Fターム[5F083ZA12]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリと独立機能ブロック (1,941) | メモリ+(ロジック、アナログ)LSI (844)

Fターム[5F083ZA12]に分類される特許

841 - 844 / 844

記憶素子、メモリ回路、半導体集積回路

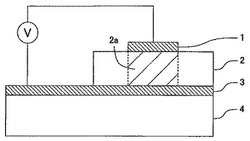

【解決手段】第1の可変抵抗(5)は、第1の端子(7)と第3の端子(9)との間に接続され、第1の端子(7)と第3の端子(9)との間に印加されるパルス電圧の極性に応じてその抵抗値を増加/減少させる。第2の可変抵抗(6)は、第3の端子(9)と第2の端子(8)との間に接続され、第3の端子(9)と第2の端子(8)との間に印加されるパルス電圧の極性に応じてその抵抗値を増加/減少させる。第1の端子(7)と第3の端子(9)との間および第3の端子(9)と第2の端子(8)との間に所定のパルス電圧を印加して第1および第2の可変抵抗(5,6)の抵抗値を可逆的に変化させることにより1ビットあるいは多ビットの情報を記録する。 (もっと読む)

他の種類の回路と共に集積されたMRAM装置

磁気抵抗ランダムアクセスメモリ(MRAM)(13)が、他の回路種(12)と共に埋め込まれている。演算装置のようなロジック(12)が、MRAM(13)と共に埋め込むのに特に適した回路種である。埋め込みを効率的に行うには、金属層(26)を他の回路(12)の相互接続部の一部として用い、更にMRAMセル(13)の一部として用いる。MRAMセル(13)は全て、プログラム線によって書き込まれる。プログラム線は、2本の線であり、交差して書き込むセルを規定する。このように、金属線(26)の共通使用があり、MRAMのプログラム線の一方に用いられ、更にロジック(12)の相互接続線の一方に用いられるので、設計が簡略化される。  (もっと読む)

(もっと読む)

3つの電気絶縁電極を有するトランジスタ及びトランジスタの形成方法

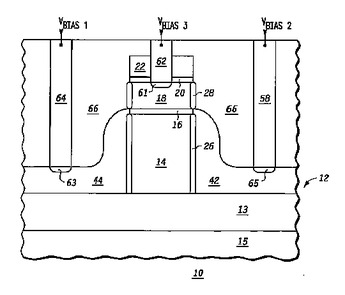

トランジスタ(10)は別々に制御することができるゲート(44,42,18)を有するように形成される。3つのゲート領域は異なる電位でバイアスすることができ、かつこれらのゲート領域は異なる伝導特性を持つことができる。チャネルサイドウォール上の誘電体はチャネル上部の上の誘電体と異ならせることができる。ソース、ドレイン、及び3つのゲートとの電気コンタクトは別々に取る。ナノクラスター(143,144)のような電荷蓄積層をトランジスタのチャネルに隣接するように設け、そして電荷蓄積層を3つのゲート領域を通して制御することにより、揮発性メモリセル及び不揮発性メモリセルの両方を同じプロセスを使用して実現することにより世界共通のメモリプロセスを提供する。揮発性セルとして用いる場合、トランジスタの高さ、及びチャネルサイドウォール誘電体の特性によって記憶保持特性を制御する。不揮発性セルとして用いる場合、トランジスタの幅、及びチャネルを覆う誘電体の特性によって記憶保持特性を制御する。  (もっと読む)

(もっと読む)

不揮発性メモリにおける基準トランジスタ用可変ゲート・バイアス

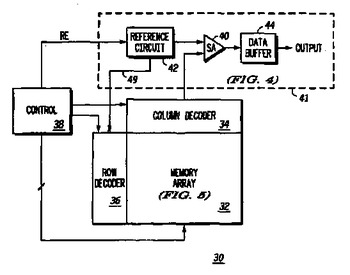

不揮発性メモリ(30)はナノクリスタルメモリセル(50、51、53)を備える。メモリセルトランジスタ(50、51、53)のプログラム及び消去閾値電圧は、プログラム/消去動作の回数の関数として上昇する。読み出し動作の間、基準トランジスタ(46)がセル電流と比較するための基準電流を供給する。基準トランジスタ(46)がナノクリスタルを含まないことを除いて、基準トランジスタ(46)は、メモリセルトランジスタ(50、51、53)を製造する際に用いるのと同様のプロセスで製造される。同様のプロセスを用いて基準トランジスタ(46)及びメモリセルトランジスタ(50、51、53)双方を製造することにより、基準トランジスタ(46)の閾値電圧は、メモリセルトランジスタ(50、51、53)の閾値電圧のずれに追従する。基準トランジスタ(46)のゲートにバイアスをかけるために、読み出し制御回路(42)が設けられている。読み出し制御回路(42)は、基準トランジスタ(46)のドレイン電流を検知し、基準電流をセル電流に対して実質的に一定値に維持するように、ゲートバイアス電圧を調節する。  (もっと読む)

(もっと読む)

841 - 844 / 844

[ Back to top ]