Fターム[5F101BD17]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | メモリセル(センサ) (3,677) | MOSトランジスタ以外のセンサ (25)

Fターム[5F101BD17]の下位に属するFターム

バイポーラトランジスタ (3)

CCD

容量、キャパシタ (16)

Fターム[5F101BD17]に分類される特許

1 - 6 / 6

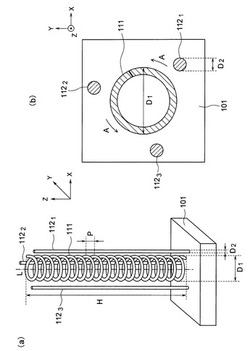

メモリ用シフトレジスタ

【課題】大容量なメモリ用シフトレジスタを提供する。

【解決手段】メモリ用シフトレジスタは、基板101と、基板101上に形成され、基板101の主面に垂直な軸Lの周りを回転する螺旋形状を有するチャネル層111とを備える。さらに、メモリ用シフトレジスタは、基板101上に形成され、軸Lに平行な方向に延びており、チャネル層111内の電荷を転送するために使用される3本以上の制御電極1121,1122,1123を備える。

(もっと読む)

半導体装置

【課題】小型化が可能な不揮発性メモリを備えた半導体装置を提供する。

【解決手段】基板901上に画素と不揮発性メモリとを備え、不揮発性メモリは、基板901上に形成される半導体活性層と、半導体活性層上に形成される絶縁膜923と、絶縁膜923上に形成されるフローティングゲイト電極907と、フローティングゲイト電極907を酸化して得られる酸化膜908,915,922と、酸化膜908,915,922に接して形成されるコントロールゲイト電極929と、を備え、画素と不揮発性メモリとは、基板901上に一体形成される。

(もっと読む)

半導体装置およびその製造方法、ならびにその半導体装置を用いた集積半導体装置および不揮発性半導体記憶装置

【課題】絶縁ゲート型電界効果トランジスタにおいて低電圧下で急峻なスイッチング特性を有する半導体素子を提供する。

【解決手段】大規模集積回路に用いられているプレーナ型のロジック回路用MOSFETにおいて、ドレイン拡散層電極のなかに、ダイオード素子と抵抗素子が並列配置されるように形成することで、低電圧であってもゲート電圧変化に対してドレイン電流が急峻な変化を示す高性能トランジスタが実現できる。

(もっと読む)

メモリーセル、及びデータ記録方法

本発明は、少なくとも一のビット・データを記憶するメモリーセル(10)に関する。当該メモリーセルは、少なくとも二つの電気的接続(40、130)と、少なくとも一のポテンシャル井戸(200)を有するバンド曲線(EL)を伴う半導体構造(11)で構成されている。供給電圧(Us=Uspeis)を二つの電気的接続へ印加することによってポテンシャル井戸が電荷担体で帯電された状態が増大し、放電電圧(Us=Usperr)を印加することによって減少するほか、維持電圧(Us=Ubei)を印加することによってこの状態が維持されて、それぞれ帯電したポテンシャル井戸の状態がメモリーセルのビット・データ片を決定する。本発明によれば、この半導体構造が空間電荷ゾーン(Wn)を有しており、ポテンシャル井戸が半導体ヘテロ接合(80)によって形成されている。この半導体ヘテロ接合と空間電荷ゾーンは、維持電圧が印加されている場合は空間電荷ゾーン内に、供給電圧が印加されている場合は空間電荷ゾーンの周縁もしくは外に、放電電圧が印加されている場合は空間電荷ゾーン内に、半導体ヘテロ接合が位置するように、空間的に相対的な配置がなされている。 (もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの占有面積を小さくした不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板と、半導体基板上に行列状に配列された複数の半導体柱と、半導体柱の間の半導体基板上に列方向に帯状に形成され、ワード線として機能する複数の第1の導電領域と、半導体柱の頂部に夫々形成された複数の第2の導電領域と、第2の導電領域を行方向に接続する複数のビット線と、半導体柱の第1と第2の導電領域との間に夫々形成され、第1と第2の導電領域に接する複数のチャネル領域と、半導体柱の間の列方向に、半導体基板上部で且つチャネル領域と対峙して絶縁的に且つ連続的に形成され、制御ゲートとして機能する複数の第3の導電領域と、第3の導電領域よりも高い位置でチャネル領域の上部に、夫々絶縁的に形成された複数の電荷蓄積領域とを具備する。

(もっと読む)

ラテラルサイリスタ及びトラッピング層を有するシリコン‐オン‐インシュレータ読み取り‐書き込み不揮発性メモリ

改善した、サイリスタに基づくメモリセルを提供する。一例では、シリコン‐オン‐インシュレータ(SOI)技術を用いて、セル(10)をフローティング基板内に形成する。セルには、第2ワードラインによりゲート駆動されるとともに完全にフローティング基板内に形成されたラテラルサイリスタ(20)を有するのが好ましい。このサイリスタのカソードは、アクセストランジスタ(18)のソースをも有し、このアクセストランジスタのドレインは装置のビットラインに接続されており、このアクセストランジスタは第1ワードライン(14)によりゲート駆動される。フローティング基板内にはトラッピング層が形成され、セルに書き込みを行う場合、パルスを加えて、論理状態“1”に対し正孔をトラッピング層にトラッピングさせ、論理状態“0”に対し電子をトラッピング層にトラッピングさせる。トラッピング層に電荷をトラッピングさせることにより、記憶されたデータ状態に追加の余裕度を加え、これらデータ状態の劣化を回避し、セルを不揮発性とする。  (もっと読む)

(もっと読む)

1 - 6 / 6

[ Back to top ]