Fターム[5F101BH16]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | 熱処理 (725)

Fターム[5F101BH16]に分類される特許

721 - 725 / 725

半導体装置及びその製造方法

【課題】リーク電流を改善した高誘電率絶縁膜を電極間絶縁膜として使用する半導体装置及びその製造方法を提供することである。

【解決手段】半導体装置は、半導体基板上に形成された第1の絶縁膜と、前記第1の絶縁膜上に形成された第1のゲート電極と、前記第1のゲート電極の上方に形成された第2のゲート電極と、前記第1のゲート電極と第2のゲート電極との間に挟まれた結晶化した第2の絶縁膜を具備することを特徴とする。

(もっと読む)

不揮発性半導体メモリ装置およびその動作方法

【課題】電源電圧相当の電圧でメモリデバイスの閾値電圧を最大限に上昇させる動作を実現する。

【解決手段】半導体基板2とゲート電極6との間に形成され電荷蓄積能力を有する積層膜5を備えるメモリトランジスタ1は、書き込み時と読み出し時とで短チャネル効果が生じているか否かの境界として見積もられるチャネル長Lminが異なり、当該異なるチャネル長Lmin(R)とLmin(W)の間に、実デバイスのチャネル長Lを有する。

(もっと読む)

半導体装置の製造方法

【課題】 マスクの枚数を増加することなく、かつ、汚染することなく膜厚の異なるゲート絶縁膜を備えた半導体装置の製造方法を提供する。

【解決手段】 メモリセル領域Mに複数のアシストゲート電極部21が互いに間隔を隔てて形成される。周辺回路領域Pでは平坦な半導体基板1の表面が露出する。次に、所定の条件のもとで、露出している半導体基板1の表面に酸化処理が施される。平坦な周辺回路領域Pに露出する半導体基板1の表面に供給される酸素ラジカルの量と比べると、メモリセル領域Mでは、アシストゲート電極部21によって挟まれていることで、露出している半導体基板1の表面にまで供給される酸素ラジカルの量は少なくなる。その結果、メモリセル領域Mに形成されるフローティングゲート酸化膜8aの膜厚は、周辺回路領域Pに形成されるゲート酸化膜10の膜厚よりも薄くなる。

(もっと読む)

重合体中のナノ結晶体を用いるフラッシュメモリ装置

【課題】本発明は、重合体薄膜中に自発形成された金属又は金属酸化物のナノ結晶体を用いた高効率かつ低費用のナノフローティングゲートを有する、フラッシュメモリ素子及びその製造方法に関する

【解決手段】

本発明は、従来のフラッシュメモリ素子のナノ結晶体の形成過程と比較し非常に簡便にナノ結晶体を形成することを可能にする。全体的に均一な分布を有する結晶体であるため、重合体層中に結晶体の凝集現象を伴わずにナノ結晶体の大きさや密度を制御することが可能となる。更に本発明は、従来のナノフローティングゲートと比較し電気的または化学的に安全性を有するナノフローティングゲートを用いることにより、高効率かつ低費用のナノフローティングゲートを有するメモリ素子及びその製造方法を提供する。

(もっと読む)

半導体装置の製造方法

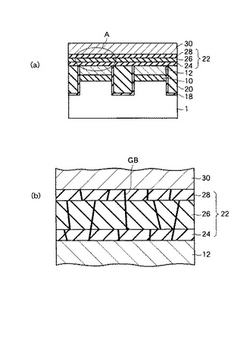

【課題】下層のポリシリコン膜を酸化させることなく、酸素アニールによりHTO膜を十分に改質させ、電気的にリークが少ないトンネル酸化膜を形成する半導体装置の製造方法を提供すること。

【解決手段】ポリシリコン膜からなる第1フローティングゲート16上に、窒化膜26又は酸窒化膜28を介してHTO膜を成膜し、酸素アニール処理を施して、トンネル酸化膜18(HTO膜)を形成する。

(もっと読む)

721 - 725 / 725

[ Back to top ]