Fターム[5F102GC01]の内容

接合型電界効果トランジスタ (42,929) | ゲート配置 (2,808) | 横型FETの上部ゲート (2,283)

Fターム[5F102GC01]に分類される特許

2,001 - 2,020 / 2,283

半導体装置とその製造方法

【課題】 従来と同程度の電極抵抗を有し、電界効果トランジスタの製造コストを低減することが可能な電界効果トランジスタおよびその製造方法を提供する。

【解決手段】 半絶縁体基板上に形成されたチャネル層と、チャネル層上に形成されたショットキー層と、ショットキー層上に形成されたオーミックコンタクト層およびショットキー層とショットキー接合するゲート電極と、オーミックコンタクト層上にオーミックコンタクト層とオーミック接合するソース電極およびドレイン電極とを備え、ソース電極、ドレイン電極およびゲート電極のそれぞれが同一の層形状をなし、ソース電極、ドレイン電極およびゲート電極の各層が同一の構成材料からなり最下層にWSiを有する第1層と、第1層の上層にTiを有する第2層と、第2層の上層にAlを有する第3層と、第3層の上層にTiを有する第4層とを有する。

(もっと読む)

半導体装置

【課題】ショットキー電極の耐湿性を向上し得る半導体装置を得る。

【解決手段】ショットキー電極であるゲート電極8は、TaNx層6とAu層7とを有している。TaNx層6は、Au層7と基板100との間で原子が拡散することを防止するための、バリアメタルとして機能する。TaNxはSiを含まないため、Siを含むWSiNよりも耐湿性が高い。そのためゲート電極8は、WSiN層を有する従来のゲート電極に比べて耐湿性が高い。また、窒素含有率xを0.8未満に設定することにより、従来のゲート電極に比べてショットキー特性が大幅に低下することを回避できる。あるいは、窒素含有率xが0.5以下の範囲内では、従来のゲート電極よりもショットキー特性を向上することができる。

(もっと読む)

III族窒化物半導体素子およびエピタキシャル基板

【課題】ショットキ電極からのリーク電流が低減されるIII族窒化物半導体素子を提供する。

【解決手段】高電子移動度トランジスタ11では、支持基体13は、具体的には、AlN、AlGaN、GaNからなる。AlYGa1−YNエピタキシャル層15は、150sec以下である(0002)面XRDの半値全幅を有する。GaNエピタキシャル層17は、窒化ガリウム支持基体とAlYGa1−YNエピタキシャル層(0<Y≦1)との間に設けられる。ショットキ電極19は、AlYGa1−YNエピタキシャル層15上に設けられる。ショットキ電極19は、高電子移動度トランジスタ11のゲート電極である。ソース電極21は、窒化ガリウムエピタキシャル層15上に設けられる。ドレイン電極23は、窒化ガリウムエピタキシャル層15上に設けられる。

(もっと読む)

III族窒化物半導体素子およびエピタキシャル基板

【課題】ショットキ電極からのリーク電流が低減されるIII族窒化物半導体素子を提供する。

【解決手段】高電子移動度トランジスタ1では、支持基体3は、AlN、AlGaN、GaNからなる。AlYGa1−YNエピタキシャル層5は、0.25nm以下の表面ラフネス(Rms)を有しており、この表面ラフネスは1μm角のエリアによって規定される。GaNエピタキシャル層7は、AlYGa1−YN支持基体3とAlYGa1−YNエピタキシャル層5との間に設けられる。ショットキ電極9は、AlYGa1−YNエピタキシャル層5上に設けられる。第1のオーミック電極11は、AlYGa1−YNエピタキシャル層5上に設けられる。第2のオーミック電極13は、AlYGa1−YNエピタキシャル層5上に設けられる。第1および第2のオーミック電極11、13の一方はソース電極であり、また他方はドレイン電極である。ショットキ電極9は、高電子移動度トランジスタ1のゲート電極である。

(もっと読む)

半導体装置及び該半導体装置を動作させる方法

本発明は、ドレイン延長部(8)を備えるラテラルDMOSTに特に関する。既知のトランジスタにおいて、更なる金属ストリップ(20)は、ゲート電極コンタクトストリップと、ソース領域コンタクト(15)に電気的に接続されているドレインコンタクト(16)との間に位置される。本特許出願において提案される装置において、更なる金属ストリップ(20)とソースコンタクト(15,12)との間の接続部は、コンデンサ(30)を有し、更なる金属ストリップ(20)は更なる金属ストリップ(20)に電圧を供給するための更なるコンタクト領域(35)を備えている。このようにして、改善された線形性が実現可能であり、当該装置の実用性が、特に、高電力及び高周波数において改善される。好ましくは、コンデンサ(30)は、単一の半導体基体(1)内にトランジスタと一体化されている。本発明は、更に、本発明による装置(10)を動作させる方法を有する。  (もっと読む)

(もっと読む)

電界効果トランジスタ及び半導体装置並びに電界効果トランジスタの製造方法

【課題】

ゲート・ドレイン間の静電容量を低減することによって、ゲインを増大させた電界効果トランジスタ及び半導体装置並びに電界効果トランジスタの製造方法を提供する。

【解決手段】

不純物の添加によりゲートが形成される第1の半導体層の上面に第2の半導体層形成する工程と、ドレイン電極が形成されるドレイン電極形成領域からゲート側に膨出させた形状に第2の半導体層をパターニングする工程と、第2の半導体層の上面に絶縁層を形成する工程と、絶縁層にドレイン電極形成用の開口を形成する工程と、この開口を介して第2の半導体層をエッチング除去する工程とにより、ドレイン電極近傍の少なくともゲート電極側に低静電容量領域を設けた電界効果トランジスタを有する半導体装置とした。

(もっと読む)

半導体装置およびその製造方法並びにその半導体装置製造用基板

【課題】 AlNバッファ層とGaN系FETの性能および信頼性との関係を明確にし、性能および信頼性の優れた半導体装置およびその製造方法並びにその半導体装置製造用基板を提供すること。

【解決手段】 基板(10)と、基板(10)上に設けられた膜厚が5から40nmの窒化アルミニウムからなるバッファ層(12)と、バッファ層(12)上に設けられた窒化ガリウム系半導体からなる動作層(20)と動作層(20)上に設けられた制御電極(26)と、を具備する半導体装置およびその製造方法並びに半導体装置製造用基板。

(もっと読む)

電子デバイス及び電力変換装置

【課題】 本発明が解決しようとする課題は主として高いコンダクタンスgmを示しながらも、ノーマリーオフの動作をするトランジスタの実現を目的とする。

【解決手段】GaN層3、AlN層9及びAlxGa1-xN(0<x<1)層4が順に密着して積層された積層構造と、前記AlxGa1-xN層4に接触する電極の組み合わせからなる電子デバイスにおいて、前記GaN及びAlxGa1-xNのxが、0<x<0.2であり、前記電極直下に相当する部分を含む部分の前記AlxGa1-xN層の厚さD、前記AlN層9の厚さdが0<D≦3nm、0<d≦0.5nmであることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 ゲート・ドレイン間の寄生容量Cgdを低下させてさらに耐圧を向上させることができる半導体装置を提供する。

【解決手段】 半導体装置100は、半導体層(1)上に設けられたゲート電極(5)と、ゲート電極(5)を挟むように半導体層(1)上に設けられたソース電極(3)およびドレイン電極(4)と、ソース電極(3)からゲート電極(5)の上方を通過してゲート電極(5)とドレイン電極(4)との間まで延在し、かつ、当該延在した領域に接合部(6a)を有するソースウォール(6)と、接合部(6a)に接合され、かつ、接合部(6a)よりもドレイン電極(4)側に延在する領域を有する電極部(8)とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】 耐圧が高く、オン抵抗が低い半導体装置およびその製造方法を提供する。

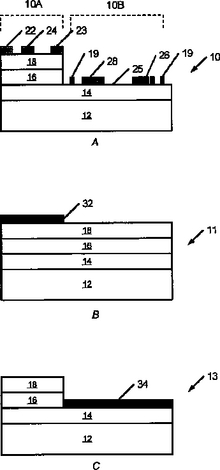

【解決手段】 基板(10)と、該基板上に形成され、SiCドリフト層(14)と、GaN系半導体層(18)と、GaN系半導体層上に形成されたソース電極(60)若しくはエミッタ電極並びにゲート電極(62)と、前記SiCドリフト層の前記GaN系半導体層と相対する面に接続されたドレイン電極(64)またはコレクタ電極と、を具備する半導体装置およびその製造方法である。SiCドリフト層を有することによりドリフト層の厚膜化が可能となりドレイン耐圧が高くできる。さらに、チャネル移動度の高いGaN系半導体層をチャネル層として用いることによりオン抵抗が低い半導体装置およびその製造方法を提供することができる。

(もっと読む)

電界効果トランジスタ

【課題】ソース−ドレイン間の電流−電圧特性におけるヒステリシス現象を防ぎ、出力電力を向上させた、GaN系化合物半導体からなる電界効果トランジスタを提供する。

【解決手段】基板1上に、GaN系化合物半導体からなるバッファ層2、電子走行層3および電子供給層4が順次積層されてなる電界効果トランジスタにおいて、前記基板1裏面側に電界発光層11を設け、前記電界発光層11からの光は基板1を透過して、前記バッファ層2、電子走行層3および電子供給層4を照射するようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】 高出力動作可能であり高周波数動作可能な半導体装置およびその製造方法を提供する。

【解決手段】 基板(10)と、基板上に形成されたGaN系半導体層(16)と、GaN系半導体層上に埋め込まれ形成されたゲート電極(18)と、ゲート電極の両側に形成されたソース電極(20)およびドレイン電極(22)と、ゲート電極とソース電極の間に形成された第1のリセス部(34)と、ゲート電極とドレイン電極の間に形成された第2のリセス部(38)と、を具備し、第1のリセス部の深さが、第2のリセス部の深さより浅いことを特徴とする半導体装置およびその製造方法である。

(もっと読む)

窒化物ベースの集積音波デバイスおよび窒化物ベースの集積音波デバイスを製造する方法

モノリシック電子デバイスは、基板と、基板上に形成された半絶縁圧電III族窒化物エピタキシャル層と、エピタキシャル層上に表面弾性波デバイスを形成する一対の入力および出力インターディジタル変換器と、基板上に形成された少なくとも1つの電子デバイス(HEMT、MESFET、JFET、MOSFET、フォトダイオード、LEDなど)とを含む。電子デバイスをSAWデバイスから、反対にSAWデバイスを電子デバイスから電気的かつ音響的に分離するための分離手段が開示される。いくつかの実施形態ではSAWデバイスと電子デバイスとの間にトレンチが形成される。さらに、その上にSAWデバイスを製造することができる半絶縁III族窒化物エピタキシャル層を形成するためのイオン注入が開示される。インターディジタル変換器に隣接した吸収および/または反射部品が、SAWデバイスの動作を妨害する可能性がある不要な反射を低減させる。  (もっと読む)

(もっと読む)

SiC基板の検査方法

【課題】 SiC基板に発生するマイクロパイプ等な貫通孔を簡便な手段で、非破壊且つ正確に検査することを可能にし、高品質のGaN系HEMTなどの製造に寄与しようとする。

【解決手段】 SiC基板21の略中央を含んで基板径の半分の径をもつ周で囲まれた真空吸引領域23を裏面側から真空吸引し、次いで、SiC基板21の表面側から水或いは水と同等の粘度をもつ液を塗布し、その液が裏面側に抜けないSiC基板を良品として選別することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 電流リークパスの形成を防止することができ半導体装置を提供する。

【解決手段】 半導体装置の製造方法は、GaN系半導体層(1)の一面にO2アッシング、有機処理またはドライエッチングのいずれかを実行する第1の工程と、GaN系半導体層(1)の一面を酸化剤および酸の混合液によりエッチングする第2の工程と、GaN系半導体層(1)の一面に電極(7,8,11)を形成する第3の工程とを含むことを特徴とする。この場合、酸化剤および酸の混合液により変質層が効率よく除去される。それにより、電流リークパスの形成が防止され、安定したオーミックコンタクトを得ることができる。その結果、耐圧低下を防止することができる。

(もっと読む)

III−V族化合物半導体製造方法

【課題】 スペーサ層を構成するAlGaAs層とGaAs層の膜厚バランスを最適にすることにより、同じキャリア濃度のドーピングでも従来技術に比べてHEMTの電子移動度を高くすることにある。

【解決手段】 HEMTのチャネル層5として混晶比yが0.15〜0.30のInyGa(1-y)As層を5〜15nmの膜厚で形成し、またスペーサ層6(又は4)にAlGaAs層6a(又は4a)とGaAs層6b(又は4b)の組み合わせを用い、そのAlGaAs層6a又は4aとして、混晶比xが0.26〜0.50のAlxGa(1-x)As層を0.1〜7.0nmの膜厚でキャリア供給層7(又は3)側に形成し、またGaAs層6b(4b)を0.1〜7.0nmの膜厚でチャネル層5側に形成し、AlGaAs層とGaAs層を合わせたスペーサ層6(又は4)の膜厚を10nmを超えない厚さとする。

(もっと読む)

半導体装置

【課題】 電極とチャネル層間のオーミック抵抗の少ない良好な高周波特性を有する半導体装置を得る。

【解決手段】 キャップ層としてのアンドープガリウム砒素(GaAs)層15a上のドレイン電極16及びソース電極17の形成位置に凹状の溝16a及び17aを設け、これらの溝16a及び17aにそれぞれドレイン電極16及びソース電極を17を形成し、それぞれの電極とチャネル層としてのn型ガリウム砒素(GaAs)層13との距離を短くする。また、ドレイン電極16及びソース電極17を、キャップ層としてのアンドープガリウム砒素(GaAs)層15aの表面に張り出すような形状に形成して、溝16a及び17aの周縁部の露出を防ぎ、この部位における表面準位の変動がチャネル層としてのn型ガリウム砒素(GaAs)層13に及ぼす影響を減らす。

(もっと読む)

改善されたフィールドプレートを備える半導体デバイス

電界効果トランジスタデバイス及び電界効果トランジスタを形成するための方法であって、当該デバイスは、半導体とオーム接触しているソース電極及びドレイン電極とを備える、電界効果トランジスタデバイス及び電界効果トランジスタを形成するための方法。ゲート電極−フィールドプレート構造は、ソース電極とドレイン電極との間に配置される。ゲート電極−フィールドプレート構造は、誘電体と、半導体とショットキー接触している第1の金属と、第2の金属とを有する。第2の金属は、第1の金属の一部の上に配置されると共に電気的に接続される第1の部分と、誘電体の一部によって第1の金属の第2の部分から分離され、且つ第1の金属のエッジを越えて、第2の金属のエッジまで延在する第2の部分とを有する。電界効果トランジスタデバイスのためのフィールドプレートを設けるために、第1の金属のエッジは、第2の金属のエッジよりもドレイン電極から離れている。 (もっと読む)

スイッチ回路装置

【課題】 HBTは、ベース−エミッタ間電流が正の温度係数を持つため、コレクタ電流も正の温度係数を持つ。従って、ベース電流を増加させて電流密度の向上を図ると、複数並列接続されたHBTの単位素子のうち、1つの単位素子に電流が集中して二次降伏を起し、破壊に至りやすくなる。

【解決手段】 HBTとFETを分離領域を介して隣接して配置し、HBTのベース電極にMESFETのソース電極を接続した単位素子を複数接続してスイッチ回路装置を構成する。単位素子を並列に複数接続したスイッチ回路装置において、単位素子毎に動作電流が不均一となっても、1つの単位素子に電流が集中することはなく二次降伏による破壊は発生しない

(もっと読む)

スイッチ回路並びに半導体装置及びその製造方法

【課題】 高調波特性および挿入損失の優れたスイッチ回路、半導体装置およびその製造方法を提供する。

【解決手段】 入力端子(70)または出力端子(72)のいずれか一方に接続され、制御端子(74)に接続されたゲート電極により、導通・非導通が制御される第1のFET(81)と、入力端子(70)または出力端子(72)のいずれか他方と第1のFET(81)との間に接続され、制御端子(74)に接続されたゲート電極により、導通・非導通が制御される第2のFET(82、83,84)とを具備し、第1のFETのゲート逆方向耐圧が第2のFETより大きい、または第1のFETのオフ容量が第2のFETより小さいスイッチ回路並びに半導体装置およびその製造方法。

(もっと読む)

2,001 - 2,020 / 2,283

[ Back to top ]