Fターム[5F102HC05]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | 拡散(固相拡散) (29)

Fターム[5F102HC05]の下位に属するFターム

横方向拡散の利用 (3)

Fターム[5F102HC05]に分類される特許

1 - 20 / 26

半導体装置および半導体装置の製造方法

【課題】ゲート電極とチャネル層との間の障壁層に低抵抗領域を備えた構成において、ゲートリーク電流を防止することによりドレイン電流の最大値の向上を図ることが可能な半導体装置を提供する。

【解決手段】化合物半導体で構成されたチャネル層14と、チャネル層14上に設けられた上部障壁層15とを備え、上部障壁層15における表面層には、不純物を含有することにより周囲よりも低抵抗に保たれた低抵抗領域15gが設けられている。また、この低抵抗領域15gを挟んだ位置において上部障壁層15に接続されたソース電極17sおよびドレイン電極17dを備えている。さらに、低抵抗領域15g上に設けられたゲート絶縁膜18と、このゲート絶縁膜18を介して低抵抗領域15g上に設けられたゲート電極19とを備えている。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】斜めイオン注入を行わなくても、外周耐圧構造を形成でき、かつ、高いドレイン耐圧が得られるようにする。

【解決手段】凹部16の底面に形成されたP型領域18と、トレンチ13内に配置されたP+型層15、および、凹部17の底面に形成されたP型領域19とによってP型リサーフ層20を構成することで電界緩和構造とする。P型リサーフ層20がトランジスタセル領域R1の周囲を囲むような構成とされることから、外周耐圧構造領域R2に延びる電界をさらにトランジスタセル領域R1の外周側に延ばすことが可能となり、ブレークダウン位置を凹部17の底面におけるN-型ドリフト層2にシフトできるため、電界緩和を行うことが可能となる。したがって、ドレイン耐圧を向上させることが可能となる。

(もっと読む)

へテロ接合電界効果型トランジスタ及びその製造方法

【課題】耐圧特性の低下やゲートリーク電流の増加を生じることなく、低抵抗で高速動作可能なヘテロ接合電界効果型トランジスタおよびその製造方法を提供する。

【解決手段】ヘテロ接合FETの製造方法に関し、(a)チャネル層3及びチャネル層3上に形成されたバリア層4を窒化物半導体層として準備する工程と、(b)窒化物半導体層上に不純物拡散源としてZnO膜9を形成する工程と、(c)ZnO膜9上のドレイン電極6及びソース電極5を形成すべき領域以外に酸化膜10を形成する工程と、(d)窒化物半導体層に対して熱処理を行い、酸化膜10が形成されていない領域の下部のチャネル層3及びバリア層4に選択的に、ZnO膜9からZn及びOを拡散させる工程とを備える。

(もっと読む)

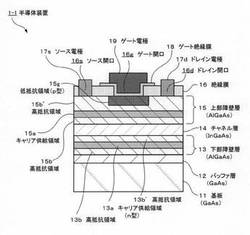

半導体装置

【課題】化合物半導体上のp型チャネルFETにおいてオン抵抗を低くすることの可能な半導体装置を提供する。

【解決手段】化合物半導体からなる基板10上に、n型チャネルFET領域2とp型チャネルFET領域3とが併設されている。p型チャネルFET領域3において、チャネル層16の下面に接するバッファ層15が、チャネル層16よりも広いバンドギャップを有する第2バッファ層15Bだけで構成された単層構造となっている。さらに、第2バッファ層15Bは、チャネル層16と電子走行層13との間に設けられている。

(もっと読む)

n型III族窒化物半導体の製造方法

【課題】Si濃度が高く、結晶性のよいn型III 族窒化物半導体を製造すること。

【解決手段】サファイア基板10上に、AlNからなるバッファ層をMOCVD法によって形成し、さらにバッファ層上にノンドープのGaNからなる第1層11をMOCVD法によって1140℃で2μm形成した(図1(a))。次に、第1層11上に、SiO2 からなる第2層12を、プラズマCVD法によって200nm形成した(図1(b))。次に、BHF(バッファードフッ酸)によって第2層12を除去した(図1(c))。次に、第2層12が除去された第1層11上に、n型ドーパントガスを供給せずにGaNをMOCVD法によって1140℃で50nm成長させた。これにより、第1層11上には、Siが高濃度にドープされ、結晶性が良好なn型GaNからなる第3層13が形成された(図1(d))。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】本発明は、耐圧特性を維持したままアクセス抵抗を低減して高速動作が可能な窒化物半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明による窒化物半導体装置は、窒化物半導体を用いたヘテロ接合電界効果型の半導体装置であって、基板1上に順次積層して形成されたチャネル層3およびバリア層4と、バリア層4上に離間して形成されたソース電極5およびドレイン電極6とを備え、ソース電極5およびドレイン電極6のそれぞれの下方であり、かつ、バリア層4の表面からチャネル層3の少なくとも一部までの領域に対して、不純物拡散を行うことによって不純物拡散領域22を設け、バンドギャップを変化させることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板上に閾値電圧が異なる2種類以上の電界効果トランジスタを集積した半導体装置であって、閾値電圧の制御性が良い電界効果トランジスタを集積した半導体装置とその製造方法とを提供することを目的とする。

【解決手段】閾値電圧が異なるE−FETとD−FETとが基板301上に形成された半導体装置30であって、基板301と、E−FETとD−FETとのそれぞれのチャネルとして機能する、基板301の上層に形成されたチャネル層303と、チャネル層303の上層に形成され、チャネル層303に電子を供給するためにドナーとなる不純物を含む、AlGaAsからなる電子供給層305とを備え、電子供給層305の領域のうちE−FETとD−FETとの少なくとも一方の領域は、さらに、フッ素原子を含む。

(もっと読む)

ヘテロ接合電界効果トランジスタおよびその製造方法

【課題】ソース電極およびドレイン電極のn+層領域と2DEGチャネルとの接触抵抗を低減したヘテロ接合電界効果トランジスタを提供する。

【解決手段】基板上に設けられた電子走行層と、電子走行層の上に設けられた電子供給層と、ソース電極およびドレイン電極のそれぞれに対応して電子供給層に設けられたトレンチと、を有し、トレンチの底面が電子走行層と電子供給層の界面であるヘテロ接合から所定の距離だけ離れている構成である。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体ウエハ面内におけるゲート形成領域の開口部のエッチング深さを均一化して所望の閾値電圧を得ることができ、併せて歩留を向上した半導体装置及びその製造方法を提供する。

【解決手段】本発明は、半絶縁性基板上に、バッファ層と、チャネル層と、p型不純物が拡散される拡散層と、前記拡散層よりもエッチングレートが大きい被エッチング層を順次エピタキシャル成長して積層するステップと、前記被エッチング層よりもエッチングレートが大きい絶縁層を前記被エッチング層上に設けるステップと、エッチングレートの違いを利用して、前記絶縁膜に開口部を設け、さらに、前記開口部を介して前記被エッチング層を選択的にエッチング除去するステップと、前記開口部から前記拡散層に前記p型不純物を拡散してゲート領域を形成するステップと、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】同一基板上にE−FETとD−FETとが集積化された半導体装置におけるソース−ドレイン間のオン抵抗の低減を目的とする。

【解決手段】同一の半導体基板10上にE−FETとD−FETとが集積化された半導体装置1であって、複数のエピタキシャル層11は、半導体基板10側から順に、E−FETとD−FETとのゲートの閾値電圧を調整する第1の閾値調整層115と、最上層から当接する上層までの選択エッチングを停止させる第1のエッチング停止層116と、D−FETのゲートの閾値電圧を調整する第2の閾値調整層117と、最上層から当接する上層までの選択エッチングを停止させる第2のエッチング停止層118とを備え、第1のエッチング停止層116および第2の閾値調整層117のうち少なくとも一方は、n型のドーピングがなされている領域を含む。

(もっと読む)

窒化物半導体トランジスタとその製造方法

【課題】電流コラプスの発生を抑制するとともに、ノーマリーオフ型の窒化物半導体トランジスタを実現する。

【解決手段】半導体トランジスタは、基板501、バッファ層502、第1窒化物半導体層503、第2窒化物半導体層504、p型窒化物半導体層506、ソース電極508、ドレイン電極509およびゲート電極510を備えている。第2窒化物半導体層504のうちp型窒化物半導体層506の下に位置する部分には、p型ドーパントを含むドーパント層511が形成されている。

(もっと読む)

スイッチ素子および電子機器

【課題】IMDや高調波歪の少ないスイッチ素子を提供する。

【解決手段】シャント回路に直列挿入されたシャントFET1Aと、シリーズ回路に直列挿入されたシリーズFET1Bとを備える。シャントFET1Aは、コンタクト層17内のゲート領域34上にゲート電極30を有し、コンタクト層17上のゲート電極30の両側にソース電極31およびドレイン電極32を有し、ゲート領域34の両側に一対のリセス35を有する。シリーズFET1Bは、コンタクト層17内のリセス40の底部に形成されたゲート領域45上にゲート電極41を有し、コンタクト層17上のリセス40の両側にソース電極42およびドレイン電極43を有する。

(もっと読む)

半導体装置およびこれを用いた電力変換装置

【課題】電力変換装置のスイッチング素子を小型化する。

【解決手段】同一の半導体チップ30内に、ダイオードおよび高電子移動度トランジスタを内蔵する半導体装置であって、ダイオードが有する半導体基板20の主面(第1主面)20a上に高電子移動度トランジスタが有する化合物半導体層10を形成し、ダイオードのアノード電極26は、化合物半導体層10の主面10aから半導体基板20の主面20aのアノード領域であるp+領域23に達するビアホール(孔)25に埋め込まれた導電体を通じてアノード領域に電気的に接続するように構成するものである。

(もっと読む)

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置であって、半導体装置は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN2とを有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電位ノードNL1に結合される第3ノードN3を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第3ノードN3から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】拡散深さとトレンチ深さを最適な値に自由に設定することの可能な化合物半導体装置を提供する。

【解決手段】チャネル層15とゲート電極22との間に、As系III−V族化合物半導体からなるスペーサ層18、P系III−V族化合物半導体からなる第1挿入層19、As系III−V族化合物半導体からなるゲート形成層20、およびP系III−V族化合物半導体からなる第2挿入層21がチャネル層15側からこの順に設けられている。また、ゲート領域26の上面がゲート形成層20の上面に、ゲート領域26の下面がスペーサ層18の上面およびその近傍に、リセス27の下面が第1挿入層19の上面およびその近傍にそれぞれ位置している。

(もっと読む)

接合型FETおよびその製造方法

【課題】 従来の接合型FETにおいては、チャネル領域をエピタキシャル層で形成するため、浅いチャネル領域が形成できず、高周波特性の改善に限界があった。また分離領域とチャネル領域のpn接合の不純物濃度差が大きく、リーク電流が低減できなかった。またチャネル領域が深いためゲート領域もイオン注入および拡散で深く形成する必要があり、内部抵抗も高く、ノイズ特性の改善が図れなかった。

【解決手段】 浅いチャネル領域をイオン注入および拡散で選択的に形成する。チャネル領域が比較的低濃度のp型半導体層とpn接合を形成するので、接合容量の低減による高周波特性の改善とリーク電流の低減が実現できる。またゲート領域もイオン注入により浅く形成できるので、内部抵抗の低減によるノイズ低減が図れる。

(もっと読む)

III族窒化物系化合物半導体素子の製造方法

【課題】下層からのマグネシウムの拡散を利用した電界効果トランジスタの製造。

【解決手段】マスク層2mでp型層1pの表面の一部を覆い、Mg原料を導入せずにGaN層を形成するべくエピタキシャル成長を行うと、下層のp型層1pに接触する部分においては、当該p型層1pからMgが拡散してpボディ層4pが形成され、マスク層2mの上部は、アンドープGaNから成るチャネル形成層4iが形成される。同様に、pボディ層4pの上部には、pボディ層4pからMgが拡散してp−AlGaN層5pが形成され、チャネル形成層4iの上部には、アンドープAlGaN層5iが形成される。このようにして製造されたHEMT100は、ボディ電極Bdの形成されるp−AlGaN層5p表面がエッチング処理されていないのでオーミック性が良好であり、ボディ電極Bdからチャネル形成層4iの電位を安定して保つことができ、素子特性の安定した素子となる。

(もっと読む)

能動素子およびスイッチ回路装置

【課題】 HBTでは、ベース電流を増加させて電流密度の向上を図ると、二次降伏を起し、破壊に至りやすくなる。

【解決手段】 単位HBTと単位FETを分離領域を介して隣接して配置し、単位HBTのベース電極に単位FETのソース電極を接続した単位素子を複数接続して能動素子を構成する。これにより、単位素子に電流が集中した場合であっても二次降伏による破壊が発生しない能動素子を実現できる。また単位FETでは耐圧を確保するため埋め込みゲート電極構造を採用するが、埋め込み部をInGaP層に拡散させない構造とすることによりPtの異常拡散を防止できる。更に、単位HBTのエミッタメサ、ベースメサ形成、レッジ形成および単位FETのゲートリセスエッチングに選択エッチングを採用でき、再現性が良好となる。

(もっと読む)

電界効果トランジスタ及びこの電界効果トランジスタを備えた半導体装置並びに半導体装置の製造方法

【課題】チップサイズの増大を招くことなく、ゲート−ドレイン間寄生容量を低減させる電界効果トランジスタ、及びこの電界効果トランジスタを備えた半導体装置、並びに半導体装置の製造方法を提供する。

【解決手段】半絶縁性基板上にエピタキシャル成長によって形成したチャネル層と、このチャネル層上にエピタキシャル成長によって形成したスペーサー層と、このスペーサー層上にエピタキシャル成長によって形成したドーピング層と、このドーピング層上にエピタキシャル成長によって形成した障壁層とからなる半導体層を有し、かつ、この半導体層の障壁層上に形成したソース電極と、ドレイン電極と、ゲート電極とを有し、ゲート電極の下側の障壁層に不純物をドーピングした埋込みゲート領域を有する電界効果トランジスタにおいて、ゲート電極とドレイン電極との間における障壁層に凹形状のスリットを設ける。

(もっと読む)

スイッチ集積回路装置およびその製造方法

【課題】高周波スイッチMMICにおいてD型HEMTとE型HEMTを同一基板に形成し、D型HEMTのゲート電極をInGaP層にPtを埋め込んだ埋め込みゲート構造とする場合、埋め込まれたPtがInGaP層表面において横方向に異常拡散するため耐圧が低くなるという問題があった。

【解決手段】AlGaAs層とInGaP層を繰り返し積層した第1〜第3ノンドープ層と安定層を有するエピタキシャル構造とし、D型HEMTの第2ゲート電極を第3ノンドープ層(AlGaAs層)上に設け、E型HEMTの第1ゲート電極を第1ノンドープ層上に設ける。第2ゲート電極をPt埋め込みゲート構造とし、埋め込まれたPtの底部を第3ノンドープ層中に留まらせ、InGaP層(第2ノンドープ層)にPtが達しないようにする。これによりInGaP層表面におけるPtの横方向異常拡散を防止し、大幅に耐圧を向上させることができる。

(もっと読む)

1 - 20 / 26

[ Back to top ]