Fターム[5F110EE22]の内容

Fターム[5F110EE22]の下位に属するFターム

テーパ状 (986)

Fターム[5F110EE22]に分類される特許

861 - 866 / 866

フィン型電界効果トランジスタを有する半導体装置

n型電界効果トランジスタおよびp型電界効果トランジスタとを含む半導体装置であって、n型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{100}面であり、p型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{110}面である、という条件を満足する半導体装置とする。 (もっと読む)

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上面から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在する絶縁膜と、ソース/ドレイン領域とを有するMIS型電界効果トランジスタを備えた半導体装置であって、1つのチップ内に、前記MIS型電界効果トランジスタとして、ゲート電極下の前記半導体凸部における基板平面に平行かつチャネル長方向に垂直な方向の幅Wが互いに異なる複数種のトランジスタを有する半導体装置。 (もっと読む)

線状素子

柔軟性、可撓性があり任意の形状に集積回路を作成できるという特徴を持つ線状MISFETでは、ソース領域とドレイン領域を並列配置する構造が使用されていた。しかし、MISFETの電気特性を決めるチャネル長が円筒形のゲート絶縁領域に沿ったソース領域とドレイン領域の距離できまるため、チャネル長の微細化や再現性向上が困難だった。 MISFETの構造を、ソース領域とドレイン領域でチャネル領域となる半導体領域を挟む構造とした。半導体領域にゲート絶縁領域を介して制御電圧を加え、ソース領域とドレイン領域間で流れる電流を制御する。チャネル長が、半導体領域の膜厚で決まるため、チャネル長の微細化や再現性向上が可能になった。 (もっと読む)

半導体デバイスおよびその製造方法

集積回路での使用に適した歪み半導体デバイスおよび歪み半導体デバイスの製造方法。半導体−オン−インシュレータ基板からメサ分離構造が形成される。このメサ分離構造にゲート構造が形成される。このゲート構造は、ゲート絶縁材料に配置されたゲートと、対向する2組の側壁を有する。ゲート構造の対向する第1の組の側壁に隣接するメサ分離構造の一部に、半導体材料が選択的に成長され、ドープが行われる。ドープされた半導体材料がシリサイド化されて、絶縁材料によって保護される。ゲートがシリサイド化され、このシリサイドが、対向する第2の組の側壁を覆っており、チャネル領域に応力を付与する。  (もっと読む)

(もっと読む)

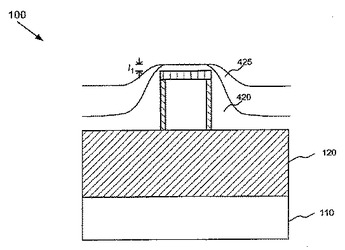

化学機械研磨プレーナ化のためのデュアルシリコンゲート層を有するFINFET

FinFETタイプの半導体デバイスは、フィン構造(210)を含んでいる。この上には、比較的薄いアモルファスシリコン層(420)を形成し、それから非ドープポリシリコン層(425)を形成する。この半導体デバイスは、アモルファスシリコン層(420)がフィン構造の損傷を防ぐ停止層として働く化学機械研磨(CMP)を使用してプレーナ化することができる。  (もっと読む)

(もっと読む)

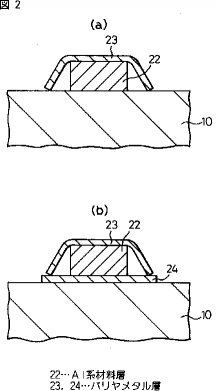

積層金属配線及び薄膜トランジスタ基板、並びにそれらの製造方法

【課題】 IC等の半導体装置や、表示装置に用いられるTFT基板で使用される、Alを含む積層配線の信頼性を高める。

【解決手段】 上層の金属層22を下層のAl又はAlを含む合金材料層21の露出した側壁を少なくとも部分的に隠蔽するよう下方に湾曲させる。この積層配線は、エッチングによりこれを作製する際に、上層の金属層22よりも下層のAl又はAlを含む合金の材料層21の方のエッチング速度を大きくして、Al又はAlを含む合金の材料層21のサイドエッチングを多くし、上層の金属層22を下層のアルミニウム又はアルミニウムを含む合金材料層21の露出した側壁を少なくとも部分的に隠蔽するよう下方に湾曲させることで作製できる。

(もっと読む)

861 - 866 / 866

[ Back to top ]