Fターム[5F110EE36]の内容

Fターム[5F110EE36]に分類される特許

61 - 80 / 96

電気光学装置用基板及び電気光学装置、並びに電子機器

【課題】画素の積層構造の単純化を図りつつ、トランジスタのオン電流を増加させる。

【解決手段】電気光学装置は、半導体層1aよりも上層側に配置され、チャネル領域1a’に重なると共に走査線11aに電気的に接続された第1ゲート電極3aと、半導体層1aよりも下層側に配置され、チャネル領域1a’に重なると共に走査線11aに電気的に接続された第2ゲート電極3bとを有するTFT30と、第2ゲート電極3bと同層に配置されるデータ線6aとを備える。

(もっと読む)

有機薄膜トランジスタ及びそれを用いた集積回路

【課題】ゲート電極への配線における断線等を生じることなく、ゲート電極の厚みを厚くすることができる有機薄膜トランジスタ及びそれを用いた集積回路を得る。

【解決手段】基板と、基板上に設けられるゲート電極と、ソース電極と、ドレイン電極と、ゲート電極上を覆うゲート絶縁膜と、ゲート絶縁膜の上に設けられ、ソース電極とドレイン電極の間でチャネル領域を形成するための有機半導体層と、ゲート電極に信号を与えるための信号線とを備える有機薄膜トランジスタであって、ゲート電極より厚みの薄い接続層が基板上に設けられており、ゲート電極の一部が接続層の上に形成されることにより、ゲート電極が接続層に電気的に接続されており、信号線が接続層と電気的に接続されることにより、接続層を介してゲート電極と電気的に接続されていることを特徴とする有機薄膜トランジスタ。

(もっと読む)

コンタクトホールの形成方法、配線基板の製造方法、半導体装置の製造方法および電気光学装置の製造方法

【課題】針などを用いた物理的なコンタクトホールの形成において導通不良の生じ難いコンタクトホールの形成方法(半導体装置の製造方法)を提供する。

【解決手段】基板10上に電極又は配線としてパターン化された導電性膜12cを形成する工程と、基板10及び導電性膜12c上に有機絶縁膜14を形成する工程と、導電性膜12c上に有機絶縁膜14を通過して、内部に空洞を有する中空針100を当接させる工程と、空洞内を減圧状態とすることにより、空洞内の有機絶縁膜14を吸引する工程とによりコンタクトホールを形成する。かかる方法によれば、空洞内の有機絶縁膜14が吸引され、コンタクトホール底部の絶縁膜残渣を低減することができる。よって、導通不良を低減できる。

(もっと読む)

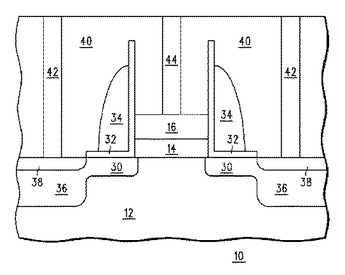

金属電極を有する半導体素子の形成、及び半導体素子の構造

半導体素子(10)を形成する方法は、ゲート誘電体(14)を基板(12)の上に形成する工程と、金属電極(16)をゲート誘電体(14)の上に形成する工程と、ポリシリコンまたは金属を含む第1犠牲層(18)を金属電極の上に形成する工程と、第1犠牲層(17)を除去する工程と、そしてゲート電極コンタクト(44)を金属電極(16)の上に位置し、かつ金属電極(16)に接続されるように形成する工程と、を含む。  (もっと読む)

(もっと読む)

コンタクトホールの形成方法、これを用いた回路基板及び半導体装置の製造方法

【課題】針などを用いた物理的なコンタクトホールの形成において導通不良の生じ難いコンタクトホールの形成方法、この方法を使用した回路基板、半導体装置の製造方法を提供する。

【解決手段】基板上に電極又は配線としてパターン化された第1の導電層を形成する第1工程と、基板及び第1の導電層上に絶縁層を形成する第2工程と、電極又は配線上の絶縁層に対して当該絶縁層の面から上方に5度乃至80度の範囲内の角度で切削具を挿入する第3工程と、切削具を上記絶縁層から引き抜いて当該絶縁層に電極又は配線に至る傾斜した開口部を形成する第4工程と、を含む。

(もっと読む)

液晶表示装置の製造方法

【課題】接触孔形成のためのエッチング工程進行時に、ゲート線の端部、データ線の端部及びドレーン電極の表面が損傷及び逆テーパ構造となることを防止し、液晶表示装置の電気的特性及び信頼性を向上する製造方法の提供。

【解決手段】データパターン、半導体の突出部及び非晶質シリコンパターンを形成する前に、ゲート線端部、維持電極固定端付近の維持電極線131、維持電極の自由端の直線部分上に存在するゲート絶縁膜140を部分的に除去する。これによって、ゲート線端部、維持電極固定端の付近の維持電極線及び維持電極133a,133bの自由端の直線部分とデータ線171端部とドレーン電極175上には共通的に保護膜180が存在するので、以降のエッチング工程によって形成される接触孔を介してゲート線の端部、データ線の端部及びドレーン電極が露出される時間が殆ど同じである。従って、電極表面の損傷及び接触孔の逆テーパ構造を防止できる。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗の問題が生じることのないソース・ドレイン領域を有する。

【解決手段】半導体装置25は、半導体基板10上に一定間隔で列状に形成された多数のMOSFET用の複数の柱状ゲート電極16と、複数の柱状ゲート電極16のうちの隣接する2つの柱状ゲート電極間の一部分に形成されるMOSFETのチャネルに相当する半導体領域19と、を備える。この半導体装置の製造方法は、半導体基板を含む基層10〜12の表面に複数の穴14を列状に形成し、これら列状の複数の穴14に半導体を埋め込んで柱状ゲート電極16を列状に複数形成し、ゲート電極16の少なくとも一部を露出させて半導体基板10,11の表面に複数の柱状ゲート電極16を露出させ、隣接する2つの前記柱ゲート電極の離隔する距離の半分の長さよりも厚い絶縁物からなるゲート側壁膜17を成膜し、列状で複数の柱状ゲート電極16の上端を平坦面としてから金属膜により橋絡して第2ゲート電極23を形成し、ゲート電極を製造する。

(もっと読む)

電気光学装置の製造方法、電気光学装置、及び電子機器

【課題】コンタクトホールの形成工程を省略し、製造プロセスの簡素化を実現して生産効率の向上を図る。

【解決手段】TFT基板10上にTFT30を構成するゲート電極3aを形成する第1配線膜形成工程(a)と、ゲート電極3aを被覆する下層絶縁膜41aを成膜する絶縁膜成膜工程(b)と、ゲート電極3aに対して電気的に接続される走査線11aを下層絶縁膜41a上に形成する第2配線膜形成工程(c)とを有し、絶縁膜成膜工程では、ゲート電極3aと走査線11aとを直接接続するための非成膜領域41aaを有する下層絶縁膜41aを成膜する。

(もっと読む)

データ記憶回路用非対称性トランジスタ

ソース(30)の抵抗がドレイン(40)よりも高いトランジスタ(22)は、記憶回路(10)におけるプル・アップ素子(20)として最適である。トランジスタは、ソース抵抗を有するソース注入を備えたソース領域を有している。ソース領域はサリサイド化されない。トランジスタの電気伝導を制御するため、制御電極領域(50)がソース領域に隣接している。ドレイン領域(40)は、制御電極領域に隣接すると共に、ソース領域とは反対側に設けられている。ドレイン領域は、ドレイン抵抗を有しサリサイド化されたドレイン注入を有している。ソース領域の物理特性はドレイン領域とは異なるため、ソース抵抗はドレイン抵抗よりも高くなっている。  (もっと読む)

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制できる構造であり、しきい値電圧を制御でき、電流駆動力に優れ、高速動作が可能なマルチフィンFETを有する半導体装置を提供することである。

【解決手段】上記の課題を解決した半導体装置の1態様は、半導体基板上に設けられたソース領域及びドレイン領域と、前記ソース領域及びドレイン領域を接続する複数のフィンと、前記半導体基板の上方に設けられ、前記各フィンを覆って設けられたゲート電極と、前記ソース領域若しくはドレイン領域から前記ゲート電極に向けて張り出し、隣接するフィンに接続して形成された張出し領域と、前記ゲート電極に接続する複数のパッド電極と、前記複数のパッド電極を接続する配線とを具備する。

(もっと読む)

半導体装置、電気光学装置、電子機器及び半導体装置の製造方法

【課題】使用するアクティブマトリクス方式の表示器に使用される有機半導体装置においてゲート駆動信号を伝搬するゲート線(ゲート信号線)の抵抗値を下げることを可能とした半導体装置、電気光学置及び電子機器を提供する。

【解決手段】基板上(101)に形成された有機半導体トランジスタと、有機半導体トランジスタのソース又はドレイン電極(105)と接続されるデータ線(107)と、データ線と交差するように配置されて有機半導体トランジスタのゲート電極(110)に接続されるゲート線と、を備え、ゲート線は、ゲート電極(110a)、ゲート電極に信号を伝搬する第1のゲート線(102)、及びデータ線と層間絶縁層(109)を介して交差する第2のゲート線(110b)を含み、上記ゲート電極、上記第1及び第2のゲート線は互いに直列に接続され、第1のゲート線(102)の導電率がゲート電極(110a)及び第2のゲート線(110b)の導電率よりも高い、ことを特徴とする。

(もっと読む)

デュアル配線型集積回路チップ

【課題】 デュアル配線型集積回路チップ及びその製造方法を提供する。

【解決手段】 両面に配線レベルを有する半導体デバイス、及び、両面のデバイス及び配線レベルへのコンタクトを有する半導体構造体を製造する方法を提供する。本方法は、シリコン・オン・インシュレータ基板上のデバイスへの第1コンタクトと、第1コンタクトへの第1側面上の配線レベルとを有するデバイスを製造するステップと、下部シリコン層を除去して埋込み酸化物層を露出させるステップと、埋込み酸化物層を貫通してデバイスへの第2コンタクトを形成するステップと、埋込み酸化物層の上に第2コンタクトへの配線レベルを形成するステップとを含む。

(もっと読む)

ダイナミックアレイ・アーキテクチャ

基板と、前記基板内で定義付けされた多数の拡散領域とを含む半導体装置。前記拡散領域は、前記基板の非活性領域によってお互いに分離されている。前記半導体装置は、前記基板の上を1つの共通方向に伸びるように定義付けされた多数の線形ゲート電極トラックを含む。線形ゲート電極トラックのそれぞれは、1つ以上の線形ゲート電極セグメントによって定義付けされている。前記基板の拡散領域と非活性領域の両方の上を伸びる線形ゲート電極トラックのそれぞれは、前記隣接する線形ゲート電極セグメント間の適切な電気的絶縁を確実にしつつ、前記線形ゲート電極トラック内の隣接する線形ゲート電極セグメントの終端間の分離距離を最小化するように定義付けされている。 (もっと読む)

半導体装置及びその製造方法

【課題】本発明は、配線パターンがプラズマ処理により形成される半導体装置及びその製造方法に関し、プラズマ処理によるゲート酸化膜の破損を防止することを課題とする。

【解決手段】半導体基板11に、回路形成領域Aに対応する半導体層16と、回路形成領域Aを囲むように設けられた非形成領域Bに対応する半導体層16とを電気的に分離する絶縁部材18を設け、絶縁部材18が設けられた半導体基板11の回路形成領域Aに複数の半導体集積回路12を形成した。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】Fin型トランジスタの金属ゲート電極を高抵抗化させることなく、トランジスタを正常に動作させることができる半導体装置を提供する。

【解決手段】半導体装置の製造方法は、半導体材料から成り、上面が保護膜40で被覆されたFin30を絶縁層20上に形成し、Finの側面にゲート絶縁膜50を形成し、Finを被覆するようにゲート電極材料60を堆積し、ゲート電極材料を平坦化し、ゲート電極材料を加工することによってゲート電極62を形成し、ゲート電極を被覆するように層間絶縁膜90を堆積し、ゲート電極の上面を露出させ、ゲート電極の上面上に金属110を堆積し、ゲート電極と金属とを反応させることによってゲート電極をシリサイド化し、金属のうち未反応の金属を除去することによって、保護膜の上面上に溝115が形成され、溝に導電体120を充填することを具備する。

(もっと読む)

アクティブマトリックス基板

【課題】断線不良の発生や実装時の接続不良の発生を抑制し、信頼性が高く高歩留まりで製造可能なアクティブマトリックス基板を提供する。

【解決手段】アクティブマトリックス基板100は、絶縁性基板1上に、ゲート電極2aを形成する第1の金属膜と、ゲート電極2aを覆う第1の層間絶縁膜4と、半導体膜5と、ソース電極8、ドレイン電極9及びソース電極8に表示信号を供給するソース配線7を形成する第2の金属膜と、第2の層間絶縁膜11と、第2の層間絶縁膜11に形成されたコンタクトホール12を介してソース電極8に接続される画素電極13とを層状に形成した画素表示領域27を少なくとも備える。さらに、表示信号入力を行うためにソース配線7を画素表示領域27から引き出すソース引き出し配線18を備え、ソース引き出し配線18は、ゲート電極2aを形成する前記第1の金属膜と同一の層に形成されている。

(もっと読む)

転写元基板、転写元基板の製造方法、及び半導体装置の製造方法

【課題】薄膜半導体の剥離転写技術を用いた半導体装置の製造において、転写用基板上に形成された複数の転写薄膜回路の良不良を転写前に予め検査することを可能とした薄膜半導体装置の製造方法を提供する。

【解決手段】本発明の転写元基板は、基板100と、この基板上に剥離層101を介して形成された転写対象となる複数の薄膜回路102と、上記基板上に形成された、回路動作を検査する検査回路11〜13と、各薄膜回路102と上記検査回路11〜13とを接続する配線と、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 電界効果型トランジスタが形成される半導体層の結晶性の劣化を抑制しつつ、バックゲート電極によるしきい値制御性を向上させる。

【解決手段】 単結晶半導体基板11上には埋め込み酸化膜12が形成され、埋め込み酸化膜12上には、バックゲート電極を構成する第1単結晶半導体層13が形成されている。さらに、第1単結晶半導体層13上には埋め込み酸化膜14が形成され、埋め込み酸化膜14上には、メサ分離された第2単結晶半導体層15a、15bが積層され、埋め込み酸化膜12の膜厚TBOX1は埋め込み酸化膜14の膜厚TBOX2よりも厚くするとともに、第2単結晶半導体層15a、15bにSOIトランジスタを形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 しきい値制御性を向上させつつ、絶縁体上に配置された電界効果型トランジスタ下にフィールドプレート電極を形成する。

【解決手段】 半導体基板1上には絶縁層2が形成され、絶縁層2には、単結晶半導体層3a、3bが積層され、単結晶半導体層3a、3b上には、メサ分離された単結晶半導体層5a、5bが絶縁層4を介してそれぞれ積層され、単結晶半導体層5a、5bには、Pチャンネル電界効果型トランジスタおよびNチャンネル電界効果型トランジスタを形成するとともに、単結晶半導体層3a、3bをフールドプレートとして機能させるとともに、不純物の極性または濃度が互いに異なるように構成する。

(もっと読む)

パターン配線、およびパターン配線の形成方法、並びに電気光学装置、電子機器

【課題】 所定領域内における膜厚分布の均一性が良好なパターン配線、およびその形成方法、並びに、当該パターン配線を備える電気光学装置、電子機器を提供すること。

【解決手段】 下層バンク10で区画された区画領域内に、機能液50を充填し、乾燥工程を経て成膜を行う。主配線部領域40と電極部領域41との接続領域42は、電極部領域41の幅よりも狭く形成されており、この接続領域42における毛細管現象によって、電極部領域41内における機能液50の液位が均一化される。

(もっと読む)

61 - 80 / 96

[ Back to top ]