Fターム[5F110NN75]の内容

Fターム[5F110NN75]に分類される特許

1 - 6 / 6

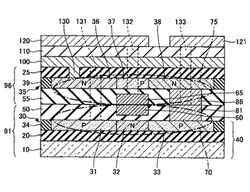

積層型半導体装置及びその製造方法

【課題】本発明は、接続電極のピッチを大きくせずにゲートの寄生容量を小さくすることができ、回路の高速化と層間接続の高密度化の両立が図れる積層型半導体装置及びその製造方法を提供することを目的とする。

【解決手段】第1のゲート60と、該第1のゲートよりも下層に形成された第1及び第2の不純物拡散領域31、33とを有する第1の半導体素子70と、

前記第1のゲートと対向して接合された第2のゲート65と、該第2のゲートよりも上層に形成された第3及び第4の不純物拡散領域36、38とを有する第2の半導体素子75と、を有することを特徴とする。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】重畳する第1のトランジスタおよび第2のトランジスタからなる第1のインバータと、重畳する第3のトランジスタおよび第4のトランジスタからなる第2のインバータと、第1の選択トランジスタと、第2の選択トランジスタと、を有し、第1のインバータの出力端子、第2のインバータの入力端子および第1の選択トランジスタのソースおよびドレインの一方が接続され、第2のインバータの出力端子、第1のインバータの入力端子および第2の選択トランジスタのソースおよびドレインの一方が接続されることによって、微細化したSRAM回路を形成する。

(もっと読む)

半導体装置

【課題】 小型であり、順方向と逆方向の双方で導通可能(スイッチング可能)な半導体装置を提供する。

【解決手段】 第1導電型の第1領域30と、第2導電型であり、第1領域30に接している第2領域32と、第1導電型であり、第2領域32によって第1領域から分離されている第3領域36と、第2導電型であり、第3領域36によって第2領域32から分離されている第4領域22と、第1導電型であり、第4領域22によって第3領域36から分離されている第5領域20と、第1領域30及び第2領域34と導通している第1電極56と、第4領域22及び第5領域20と導通している第2電極54と、第2領域32に対して絶縁膜42を介して対向している第1ゲート電極44と、第4領域22に対して絶縁膜50を介して対向している第2ゲート電極52を備えていることを特徴とする半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】MIS−HEMTにおいて、閾値電圧の低下を抑制する。

【解決手段】半導体装置は、基板19と、この基板上に形成されており、電子走行層13及び電子供給層15が順次積層されて形成された積層構造体17とを含む下地11を具えている。この下地の下地面には、互いに離間し、かつ対向して第1及び第2主電極が形成されている。そして、下地面11aの、これら第1主電極41a及び第2主電極41b間に挟まれた領域内に、ゲート形成用凹部27が形成されている。更に、半導体装置はゲート絶縁膜29を具えている。そして、このゲート絶縁膜は、最小でも2.9g/cm3の結晶密度で形成されている。また、半導体装置は、ゲート絶縁膜が形成された前記ゲート形成用凹部を埋め込むゲート電極43を具えている。

(もっと読む)

ハイブリッド配向トランジスタにおける帯電損傷からの保護

【課題】 帯電損傷からHOT回路内のデバイスを保護するための新しい保護スキームを提供すること。

【解決手段】 チップが、半導体基板(5)の下にあるバルク領域(18)と導電的に連通している基板の第1の領域(24)内に配置されたバルク・デバイス(20)を有するCMOS構造体を含み、第1の領域(24)及びバルク領域(20)は、第1の結晶配向を有する。SOIデバイス(10)は、埋込み誘電体層(16)によって基板のバルク領域から分離された半導体オン・インシュレータ(「SOI」)層(14)内に配置され、SOI層は、第1の結晶配向とは異なる結晶配向を有する。一例において、バルク・デバイスは、p型電界効果トランジスタ(「PFET」)を含み、SOIデバイスは、n型電界効果トランジスタ(「NFET」)デバイスを含む。代替的に、バルク・デバイスはNFETを含むことができ、SOIデバイスはPFETを含むことができる。SOIデバイスがバルク・デバイスのゲート導体(21)と導電的に連通しているゲート導体(11)を有するとき、バルク領域と逆バイアスがかかった状態で導電的に連通しているダイオードの存在を除いて、SOIデバイスに帯電損傷が生じることがある。ダイオードは、ゲート導体上の電圧、或いはSOIデバイスのソース又はドレイン領域上の電圧のいずれかがダイオードの破壊電圧を超えたとき、放電電流をバルク領域に伝えるように動作可能である。

(もっと読む)

完全に量子井戸が空乏化した低出力のマルチチャネルCMOSFET

マルチチャネル半導体デバイスは、完全に、または部分的に量子井戸が空乏化(排除)(depleted)されており、CMOSFETのようなULSIデバイスにおいて特に役立つ。マルチチャネル領域(15)は、最上部のチャネル領域上に、例えばゲート絶縁膜(14c)により分離されるゲート電極が形成された状態で、基板(12)上に形成される。マルチチャネル領域(15)およびゲート電極(16)の垂直方向の積み重なりが、デバイスによって占有されるシリコン領域を増加させることなく、半導体デバイス中の駆動電流を増加させることができる。  (もっと読む)

(もっと読む)

1 - 6 / 6

[ Back to top ]