Fターム[5F140BE18]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜の製造 (6,009) | 加熱方法 (114)

Fターム[5F140BE18]の下位に属するFターム

RTP、電子線 (101)

Fターム[5F140BE18]に分類される特許

1 - 13 / 13

半導体装置およびその製造方法

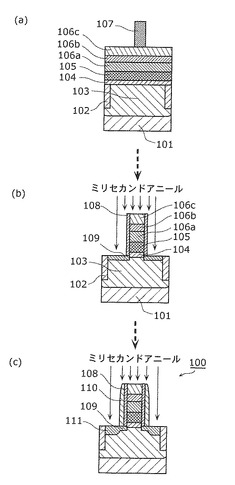

【課題】微細化が進んだ場合であっても、適切なしきい値電圧を有するpチャネルMOSFETを含む半導体装置を製造する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板101上に、SiO2またはSiONを含む第1ゲート絶縁層104を形成する第1ゲート絶縁層形成ステップと、第1ゲート絶縁層104上に、金属酸化物を含む第2ゲート絶縁層105を形成する第2ゲート絶縁層形成ステップと、第2ゲート絶縁層105上に、金属を含む第1電極106aを形成する第1電極形成ステップと、形成された積層構造に、複数回のミリセカンドアニール処理を行うことで、第2ゲート絶縁層105および第1電極106aの少なくとも一方に含まれる4族、5族または13族の元素を、第1ゲート絶縁層104と第2ゲート絶縁層105との界面に拡散させるアニールステップとを含む。

(もっと読む)

半導体装置の製造方法

【目的】ゲート酸化膜の信頼性を確保しながらB(ボロン)の吸い出し現象やP(リン)のパイルアップ現象を補償して正常に動作するMOSFET素子を形成できる半導体装置の製造方法を提供する。

【解決手段】n型拡散層9の表面層にp型拡散層10を形成し、その後のゲート酸化膜11の形成により生じたB(ボロン)の吸い出し現象やP(リン)のパイルアップ現象を900℃以上の熱処理をすることで補償し、n型化したp型拡散層10の表面をp型に戻して、ゲート酸化膜11の信頼性を確保しながら、正常に動作するMOSFET素子を有する半導体装置の製造方法を提供することができる。

(もっと読む)

半導体装置の製造方法

【課題】 高誘電体ゲート絶縁膜およびシリコン基板との界面を高品質化して、MISFETの特性向上を図る。

【解決手段】 シリコン基板11上にhigh−k膜21とゲート電極24を形成する半導体装置の製造方法において、high−k膜形成後にフッ素雰囲気でアニール処理23を施し、その後のプロセス温度を600℃以下で行う、半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】ナローチャネル特性の劣化を抑制する。

【解決手段】素子分離領域STIは、半導体基板100に形成されたトレンチ104内に設けられており、トレンチ104の側壁上に形成された下地絶縁膜105を有している。素子形成領域100a上にはゲート絶縁膜112が形成されており、ゲート絶縁膜112は高誘電率膜110を有している。高誘電率膜110の第1の部分110aは、素子形成領域100aにおける上面上に形成されており、高誘電率膜110の第2の部分110bは、素子形成領域における上部側面104a上に下地絶縁膜105を介して形成されている。第2の部分110bと下地絶縁膜105との間には、MISトランジスタの閾値電圧を変更する金属を含有する第1のキャップ膜106が設けられている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の高集積化と供に、メモリ装置のキパシタで容量値の確保のために、酸素欠損のない高誘電率膜を形成する装置の製造方法を提供する。

【解決手段】誘電体膜を形成する工程と、酸化性ガスを供給して誘電体膜に対して酸化処理を行う工程を複数回、断続的に繰り返す熱処理工程と、を有する誘電体膜を備えた半導体装置の製造方法。

(もっと読む)

薄膜形成方法、及び薄膜形成装置

【課題】 低温で形成されたSiO2膜は高温で形成されたSiO2膜より特性が僅かに劣るため、そのままでは使う事が出来なかった。又、高温で形成されたSiO2膜と同等の特性を得るためには、後工程で少なくとも500℃以上でのアニールを行う必要があった。ところが、プロセス低温化の要求から、基板温度を500℃以下に維持したまま、高品質なSiO2膜を形成する技術の開発が必要とされていた。

【解決手段】

活性な酸素原子を用いて500℃以下の低温でSiO2膜を成膜後、紫外光をシリコン基板のシリコン酸化膜側表面に1回または複数回照射する事で、Si基板を高温にする事なくSiO2膜の特性を改善させる事が可能となった。前記紫外光とは、200nm以上370nm以下の波長のみが含まれ、1回の照射時間が0.1マイクロ秒以下であり、照射1回当たりのエネルギー密度が0.01J/cm2以上であるという条件を満たす紫外光である。

(もっと読む)

MIS型FET及びその製造方法

【課題】動作時のゲート電極底端部において発生する電界集中を低減させた、製造歩留り及び信頼性の高いMIS型FET得る。

【解決手段】下地20上にエッチングレートの異なる二層構造のゲート絶縁膜を有し、ゲート絶縁膜に加工形成されたゲートコンタクトホールの底部側面及び底部が下地側に凸形状の曲面である。このゲート絶縁膜は、下地側から下層の第1ゲート絶縁膜30と第1ゲート絶縁膜のエッチングレートより大なるエッチングレートを有する上層の第2ゲート絶縁膜32から成る窒化シリコン膜である。

(もっと読む)

半導体装置の製造方法

【課題】ALD法で半導体ウエハ上に成膜した金属酸化物膜の膜厚分布を均一にする。

【解決手段】成膜装置11のチャンバ12内に半導体ウエハ1Wを配置し、ガス排気口14からチャンバ12内のガスを排気する。それから、ゲートバルブ15を閉じてガス排気口14からの排気を遮断した状態で、チャンバ12内に不活性ガスを導入してチャンバ内の圧力を133Pa以上、好ましくは667Pa以上で、101325Pa未満としてから、チャンバ12内に不活性ガスと金属酸化物成膜用の原料ガスとの混合ガスを導入する。その後、ゲートバルブ15を開けてガス排気口14からチャンバ12内のガスを排気してから、酸化用ガスをチャンバ12内に導入し、半導体ウエハ1Wに吸着されていた原料ガス分子と反応させて、半導体ウエハ1W上に金属酸化物膜を形成する。これらを繰り返すことで、半導体ウエハ1W上に所望の厚みの金属酸化物膜2が成膜される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高品質の極薄酸化膜を均一な膜厚で再現性良く形成する。

【解決手段】半導体ウエハ1Aを酸化膜形成室107の熱処理チャンバ120へ導入する工程と、熱処理チャンバ120内のガス雰囲気を窒素によって置換する工程と、第1の温度で、触媒を用いて酸素と水素から水分を合成する工程と、合成した水分を前記酸化炉107の熱処理チャンバ120へ導入して、気化状態を維持したまま、熱処理チャンバ120内の半導体ウエハ1Aの第1主面上に水分を含んだ酸化性雰囲気を形成する工程と、熱処理チャンバ120内の水分を含んだ酸化性雰囲気において、前記第1の温度より高い第2の温度まで半導体ウエハ1Aの主面をランプ加熱して、半導体ウエハ1Aの第1主面上のシリコン表面を熱酸化処理して絶縁膜を形成する工程と、前記工程の後、熱処理チャンバ120内の前記水分を含んだ酸化性雰囲気を窒素によって置換する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】良質なシリコン窒化膜、酸化アルミニウム膜、遷移金属高誘電率絶縁膜を形成することを可能にする。

【解決手段】半導体を主構成元素とする膜および半導体基板のいずれか一方上に、シリコン−窒素結合、アルミニウム−酸素結合、遷移金属−酸素−シリコン結合、および遷移金属−酸素−アルミニウム結合、遷移金属−酸素結合の少なくとも一つの結合を有する絶縁膜を形成するステップと、最大強度の波長が前記絶縁膜に応じた波長領域内でかつ前記絶縁膜に吸収される波長のパルス状赤外光を前記絶縁膜に照射するステップと、を備えている。

(もっと読む)

半導体構造

【課題】 金属ゲート電極層に望まれる特性は、微細加工を施された半導体立体構造体上に段差被覆率良く被覆されていることである。またもう一つの特性は、堆積された電極層の表面が1ナノメートルのスケールで平坦であり、電極層の堆積後に特別な平坦化処理を施すことなく電気的な絶縁を目的とした誘電体層を被服することが可能なことである。また、金属ゲート電極層に望まれる更なる特性の一つは、通常の半導体プロセスと同様のエッチング加工性を有していることである。また、金属ゲート電極層に望まれるもうひとつの特性は、結晶粒界がなく均一であり、不純物拡散が抑制された構造であることである。

【解決手段】 上記特性を満たす最良の金属ゲート電極としてアモルファス構造の金属電極が優れていることを見出し、本発明に至った。

(もっと読む)

半導体装置及びその製造方法

【課題】不純物の突き抜けや拡散を防止できる高性能な絶縁膜を提案する。

【解決手段】本発明の例に関わる半導体装置は、半導体基板11と、半導体基板11上に形成されるPチャネルMOSトランジスタのゲート絶縁膜13とを備える。ゲート絶縁膜13は、酸化膜(SiO2)と、少なくともボロン原子と窒素原子を含む拡散防止膜(BN)とから構成される。

(もっと読む)

多成分誘電体膜を形成するためのシステム及び方法

【課題】半導体用途における誘電体膜を形成するためのシステム及び方法、特に、混合気化前駆体を用いて基板上に多成分誘電体膜を作製するためのシステム及び方法を提供する。

【解決手段】本発明は、気化した前駆体の混合物が、原子層堆積(ALD)処理における単一パルス段階中にチャンバ内に一緒に存在して多成分膜を形成するような気化前駆体の混合をもたらすためのシステム及び方法を提供する。気化前駆体は、少なくとも1つの異なる化学成分から成り、そのような異なる成分が単層を形成して多成分膜を生成することになる。本発明の更に別の態様では、組成勾配を有する誘電体膜が提供される。

(もっと読む)

1 - 13 / 13

[ Back to top ]