Fターム[5F140BG52]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート側壁の形成方法及び除去 (3,620) | 堆積 (1,344) | CVD (924)

Fターム[5F140BG52]に分類される特許

921 - 924 / 924

マスキング方法

本発明はマスキング方法を包含する。1つの実施において、ホウ素ドープアモルファスカーボンを含むマスキング材料が、半導体基板上に形成されたフィーチャーを覆って形成される。マスキング材料は少なくとも約0.5原子パーセントのホウ素を含む。マスキング材料は実質的に異方的にエッチングされ、ここでそのエッチングはホウ素ドープアモルファスカーボンを含む異方的にエッチングされたサイドウォールスペーサをフィーチャーのサイドウォール上に形成するのに有効である。次に、スペーサに最も近い基板が、ホウ素ドープアモルファスカーボンを含むスペーサをマスクとして用いながら加工される。スペーサに最も近い基板を加工した後、ホウ素ドープアモルファスカーボンを含むスペーサが基板からエッチングされる。他の実施および面も考えられる。 (もっと読む)

空洞を有するシリコン基板上の高移動度MISFET半導体装置及びその製造方法

MISFETの高性能化を実現する高移動度歪みシリコン構造に、低欠陥かつ低コストで移動度を向上した半導体装置を提供する。MISFETの高性能化を実現する高移動度歪みシリコン構造として、空洞を有するシリコン基板上に、格子緩和シリコン・ゲルマニウム膜/濃度傾斜シリコン・ゲルマニウム膜を形成し、さらにその上に歪みシリコン膜を形成する。これにより、空洞近傍の格子の束縛が緩み、自由度が増すことにより、シリコン・ゲルマニウム膜の薄膜化が実現できるため、低欠陥かつ低コストで移動度を向上した半導体装置を提供できる。 (もっと読む)

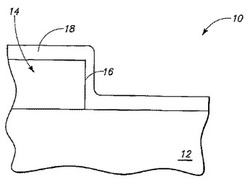

非対称の側壁スペーサの形成方法

集積回路半導体デバイスの製造プロセスに統合可能な非対称スペーサの形成方法が提供される。この方法は、基板上にゲート構造(15)を形成するステップと、ゲート構造および基板の上に側壁層(10)を形成するステップとを含み、側壁層は、ゲート構造の第1の側壁の上に第1の部分を含む。第1の部分に隣接して、フォトレジスト構造(11)が形成され、イオンビームにさらされる。フォトレジスト構造は、第1の部分の少なくとも一部をイオンビームから遮蔽するように働く。照射中、ウェハは、イオンビーム(13、17)の経路と、第1の側壁の表面との間に、非直交傾斜角が存在するように配向される。遮蔽されていない側壁部分への放射ダメージにより、その後に続くエッチングがより高速に進むため、非対称スペーサの形成が可能である。  (もっと読む)

(もっと読む)

低GIDLMOSFET構造および製造方法

【課題】 従来のMOSFETデバイスに比べてGIDL電流が小さい低GIDL電流MOSFETデバイス構造を提供する。

【解決手段】 MOSFETデバイス構造は、縁部がソース/ドレイン拡散にわずかに重なる場合(82)がある中央ゲート導体と、薄い絶縁性の拡散バリア層によって中央ゲート導体から分離した側方ウイング・ゲート導体とを含む。また、側方ウイング・ゲート導体の左右の横方向の縁部が、前記ソース拡散領域および前記ドレイン拡散領域の一方に重なる場合(80)も含まれる。

(もっと読む)

921 - 924 / 924

[ Back to top ]