Fターム[5H420NE06]の内容

電気的変量の制御(交流、直流、電力等) (13,664) | 機能 (487) | 起動停止 (77) | 外部からの信号により起動停止を行うもの (67) | 停止特性 (5)

Fターム[5H420NE06]に分類される特許

1 - 5 / 5

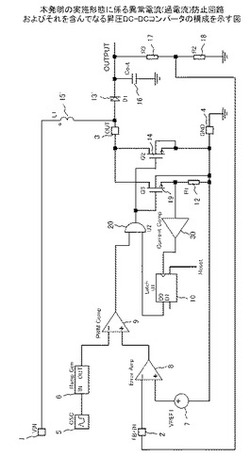

DC−DCコンバータの異常電流防止回路

【課題】回路規模が小さくて遅延が少なく且つ特性に与える素子バラツキの影響が小さいDC-DCコンバータの異常電流防止回路を提供する。

【解決手段】電流検出抵抗12を流れる電流を所定の基準電流と比較して過電流の有無を判定する電流コンパレータ30を備える。検出抵抗12の電圧は通常時(正常時)には負電圧であるが異常時に逆電流が生じた場合には正電圧が現れるようになる。電流コンパレータ30は検出抵抗12の電圧を監視し、検出抵抗12の電圧が負電圧の間はハイ出力をラッチ10を介してAND回路20に送ってPWM比較器9の出力信号がローサイド側スイッチ素子14,19に伝わるようにし、検出抵抗12の電圧が正電圧になると電流コンパレータ30の出力電圧はローになり、ローサイド側スイッチ素子14,19を強制的にOFFにする。

(もっと読む)

定電流回路

【課題】低電圧で動作可能で、かつ出力電流遮断時時のリーク電流が少ない定電流回路を提供することにある。

【解決手段】定電流回路10におけるカレントミラー部10Cは、負荷回路6に接続され、供給される基準電流に基づいて負荷回路6の電流を制御する。半導体スイッチ部10Sは、カレントミラー部10Cと接地極の間に配置され、カレントミラー部10Cに供給される基準電流と負荷回路6の電流をそれぞれ遮断する。

(もっと読む)

DC−DCコンバータの異常電流防止回路

【課題】回路規模が小さくて遅延が少なく且つ特性に与える素子バラツキの影響が小さいDC-DCコンバータの異常電流防止回路を提供する。

【解決手段】検出抵抗12の電圧は通常時(正常時)には負電圧であるが異常時に逆電流が生じた場合には正電圧が現れるようになる。電流コンパレータ30は検出抵抗12の電圧を監視し、検出抵抗12の電圧が負電圧の間はハイ出力をAND回路20に送ってドライバ10の出力信号がローサイド側スイッチ素子14,19に伝わるようにし、検出抵抗12の電圧が正電圧になると電流コンパレータ30の出力電圧はローになり、ローサイド側スイッチ素子14,19を強制的にOFFにする。電流コンパレータ30は従来の電圧コンパレータに比べ出力電流値を大きくすることができ、異常電流発生の判定に遅延が生じず速度が極めて速くなり、且つ変化幅を大きく取ることができる。

(もっと読む)

電圧源回路

【課題】出力キャパシタを用いた電圧源回路において、出力キャパシタの端子電圧を常に一定時間で直線的にグランド電位まで降下させることができるようにする。

【解決手段】出力キャパシタC1に初期電圧値を与える基準電圧源1と同一特性を持つ第2の電圧源2及び第3の電圧源3、倍率回路4,5、基準抵抗R1、第2の電圧源2から駆動電流が供給されるトランジスタQ1、及びトランジスタQ1の駆動電流を制御するオペアンプ(演算増幅器)OP1により、基準電圧源1の特性変動と相関関係を持つ特性変動を有する定電流回路を構成する。そして、出力キャパシタC1と並列にトランジスタQ1と同一のトランジスタQ2を接続し、上記定電流回路に流れる電流値と相関のある電流値で出力キャパシタC1を放電させる。

(もっと読む)

オペアンプ回路

【課題】オペアンプの出力電圧の立下りの応答性を改善することが可能なオペアンプ回路を提供することを目的とする。

【解決手段】オペアンプ31と、ドレイン端子がオペアンプ31の出力端子37に接続されソース端子がグランドに接続されゲート端子に入力される停止信号Ss1がハイレベルになるとオンし出力端子37の電圧をグランドレベルにするNチャネルのMOSFET2とを備えてオペアンプ回路3を構成する。

(もっと読む)

1 - 5 / 5

[ Back to top ]