Fターム[5J011CA11]の内容

ウェーブガイドの接合構造 (361) | 補助装置 (100) | 平面回路型 (80)

Fターム[5J011CA11]の下位に属するFターム

Fターム[5J011CA11]に分類される特許

1 - 13 / 13

リミッタ回路

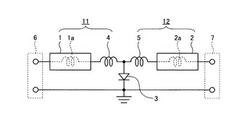

【課題】装置の大型化、伝送周波数における通過損失の上昇を招くことなく、高周波帯域の不要波による影響を抑制可能とするリミッタ回路を得る。

【解決手段】誘導性のマイクロストリップ線路1を含む入力側経路11と、誘導性のマイクロストリップ線路2を含む出力側経路12と、一端が接地され、他端が入力側経路11と出力側経路12との間に接続されたPINダイオード3と、を備え、PINダイオード3がキャパシタ性を有する小信号入力時において、入力側経路11および出力側経路12のインダクタンス値とPINダイオード3のキャパシタンス値とにより、当該リミッタ回路の伝送周波数を遮断周波数以下の通過帯域に含み、且つ、不要波の周波数を通過帯域に含まないローパスフィルタを形成する。

(もっと読む)

ノイズ抑制伝送路及びそれに用いられるシート状構造体

【課題】LSIなどの多数の配線のノイズを一括して抑制することができ、小型且つ薄型のノイズ抑制伝送路及びそれに用いられるシート状構造体を提供すること。

【解決手段】本発明のノイズ抑制伝送路は、少なくとも信号導体を備える配線層と、誘電体層と、シート状構造体とを備えている。シート状構造体は、所定パターンを有する単位形状を繰り返し並べてなる導電体層を備えており、誘電体層は、配線層と導電体層との間に設けられている。なお、配線層のグランド線と導電体層の一部とを接続することとしてもよい。以上の構成により、信号導体を流れるノイズを低減することを可能とした。

(もっと読む)

平面回路およびフィルタ回路

【課題】伝送線路の短絡部の接触抵抗による導体損を低減した平面回路を提供する。

【解決手段】誘電体基板と、前記誘電体基板の第1の面上に形成される伝送線路と、前記誘電体基板の前記第1の面と反対側の第2の面側に配置される導電板とを備え、前記伝送線路は、短絡部を有し、前記誘電体基板は、前記伝送線路の前記短絡部に対応する位置に貫通孔を有し、前記導電板は、前記伝送線路の前記貫通孔に挿入され、前記誘電体基板の前記第1の面側に突出する突起部を有し、前記伝送線路の前記短絡部は、前記導電板の前記突起部に電気的・機械的に接続されている。

(もっと読む)

導波路構造、プリント配線板、アンテナ、アレイアンテナ及びプリント基板並びにそれを用いた電子装置

【課題】小型化可能な導波路構造を、チップ部品を用いることなく低コストに実現し提供すること、およびそれを用いたプリント配線板を提供することを目的とする。

【解決手段】少なくとも、平行に配設された第1、第2の導体プレーン1,2と、第1の導体プレーン1及び前記第2の導体プレーン2と異なる層に配設され、第2の導体プレーン2をリターンパスとし、一端がオープン端となっている伝送線路4、および、伝送線路4の他端と第1の導体プレーン1とを電気的に接続する導体ビア5、を有する単位構造3と、を備え、単位構造3が1次元又は2次元に周期的に配列されている。

(もっと読む)

高周波回路基板、及び高周波回路基板のバイアス回路インピーダンス制御方法

【課題】広い周波数帯に渡って、挿入損失特性が良好で電流許容量の大きなバイアス回路を具えた高周波回路基板を提供する。

【解決手段】絶縁体で構成される基板11と、前記基板11上の主面上又は前記基板11内の少なくとも一方に形成された、高周波の電気信号を伝送するための金属導体部12と、前記基板11の裏面上及び前記基板11内の少なくとも一方に形成された電源層13と、前記金属導体部12内を伝送する前記電気信号に対して直流のバイアス電圧を重畳するためのバイアス回路14とを具備し、前記基板11は前記バイアス回路14のインピーダンスを調整するためのインピーダンス調整機構を有するようにして高周波回路基板10を構成する。

(もっと読む)

誘電体パッケージ

【課題】 抵抗体や電波吸収体の無反射条件を満足しつつ、不要共振周波数を抑制することのできるパッケージ構造を得ることを目的とする。

【解決手段】 半導体素子を収納するキャビティ21の形成された誘電体多層基板6と、キャビティ21を取り囲むようにキャビティ側壁内に配列された複数の金属充填スルーホール4と、キャビティ21を取り囲むように設けられ、キャビティ側壁内における金属充填スルーホール4の配列から、不要共振波の4分の1波長の距離だけ内側に配列され、無反射終端された複数の抵抗体充填スルーホール7とを備えて、誘電体パッケージ20を構成する。

(もっと読む)

半導体装置

【課題】マイクロストリップライン構造の信号線間のクロストークを効果的に低減することのできる半導体装置の配線構造を提供する。

【解決手段】 信号層1、グランド層2、および電源層3を備えたマイクロストリップライン構造を持つ半導体装置の配線構造であって、信号層1には、信号線11とともに、電源層3の電源線31とは別の電源線13が設けられており、この信号層1が、信号線11同士の間ならびに信号線11と電源線13との間に、グランド層2のグランド線21とは別のグランド線12を設けたコプレーナ構造となっている。

(もっと読む)

無限波長周波数におけるメタ物質右手系/左手系複合伝送線路を用いた電力結合器

【課題】 直列接続内において固定された波長位置決め(fixed wavelength positioning)を必要とせず、小型形状において実施可能な分配/結合装置及び方法を提供すること。

【解決手段】 右手系/左手系複合(CRLH)メタ物質線路において観察される無限波長現象を用いたトンネルダイオード発振器のための電力結合方法及び装置。ある実施例においては、各発振器の出力ポートは直接的に線路に接続され、かつ、同相で結合され、電力を位相において等しく結合するためのゼロ度線路から構成される直列結合器を利用している。第2の実施例においては、ゼロ度伝送線路のあるセクションが、波の振幅と位相が線路に沿って一定であるという条件下において、共振器に疎結合された発振器と共に、定常波長共振器を実行する。

(もっと読む)

可変メタマテリアル装置

本発明は、メタマテリアルなどの人工物質は調整可能な特性を含む。一部の手法においては、該特性は、電磁波との相互作用の能動的フィードバックに応じて調整可能である。

特に、可変装置であって、

相対的空間位置に配置された複数の人工要素の配置を備え、前記配置は、選択周波数で、前記要素の前記相対的空間位置と前記選択周波数での前記要素の前記回路応答との関数である、不均一な実効誘電率および/または透磁率を有し、複数の前記要素の前記回路応答は制御信号に応答して変化する、装置を提供する。  (もっと読む)

(もっと読む)

雷サージ保護回路

【課題】 RF信号ラインとサージアブソーバの間に介在した1/4波長長さのマイクロストリップ線路の線路幅を変えずに、従来技術より耐サージ電圧値を向上させた雷サージ保護回路を提供する。

【解決手段】 RF信号を通す配線に、1/4波長長さのマイクロストリップ線路を介して、サージアブソーバが接続され、前記配線に流入したサージ電流を前記サージアブソーバに導く雷サージ保護回路において、空芯コイル等を備えたバイパス経路を、前記マイクロストリップ線路に対し、並列に接続した構成とする。

(もっと読む)

RF素子でRFテスト及びDCテストが可能な装置及び方法

【課題】RF素子でRFテスト及びDCテストが可能な装置及び方法を提供する。

【解決手段】RF線と、RF線に連結されたDC線と、DC線と接地との間に連結されたキャパシタとを備え、RF線及びDC線それぞれを通じてRF信号端子からのRF信号及びDC信号を伝達するテストのための装置である。これにより、RF線上にDC線を追加しても、RF信号の共振現象なしにRF信号テスト帯域が確保される。DC線上には、計算された位置にオープンスタブのためのキャパシタを有し、DC線上の任意の位置にキャパシタを設置しようとする場合には、LC補助回路が利用される。

(もっと読む)

結合器リソース・モジュール

結合組立体は、積重ね配列に互いに融着された複数の複合基板層及びフランジ層を含む。基板層はフランジ層の上に位置づけられ、及び信号入力部及び信号出力部に接続された埋込信号処理回路を含む。信号接続端子を露出させるように基板層の領域を通じて空洞が形成される。これらの信号接続端子は、埋込信号処理回路に結合され、フランジ層と基板層の融着後に組立体に回路素子を追加可能にし、さらにその追加素子を信号処理回路に結合可能にする。 (もっと読む)

マイクロストリップ線路構造

【課題】 第1の信号が第2のマイクロストリップ線路に、また、第2の信号が第1のマイクロストリップ線路に混入されることできる限り阻止する中継導体を備えたマイクロストリップ線路構造を提供することにある。

【解決手段】マイクロストリップ線路構造においては、第1の信号を伝送する第1のマイクロストリップ線路11及びこの第1のマイクロストリップ線路11に交差する箇所で分断され、直流、或いは、前記第1の信号に比して周波数帯が低い第2の信号を伝送する第2のマイクロストリップ線路12a、12bが基板上に設けられ、前記分断された第2のマイクロストリップ線路12a、12bを接続する為にマイクロストリップ中継導体13が前記第1のマイクロストリップ線路11との間に間隙を空けて第1のマイクロストリップ線路11上を延出され、このマイクロストリップ中継導体13が電波吸収体15によって被覆されている。

(もっと読む)

1 - 13 / 13

[ Back to top ]