Fターム[5J014CA24]の内容

Fターム[5J014CA24]に分類される特許

1 - 8 / 8

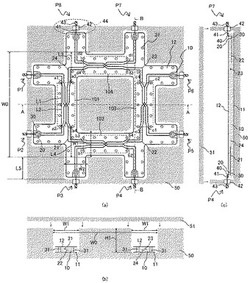

電力分配合成回路

【課題】単一の誘電体基板で簡素に構成されるとともに、キャビティ共振の抑圧による安定した回路性能の維持および気密封止を両立可能な電力分配合成回路を得る。

【解決手段】くり貫き部110を有し、M個の結合線路型カプラ101〜104がくり貫き部110を囲むように環状に配置された誘電体基板10を内部に封入する空洞200を有する金属ケース50は、誘電体基板10の裏面側に配置される底面219、誘電体基板10の表面側に配置される金属板51、くり貫き部110の内周側面側に配置され、くり貫き部110を貫通するとともに、底面219および金属板51と電気的に接続される金属壁210、並びに誘電体基板10の外周側面側に配置され、底面219および金属板51と電気的に接続される金属壁211〜218により構成され、M個の結合線路型カプラ101〜104は、多段結合線路またはテーパ結合線路により構成されている。

(もっと読む)

送信モジュール

【課題】 コアアイソレータ素子の挿入損失の増加を抑制した、送信モジュールを提供する。

【解決手段】 回路基板2は、グランドパターン3A〜3Dを備えた多層基板である。回路基板2には、電力増幅器10およびコアアイソレータ素子14が実装される。電力増幅器10およびコアアイソレータ素子14は、樹脂層12によって覆われる。樹脂層12の表面にはシールド層13が設けられる。コアアイソレータ素子14の天面14Aと、天面14Aと対向するシールド層13の天面シールド層13Aとの間隔、コアアイソレータ素子14の側面と、この側面と対向するシールド層13の側面シールド層との間隔を、所定の距離だけ離間して、コアアイソレータ素子14による挿入損失の増加を抑制する。

(もっと読む)

高周波回路モジュール

【課題】 高周波部品の間に高密度にシールド壁を実装することを目的とする。

【解決手段】 複数の高周波部品が実装された第1のプリント基板と、上記第1のプリント基板に対向配置され、上記高周波部品の実装領域に対向する部分に、複数の導体ビアの埋設壁面および表層または内層の導体層によって周囲が囲まれる掘り込みが設けられた第2のプリント基板と、上記第1、第2のプリント基板における、上記導体ビアに接続された対向する表層パターン同士が、半田によって電気的に接続されるとともに、上記第2のプリント基板における掘り込みを設けた空間内に上記高周波部品がそれぞれ収容され、上記高周波部品が当該掘り込みを設けたそれぞれの空間内に分離配置する。

(もっと読む)

極短パルス発生装置

【課題】構成簡易化、低コスト化、高性能化を実現可能なマイクロ波・ミリ波帯の極短パルス発生装置を提供する。

【解決手段】一対の軸対称な等傾斜角の先鋭部を具備する第1,第2導体パッチ2a,2bの各先鋭部を近接させ、高速変化信号発生部1を直に電気的接続して高速に変化する電圧を印加することで、第1,第2導体パッチ2a,2bが放射パルス形成回路と放射アンテナとを兼ねて機能させ、第1,第2導体パッチ2a,2bの両側方に対称軸と平行に配置した第1,第2導体壁3a,3bの間隔aを、不要信号の波長λaの1/2未満に、第1,第2導体パッチ2a,2bの各端部から第1,第2導体壁3a,3bの各端部までの距離Lw1,Lw2および誘電体基板4の導体パッチ面から第1,第2導体壁3a,3bの突出端部までの距離Lw3を全てλa/2以上にすることで、不要信号抑制手段を構成する。

(もっと読む)

高周波回路、低雑音ダウンコンバータおよびアンテナ装置

【課題】マイクロストリップラインの小型化を容易にかつ低コストで実現することが可能な高周波回路、低雑音ダウンコンバータおよびアンテナ装置を提供する。

【解決手段】高周波回路101は、誘電体基板13の第2主表面S2に設けれらた第1のアースパターン16と、誘電体基板13の第1主表面S1に設けられ、誘電体基板13および第1のアースパターン16とともにマイクロストリップラインを構成する信号パターン11と、第1主表面S1に設けられ、信号パターン11と間隔を隔てて設けられた第2のアースパターン15と、第2のアースパターン15と電気的に接続され、信号パターン11と隙間を設けて対向する金属部材12と、第1のアースパターン16および第2のアースパターン15と電気的に接続され、誘電体基板13、マイクロストリップラインおよび金属部材12を収容する金属筐体とを備える。

(もっと読む)

伝送線路

【課題】埋込グランド配線15同士の間隔が信号配線10を伝送する高周波の波長の1/4となる時に発生する共振現象を抑制する。

【解決手段】伝送線路は、対向する表面及び裏面を有する誘電体基板21と、この表面上に配置され且つ高周波を伝送する信号配線10と、表面上に配置され且つ信号配線10から絶縁された表面グランド電極11と、誘電体基板21の表裏面を貫通し且つ信号配線10に接続された貫通信号配線12と、基板裏面上に配置された裏面グランド電極14と、誘電体基板21に埋め込まれ且つ貫通信号配線12の周囲に円弧状且つ等間隔に配置された複数の埋込グランド配線15a〜15gとを有する。各埋込グランド配線15a〜15gが、表面グランド電極11及び裏面グランド電極14の少なくともいずれか一方に接続され、複数の埋込グランド配線15a〜15gが、前記した高周波の波長の1/4未満の間隔で配置されている。

(もっと読む)

高周波モジュール

【課題】前記のような課題を解決するためになされたものであり、製造が容易な構成を備え、かつ、空洞共振を抑圧することのできる高周波モジュールを得る。

【解決手段】高周波素子を内部に実装する筐体構造を備えた高周波モジュールにおいて、筐体構造の空洞共振周波数と同じ周波数で共振する共振構造6を筐体構造内部に設けている。これにより、共振構造6と金属製の蓋4とが結合し、共振構造6と金属製の蓋4を結ぶ面8の近辺に、電気壁が形成される。

(もっと読む)

半導体チップ実装基板

【課題】半導体チップを埋め込んだマルチポートの半導体チップ実装基板において、ポート間のアイソレーションを向上させること。

【解決手段】この半導体チップ100の1辺の長さは約2.5mmであり、この長さは、目的の高周波の環状溝210内における環方向の波長の半分余りに相当している。この半導体チップ100の周囲には、空洞部220に半導体チップ100を搭載した後の残りの空間によって、平面視時の輪郭が略正方形のリング形状の環状溝210が形成されている。そして、この環状溝210の4隅にはそれぞれ、銀ペーストからなる柱状導体1が埋め込まれている。即ち、この柱状導体1は、上記の空洞部220の内壁面と上記の半導体チップ100の側壁面との間の隙間から形成される環状溝210の4隅に配置されており、半導体チップ100の裏面に配置される共通グランドの上に直接立脚している。

(もっと読む)

1 - 8 / 8

[ Back to top ]