Fターム[5J023CA00]の内容

遅延要素を用いたフィルタ (1,075) | 構成 (105)

Fターム[5J023CA00]の下位に属するFターム

スイッチト・キャパシタフィルタ(SCF) (68)

スイッチト・キャパシタ積分器 (31)

Nパスフィルタ (3)

抵抗スイッチング

Fターム[5J023CA00]に分類される特許

1 - 3 / 3

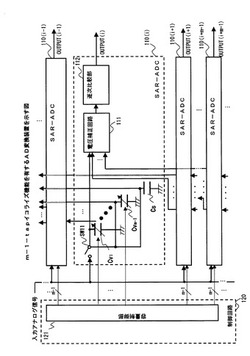

AD変換装置

【課題】アナログイコライザの前置を不要とするAD変換装置を提供する。

【解決手段】Nビット分解能を有するM個(M≧N+3)の逐次比較型AD変換回路と制御回路とを備え、各逐次比較型AD変換回路(i)は、入力アナログ信号のサンプリング電圧Vs(i)に相当する電荷Q(i)を保持する可変容量キャパシタCv1〜Cvm−1と、各可変容量キャパシタの容量の変更に応じて、逐次比較型AD変換回路(i)〜(i+m−2)内の、容量が変更された可変容量キャパシタCv1〜Cvm−1の端子間に現れる係数乗算電圧Vm(i)〜Vm(i+m−2)と、サンプリングタイミングT(i+m−1)に対応するサンプリング電圧Vs(i+m−1)とに基づいて、前補正電圧Vd(i+m−1)を生成する電圧補正回路と、Nビットのデジタル出力を生成する逐次比較部とを備え、可変容量キャパシタの容量を変化させる容量制御部を備える。

(もっと読む)

サンプルホールド回路およびパイプラインAD変換器

【課題】サンプルホールド回路のオペアンプのオフセット電圧をキャンセルする。

【解決手段】第1のクロックで入力信号をサンプリングする第1の容量と、第2のクロックで第1の容量に蓄積された電荷が供給される第2の容量と、第2のクロックで帰還用スイッチを介して入力信号を上記第1と第2の容量比で増幅して出力する増幅器と、第1のクロックに対して所定の位相でリセットスイッチが駆動されリセットスイッチを介して増幅器の入出力間を容量接続する第3の容量と、第1のクロックで基準電圧を第1と第2の容量に供給し、上記第2のクロックで基準電圧を上記第3の容量に供給する基準電位発生回路と、第1のクロックで第2の容量にコモン電圧を供給するコモン電圧供給回路と、第1のクロックで増幅器から出力されたオフセットを含む信号を増幅し、第2の容量にプリチャージするオフセットキャンセル回路とを有する。

(もっと読む)

アナログメモリ

【課題】

従来技術に係るアナログメモリでは、スイッチト・キャパシタ部SCの組数に比例して、放電用配線Loutの寄生容量が大きくなっていた。

【解決手段】

本発明に係るアナログメモリでは、複数のメモリブロックMBに分割されることにより、一の放電用配線Lout当たりの寄生容量が抑えられる。そして、次段階においてオペアンプOPの入力端子+と接続されるメモリブロックMBは、現段階においてオペアンプOPの出力端子−と接続される。したがって、メモリブロックMBの切り替えに伴う出力信号Voutの連続性に歪が生じなくなる。

(もっと読む)

1 - 3 / 3

[ Back to top ]