Fターム[5J023CA01]の内容

遅延要素を用いたフィルタ (1,075) | 構成 (105) | スイッチト・キャパシタフィルタ(SCF) (68)

Fターム[5J023CA01]の下位に属するFターム

Fターム[5J023CA01]に分類される特許

1 - 20 / 56

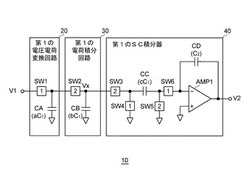

スイッチトキャパシター積分回路、フィルター回路、物理量測定装置、及び電子機器

【課題】面積が小さく、消費電流を大幅に低減することができるスイッチトキャパシター積分回路、フィルター回路、物理量測定装置、及び電子機器等を提供する。

【解決手段】スイッチトキャパシター積分回路としての2重正相積分回路10は、第1の容量CAを有し、第1の期間において入力信号に対応した電荷を第1の容量CAに充電する第1の電圧電荷変換回路20と、第2の容量CBを有し、第2の期間において第1の容量CAに充電された電荷の一部を第2の容量CBに充電し、第2の容量CBに充電された電荷の一部を転送する第1の電荷積分回路30とを含む。

(もっと読む)

離散時間アナログ回路及びそれを用いた受信機

【課題】フィルタの極の設定位置の自由度が高い、広帯域かつ急峻なフィルタ特性を有する離散時間アナログ回路および受信機を提供すること。

【解決手段】離散時間アナログ回路100は、ローテートキャパシタ回路150と、ローテートキャパシタ回路150の入力ライン又は出力ラインに接続され、入力電位又は入力電荷を増幅する増幅器141と、増幅器141に直列に配置され、互いに並列に配置される2個のヒストリキャパシタ143−1,143−2とを有する係数回路140と、2個のヒストリキャパシタ143−1,143−2のうち、増幅器141と接続されチャージされる第1のアクティブキャパシタと、増幅器141を介さずに入力ライン又は出力ラインと接続され、ローテートキャパシタ回路150と電荷共有される第2のアクティブキャパシタとのペアを順次変更するクロック生成回路110と、を具備する。

(もっと読む)

ダイレクトサンプリング回路

【課題】時分割統合された信号系列に対して、時分割で兼用する場合であっても、各系統間で信号の混ざりを回避するダイレクトサンプリング回路を提供する。

【解決手段】スイッチトキャパシタフィルタ160の前段に系統毎にヒストリキャパシタ153,155を接続し、スイッチトキャパシタフィルタ160の後段に系統毎にバッファキャパシタ173,175を接続し、スイッチトキャパシタフィルタ160のローテーションキャパシタと接続するヒストリキャパシタ及びバッファキャパシタを入力している時分割系統毎に切り替える。

(もっと読む)

スイッチトキャパシタフィルタ及びスイッチトキャパシタフィルタの制御方法

【課題】簡易な構成により雑音を低減することができるスイッチトキャパシタフィルタ及びその制御方法を提供すること。

【解決手段】本発明では、演算増幅器AMPの反転入力は積分キャパシタC0の一端と、出力は積分キャパシタC0他端と接続される。スイッチトキャパシタは第1〜3の順に接続状態が移行する。第1の接続状態では、第1の端子は入力信号と、第2の端子は固定電圧と接続される。第2の接続状態では、第1の端子は固定電圧と、第2の端子は演算増幅器AMPの反転入力と接続される。第3の接続状態では、第1の端子は演算増幅器AMPの出力と、第2の端子は演算増幅器AMPの反転入力と接続される。第2及び第3の接続状態のスイッチトキャパシタが各1個以上存在する場合の第2の接続状態のスイッチトキャパシタの個数は常に同じであり、第3の接続状態のスイッチトキャパシタの個数も常に同じである。

(もっと読む)

応答時間が高速なスイッチト・キャパシタ・ノッチ・フィルタ

電力を制限に準拠する72229パッシブ・スィッチ・キャパシタ・フィルタ

【解決手段】パッシブスィッチキャパシタ(PSC)フィルタは、明細書に記載されている。一例において、PSCフィルタは、二つの複素数1次IIR部を含む2次無限インパルス応答(IIR)フィルタを実施する。各複素数1次IIR部は、キャパシタの三つのセットを含んでいる。キャパシタの第1のセットは、実数入力信号及び虚数遅延信号を受信し、電荷を記憶及び共有し、実数フィルタ信号を提供する。キャパシタの第2のセットは、虚数入力信号及び実数遅延信号を受信し、電荷を記憶及び共有し、虚数フィルタ信号を提供する。キャパシタの第3のセットは、虚数及び実数フィルタ信号を受信し、電荷を記憶及び共有し、虚数及び実数遅延信号を提供する。他の例において、PSCフィルタは、複素数1次IIR部についての有限インパルス応答部及びIIR部を実施する。前記IIR部は、インタリーブされた方法で動作する複数の複素数フィルタ部を含んでいる。 (もっと読む)

離散時間受信機

【課題】本発明は離散時間受信機に関する。

【解決手段】本発明の離散時間受信機は、サンプリングクロックに応じて入力信号をサンプリングするサンプリングミキサと、制御信号を用いてデシメーション比を調節し、フィルタクロックを用いて上記サンプリングされた信号をフィルタリングする離散時間フィルタと、上記サンプリングミキサに供給されるサンプリングクロックを生成し、上記サンプリングクロックの周波数と予め設定された出力周波数とを比較して制御信号及びフィルタクロックを生成するクロック生成器と、を含み、広帯域の入力信号に対して出力信号のダイナミック範囲を向上させることができる。

(もっと読む)

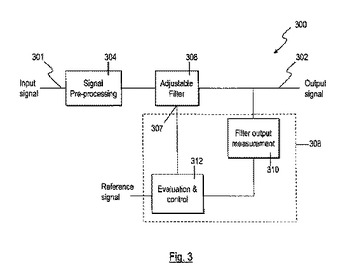

ホイールモニタリングシステムのための追跡フィルタ装置

ホイールモニタリングシステムは、変化する主周波数を有する信号を追跡する追跡フィルタ装置を含む。追跡フィルタ装置は、調整可能なフィルタと、フィルタリングされた信号の振幅を測定し、振幅を基準値に対して比較するように構成されたフィルタコントローラとを備える。フィルタコントローラは、測定された振幅が基準値から所定のしきい値を越える量にわたって相違するとき、フィルタのカットオフ周波数を調整する。フィルタコントローラは、主周波数がフィルタの周波数応答のロールオフ領域内に存在するように、カットオフ周波数を調整する。本システムは、ホイールに設けられたモニタリング装置の衝撃センサによって生成された信号を追跡するために使用可能である。  (もっと読む)

(もっと読む)

スイッチトキャパシタノッチフィルタ

複数のサンプリングキャパシタ(120a、120b)および複数の非重複期間を使用して入力信号(111)をサンプリングするためのスイッチトキャパシタノッチフィルタ(100)。サンプリングキャパシタからの電荷は、別の非重複期間の間に平均化され、フィルタ出力部(113)に移送される。  (もっと読む)

(もっと読む)

全差動型スイッチトキャパシタフィルタ回路およびA/Dコンバーター

【課題】入力インピーダンスが高く、ノイズや歪みの少ない出力信号を得ることのできる全差動型スイッチトキャパシタフィルタ回路およびA/Dコンバーターを提供する。

【解決手段】クロック生成回路11bから出力されるクロック信号φの1周期あたりでオペアンプAMP2がサンプリングキャパシタC1a,C2aに充電する電荷量(トランスファーフェーズにおけるサンプリングキャパシタC1a,C2aから積分キャパシタC1b,C2bに転送する電荷量)を変化させないと共に、1周期あたりの充電回数を1/2(1回)にすることで、SCF回路11aの入力インピーダンスを2倍にする。

(もっと読む)

フィルタ装置

【課題】アンチエイリアシングフィルタを搭載することなく、サンプリング周波数近傍のエイリアシングを減衰することができる小型のフィルタ装置を得ることを目的とする。

【解決手段】Clock11〜14に同期して、I信号をサンプリングして、そのI信号の帯域を制限するサンプリングフィルタ10と、Clock11〜14と4分の1周期ずれているClock21〜24に同期して、そのI信号と直交しているQ信号をサンプリングして、そのQ信号の帯域を制限するサンプリングフィルタ11とを設け、合成部12がサンプリングフィルタ10により帯域が制限されたI信号とサンプリングフィルタ11により帯域が制限されたQ信号を合成する。

(もっと読む)

フィルタ回路及び通信装置

【課題】寄生容量に起因する周波数特性の変化を確実に抑えること。

【解決手段】入力端に入力された電圧信号を電流信号に変換する電圧電流変換部106と、複数のキャパシタから構成され、電圧電流変換部106から出力された電流信号が周期毎に各キャパシタへ順次に入力され、電流信号が入力された1群のキャパシタの電荷を加算して出力する第1のキャパシタ集合体102と、複数のキャパシタから構成され、第1のキャパシタ集合体102から出力された電流信号が周期毎に各キャパシタへ順次に入力され、電流信号が入力された1群のキャパシタの電荷を加算して出力する第2のキャパシタ集合体104と、第1のキャパシタ集合体102において電荷を出力する任意のキャパシタと、当該電荷の出力による電流信号が入力される第2のキャパシタ集合体104のキャパシタとを個々に接続する複数の接続ノード110,112,114,116と、を備える。

(もっと読む)

サンプリングフィルタ

【課題】回路規模の増大を招くことなく、任意の重み付け係数を設定することができるサンプリングフィルタを得ることを目的とする。

【解決手段】制御信号生成部5が、電圧電流変換部2の帰還回路を構成しているスイッチ24のON時間T1と、スイッチ25のON時間T2を変更することで、キャパシタ12,13から電圧電流変換回路11に帰還される電荷の帰還時間を制御する。これにより、充放電部3のキャパシタ31〜34に充電される電荷に対して任意の重みを付けることが可能になる。

(もっと読む)

フィルタ回路及び通信装置

【課題】電荷の移動に伴う過渡現象が出力に与える影響を抑止すること。

【解決手段】入力端に入力された電圧信号を電流信号に変換するトランスコンダクタンスアンプ102と、複数のキャパシタから構成され、トランスコンダクタンスアンプ102から出力された電流信号が周期毎に各キャパシタへ順次に入力されるキャパシタ集合体と、電流信号が入力された1群のキャパシタを互いに接続し、当該1群のキャパシタに蓄積された電荷を加算するシェアスイッチS1aS〜S4aS,S1bS〜S4bSと、シェアスイッチS1aS〜S4aS,S1bS〜S4bSにより電荷が加算された後、1群のキャパシタのうちの少なくとも1つのキャパシタを出力端に接続するダンプスイッチS1aD〜S4aDと、を備える。

(もっと読む)

スイッチトキャパシタフィルタ回路

【課題】インバータにより反転増幅回路を構成したスイッチトキャパシタフィルタ(SCF)回路では、出力信号のオフセット電位が変動しやすい。

【解決手段】SCF回路2は、出力段にインバータ回路14a,14bを有した2つのSCF4,6を備え、差動形式の出力信号を生成する。差動出力端子間に接続した抵抗RA,RBは差動信号を分圧し、中点電位VCMを生成する。比較器30は、VCMと目標電位VCTとを比較する。インバータ回路14a,14bのCMOSインバータと接地電位との間に接続されたトランジスタは、比較器30での比較結果に応じてチャネル抵抗を変化させ、CMOSインバータの出力端のバイアス電位を変化させ、オフセット電位をVCTへ向けてフィードバック制御する。

(もっと読む)

フィルタ回路および通信装置

【課題】フライングキャパシタを備え、急峻な減衰特性を備えた上でさらにQ値を可変にすることが可能なフィルタ回路の提供。

【解決手段】入力端から出力端へ切り替わる場合には極性を維持し、出力端から入力端へ切り替わる場合には極性が反転するフライングキャパシタと、フライングキャパシタの入力端にフライングキャパシタと並列に設けられる第1のキャパシタCh1と、フライングキャパシタの出力端にフライングキャパシタと並列に設けられる第2のキャパシタCh2と、を備え、フライングキャパシタは、出力端から入力端へ切り替わってから所定の時間遅延して入力端から出力端へ切り替わり、入力端から出力端へ切り替わってから所定の時間遅延して出力端から入力端へ切り替わる、フィルタ回路。

(もっと読む)

サンプリングフィルタ

【課題】単極性の電圧電流変換回路を並列に接続することなく、正のタップ係数と負のタップ係数を同時に実現することができるサンプリングフィルタを提供する。

【解決手段】制御信号生成回路が充放電部3を構成しているスイッチ11〜17を制御して、電圧電流変換回路2から出力される電流を充放電部3を構成している2つのキャパシタ21,22に供給することで、キャパシタ21,22に電荷を充電させる一方、充放電部3を構成しているスイッチ11〜17を制御して、キャパシタ21,22に充電されている電荷を出力端子5,6に放電させる。

(もっと読む)

受動無線受信機

入力信号を受信しその入力信号を受動的に処理して出力信号を発生する受動無線受信機。この受動受信機の実施例は入力回路、ダイナミックスイッチング回路、スイッチ信号発生器を含む。この入力回路は入力信号を受信して第1の出力信号を発生するように構成される。入力回路はその入力信号に条件付けするように構成された受動ネットワークを含む。このダイナミックスイッチング回路は第1の出力信号に対して周波数変換を行なうように構成される。スイッチ信号発生器は、周波数制御回路によって制御され安定化されるサンプリング周波数でダイナミックスイッチング回路を活性化及び非活性化するようにダイナミックスイッチング回路を駆動するように構成される。 (もっと読む)

サンプルホールド回路

【課題】キャパシタを用いたサンプルホールド回路において、サンプリング時におけるキャパシタの充電状態をホールド状態とするためにオフされるべきスイッチにリーク電流が生じる。

【解決手段】サンプルホールド回路10は、オペアンプ12の反転入力端子IN−に一方端を接続されたキャパシタC1にサンプリング電圧に応じた電荷を蓄積する。その際、C1のIN−側の端子はスイッチ回路14を介して出力端子VOUTに接続し、所定電位に設定する。ホールド状態ではスイッチ回路14はオフされ、それが接続されたC1の端子をフローティング状態とする。スイッチ回路14は、IN−とVOUTとの間に直列に接続され同相でオン・オフされるMOSトランジスタスイッチS11,S12と、それら相互の接続点と接地電位との間に接続されたキャパシタC2とからなる。

(もっと読む)

フィルタ

【課題】タップ係数として任意の値を設定することができるフィルタを得ることを目的とする。

【解決手段】キャパシタ11,31により充電された電荷とキャパシタ13,33により充電された電荷の総和を出力端子Pに出力し、キャパシタ12,32により充電された電荷とキャパシタ14,34により充電された電荷の総和を出力端子Nに出力する。これにより、キャパシタ11〜14,31〜34の容量値Cpp,Cpn,Cnp,Cnnを適宜変更することで、タップ係数として任意の値を設定することができる。

(もっと読む)

1 - 20 / 56

[ Back to top ]