Fターム[5J023CA07]の内容

遅延要素を用いたフィルタ (1,075) | 構成 (105) | スイッチト・キャパシタ積分器 (31)

Fターム[5J023CA07]に分類される特許

1 - 20 / 31

スイッチドキャパシタ積分器

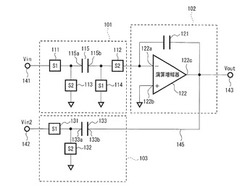

【課題】演算増幅器の充電にかかる負荷を抑え、低消費電力化を実現できるスイッチドキャパシタ積分器を提供する。

【解決手段】演算増幅器122を含む積分器102、演算増幅器122の入力端子122aに信号を入力するスイッチドキャパシタ回路101、演算増幅器122の出力端子122cと接続する出力端子443を有するスイッチドキャパシタ回路103を含み、積分器102及びスイッチドキャパシタ回路101がサンプリング動作と積分動作とを繰返し、スイッチドキャパシタ回路103は、キャパシタ133、キャパシタ133をサンプル、ホールド動作させるスイッチング素子131、132を含み、スイッチング素子131、132がキャパシタ133を、積分動作中にホールド動作させる。

(もっと読む)

スイッチトキャパシタ積分器

【課題】スイッチトキャパシタ積分回路に用いられる第1のコンデンサと第2のコンデンサの電圧依存性の影響の低減及び小型化が可能な、新規な構造のスイッチトキャパシタ積分回路を提供すること。

【解決手段】第1のコンデンサ18と、前記第1のコンデンサ18の一端と入力端子16との間に接続される第1のスイッチ12と、前記第1のコンデンサ18の他端に出力端20が接続され、非反転入力端子28が定電位源に接続される差動増幅器24と、前記第1のコンデンサ18の一端と前記差動増幅器24の反転入力端子26との間に接続される第2のスイッチ14と、前記差動増幅器24の出力端20と反転入力端子26の間に接続される第2のコンデンサ22とを備えた。

(もっと読む)

スイッチトキャパシター積分回路、フィルター回路、物理量測定装置、及び電子機器

【課題】面積が小さく、消費電流を大幅に低減することができるスイッチトキャパシター積分回路、フィルター回路、物理量測定装置、及び電子機器等を提供する。

【解決手段】スイッチトキャパシター積分回路としての2重正相積分回路10は、第1の容量CAを有し、第1の期間において入力信号に対応した電荷を第1の容量CAに充電する第1の電圧電荷変換回路20と、第2の容量CBを有し、第2の期間において第1の容量CAに充電された電荷の一部を第2の容量CBに充電し、第2の容量CBに充電された電荷の一部を転送する第1の電荷積分回路30とを含む。

(もっと読む)

スイッチトキャパシター回路、フィルター回路、物理量測定装置及び電子機器

【課題】所望の信号伝達関数でより一層の出力雑音成分を低減できるスイッチトキャパシター回路、フィルター回路、物理量測定装置及び電子機器等を提供する。

【解決手段】スイッチと、複数のサンプリング容量と、積分容量とを含んで構成されるスイッチトキャパシター積分回路10は、電荷充電期間T1の入力信号に対応した電荷をサンプリング容量の少なくとも1つに充電する。スイッチトキャパシター積分回路10は、電荷転送期間T2において、該電荷を積分容量に転送することで、該電荷に対応した信号を伝搬遅延させる。スイッチトキャパシター積分回路10は、例えばスイッチにより複数のサンプリング容量の接続を切り換えることにより、電荷充電期間T1にて決定される信号伝達関数と、電荷転送期間T2にて決定される雑音伝達関数とを異ならせる。

(もっと読む)

スイッチトキャパシタ回路

【課題】システムの性能劣化を避けつつ、システムの消費電力を低減する。

【解決手段】コンデンサC1と、コンデンサC1の入力側及び出力側にそれぞれ設けられたスイッチSW1〜SW4と、コンデンサC1の出力を受ける後段のオペアンプ204とを備え、スイッチSW1〜SW4の少なくとも一つの開閉状態に応じてオペアンプ204へ供給される電流値を切り替える。

(もっと読む)

信号モニタリングシステム

【課題】信号モニタリングシステムにおいて、応答速度およびモニタリング精度の両方を向上させる。

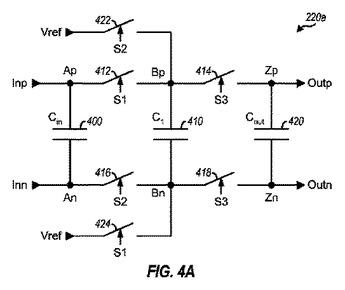

【解決手段】信号フィルタは、ノードと、第1端と、第2端と、前記ノード並びに前記第1および第2端に結合されたエネルギ蓄積回路とを有する。ノードは、入力信号および基準信号を選択的に受信する。第1端は、前記入力信号および基準信号によって特定された出力信号を提供する。第2端は、前記出力信号を示すフィードバック信号を受信する。エネルギ蓄積回路は、前記入力信号および基準信号に基づいて前記第1端で前記出力信号を発生させる。またエネルギ蓄積回路は、ノードを介して入力信号を受信するとともに、第2端を介してフィードバック信号を受信する、該動作を交互に実行する。信号フィルタの支配極は、第1入力信号およびフィードバック信号が交代されることについての周波数によって制御される。

(もっと読む)

時定数調整回路

【課題】参照用の時定数発生回路を集積回路の外部に用意すると、集積回路の端子数の増加および半導体チップ面積の増大を招き、その結果、製造コストが増大してしまう。また、集積回路単体では時定数の調整を行えない。

【解決手段】スイッチトキャパシタを用いることで、時定数発生回路を集積回路に内蔵しても十分な精度が保たれる。さらに、時定数の補正結果を記憶する記憶部を設けることで、時定数調整用回路と、時定数調整後の通常動作用回路を、一部兼用することが可能となる。集積回路の端子数と、半導体チップ面積を節約でき、その結果、製造コストを抑えられる。さらに、外部から電源さえ供給されれば、自動的かつ自律的に時定数の調整を行える。

(もっと読む)

スイッチトキャパシター回路を用いたハイパスフィルター及び電子機器

【課題】設計の自由度を失うことなく、SC回路を構成するスイッチのクロック周波数を高く、且つカットオフ周波数を低くする場合において面積をより小さくできるSC回路を用いたHPF等を提供する。

【解決手段】スイッチトキャパシター回路を用いたM(Mは2以上の整数)次のハイパスフィルターは、第1の入力端、第2の入力端及び出力端を備える第1のオペアンプOP1と、第1の入力キャパシターC1と、出力端から帰還される帰還信号に対してハイパスフィルターのゲイン調整を行うゲイン調整回路GA1とを有する第1のスイッチトキャパシター積分器1001を含み、第1の入力端に、ハイパスフィルターの入力信号VINが供給され、第2の入力端に、帰還信号が第1の入力キャパシターC1を介して供給され、出力端からハイパスフィルターの出力信号VOUTが出力される。

(もっと読む)

スイッチトキャパシター回路を用いたハイパスフィルター及び電子機器

【課題】設計の自由度を失うことなく、SC回路を構成するスイッチのクロック周波数を高く、且つカットオフ周波数を低くする場合において面積をより小さくできるSC回路を用いたHPF等を提供する。

【解決手段】スイッチトキャパシター回路を用いたM(Mは2以上の整数)次のハイパスフィルター10は、第1の入力端、第2の入力端及び出力端を備える第1のオペアンプをOP1と、第1の入力キャパシターC1とを有する第1のスイッチトキャパシター積分器1001を含み、第1の入力端に、前記ハイパスフィルター10の入力信号VINが供給され、第2の入力端に、出力端から帰還された帰還信号が第1の入力キャパシターC1を介して供給され、出力端からハイパスフィルター10の出力信号VOUTが出力される。

(もっと読む)

スイッチト・キャパシター増幅回路及びそのスイッチ制御方法

【課題】高速かつ高精度なスイッチト・キャパシター増幅回路の提供。

【解決手段】オペアンプOA1と、オペアンプOA1に供給する基準信号VRを生成する基準信号生成回路X11と、オペアンプOA1の第1の入力端子に接続された第1の入力容量C11と、第1の入力容量量C11に第1の入力信号を伝送する第1の入力スイッチS15と、オペアンプOA1の第1の出力端子からの出力信号を第1の入力端子へフィードバックするための第1の帰還容量C12と、第1の出力端子と第1の帰還容量C12との間に設けられた第1の帰還スイッチS12と、第1の帰還容量C12に充電された電荷をリセットするための第1のリセットスイッチS21と、を備えたスイッチト・キャパシター増幅回路。

(もっと読む)

ダイレクトサンプリング回路及び受信機

【課題】比較的簡易な構成及び簡易なクロックで、良好な周波数特性を有するダイレクトサンプリング回路及び受信機を提供する。

【解決手段】離散時間回路102−1〜102−4において、充電スイッチ1021は、4相の制御信号のうち、いずれか一つの制御信号を用いてオンオフ制御され、ローテートキャパシタ1022は、充電スイッチ1021を介して、IQ生成回路101に蓄積された電荷を電荷共有し、ダンプスイッチ1023は、4相の制御信号のうち、充電スイッチ1021をオンオフ制御する制御信号と位相が異なる信号が用いられてオンオフ制御され、バッファキャパシタ1026は、ダンプスイッチ1023を介して、ローテートキャパシタ1022と電荷共有することにより出力値を形成する。

(もっと読む)

スイッチトキャパシタノッチフィルタ

複数のサンプリングキャパシタ(120a、120b)および複数の非重複期間を使用して入力信号(111)をサンプリングするためのスイッチトキャパシタノッチフィルタ(100)。サンプリングキャパシタからの電荷は、別の非重複期間の間に平均化され、フィルタ出力部(113)に移送される。  (もっと読む)

(もっと読む)

全差動型スイッチトキャパシタフィルタ回路およびA/Dコンバーター

【課題】入力インピーダンスが高く、ノイズや歪みの少ない出力信号を得ることのできる全差動型スイッチトキャパシタフィルタ回路およびA/Dコンバーターを提供する。

【解決手段】クロック生成回路11bから出力されるクロック信号φの1周期あたりでオペアンプAMP2がサンプリングキャパシタC1a,C2aに充電する電荷量(トランスファーフェーズにおけるサンプリングキャパシタC1a,C2aから積分キャパシタC1b,C2bに転送する電荷量)を変化させないと共に、1周期あたりの充電回数を1/2(1回)にすることで、SCF回路11aの入力インピーダンスを2倍にする。

(もっと読む)

スイッチトキャパシター回路を用いた積分回路、ローパスフィルター及び電子機器

【課題】オペアンプの入力キャパシターと帰還キャパシターの比を大きくすることなく、

カットオフ周波数が低いスイッチトキャパシター回路を用いた積分回路等を提供する。

【解決手段】SC積分回路50は、オペアンプOPAと、オペアンプOPAの帰還経路に

設けられる帰還キャパシターC3と、信号入力ノードP1とオペアンプOPAの入力ノー

ドとの間に設けられる入力キャパシター回路100とを含む。入力キャパシター回路10

0は、信号入力ノードと第1ノードとの間に設けられる第1のスイッチと、第1ノードと

基準電位との間に設けられる第2のスイッチと、第1ノードと第2ノードとの間の容量値

を変更可能に構成された第1のキャパシター部と、信号入力ノードと第3ノードとの間に

設けられる第3のスイッチと、第3ノードと基準電位との間に設けられる第4のスイッチ

と、第3ノードと第4ノードとの間に設けられる第2のキャパシターとを含む。

(もっと読む)

スイッチトキャパシタ回路を用いた積分回路、ローパスフィルタおよび電子機器

【課題】 カットオフ周波数が極めて低いスイッチトキャパシタ積分回路(SC積分回路)を、SC回路のキャパシタ(入力容量)およびオペアンプの帰還容量の容量値の比(Cp/Ci:容量素子係数)を極端に小さくすることなく、高精度に実現すること。

【解決手段】 積分回路の入力部170において、第1の入力回路(第1のスイッチトキャパシタ回路)10と、第2の入力回路(第2のスイッチトキャパシタ回路)11と、積分部61とを設ける。SC積分回路150の等価的な伝達関数をH(z)とするとき、{αH(z)−(α−X)H(z)}で表わされる信号処理を実行する。すなわち、信号伝送路において電荷の減算を実行し、キャパシタの容量値を、見かけ上、小さくし、現実的なサイズのキャパシタを用いて、カットオフ周波数が極めて低いSC積分回路を構成する。

(もっと読む)

離散時間型マルチ・レート・アナログ・フィルタ

【解決手段】レシーバ及び他の電子デバイスでの使用に適した離散時間型アナログ・フィルタが明細書に記載されている。一デザイン例の装置は、トランスコンダクタンス増幅器、サンプラ、及び離散時間型アナログ・フィルタを備え得る。トランスコンダクタンス増幅器は、電圧入力信号を増幅しアナログ信号を提供し得る。サンプラは、サンプリング・レートでアナログ信号をサンプリングし、アナログ・サンプルを提供し得る。離散時間型アナログ・フィルタは、ノン・デシメート・フィルタのサンプリング・レート、またはデシメート・フィルタのサンプリング・レートよりも低い出力レートでアナログ・サンプルをフィルタリングし、フィルタリングされたアナログ・サンプルを提供し得る。離散時間型アナログ・フィルタはまた、レクタンギュラ・フィルタの均等な重み、または重み付けフィルタの少なくとも二つの異なる重みでアナログ・サンプルをフィルタリングし得る。 (もっと読む)

スイッチドキャパシタデシメータ

出力サンプルレートの奇数高調波における望ましくない信号成分を減衰させることができるスイッチドキャパシタデシメータが、説明される。スイッチドキャパシタデシメータは、少なくとも1つのサンプリングキャパシタと、複数のスイッチと、を含む。各サンプリングキャパシタでは、上部プレートは、キャパシタが上部充電のために選択されるときに、第1の入力信号で充電され、下部プレートは、キャパシタが下部充電のために選択されるときに、第2の入力信号で充電される。各サンプリングキャパシタでは、キャパシタが読取りのために選択されるときに、上部プレートは、その蓄積された電荷を第1の出力信号へと供給し、下部プレートは、その蓄積された電荷を第2の出力信号へと供給する。スイッチは、充電のためには第1および第2の入力信号に、読取りのためには第1および第2の出力信号に、少なくとも1つのサンプリングキャパシタを結合する。  (もっと読む)

(もっと読む)

スイッチトキャパシタ回路を用いた積分回路、ローパスフィルタおよび電子機器

【課題】 カットオフ周波数が極めて低いスイッチトキャパシタ積分回路を、オペアンプの入力容量とオペアンプの帰還容量の比を大きくすることなく、高精度に実現する。

【解決手段】 積分回路50の入力部100に含まれるスイッチトキャパシタ回路(SC回路)は、第1のスイッチ回路SW1と、第1のキャパシタ部TS(1)と、第2のスイッチ回路SW2と、第2のキャパシタ部TS(2)と、第3のスイッチ回路SW3と、第4のスイッチ回路SW4と、を有し、第1のキャパシタ部TS(1)は、T字形に結線されたキャパシタGA1,GA2およびGA3を有し、第2のキャパシタ部TS(2)は、T字形に結線されたキャパシタGB1,GB2およびGB3を有する。

(もっと読む)

チャージドメインフィルタ回路

【課題】 低消費電力で動作可能であり、かつ、フィルタ特性がリコンフィギュアラブルである、チャージドメインフィルタ回路を提供すること。

【解決手段】所定の間隔でサンプリングされる第1の信号を出力する第1の信号出力手段と、第1の信号と同間隔で、かつ異なるタイミングでサンプリングされる第2の信号を出力する第2の信号出力手段と、第1の信号と第2の信号とを加算して出力する加算手段と、を含み、第2の信号出力手段は、第2の信号のサンプリングのタイミングを複数の中から選択可能であることを特徴とする、チャージドメインフィルタ回路が提供される。

(もっと読む)

複数のクロックを用いるサンプリングフィルタ

フィルタリングされた入力信号の一連のサンプルを形成する方法及び装置に関する。複数のタップ電流セルは、夫々、入力信号からタップ電流を生成する。複数の分配手段はタップ電流セルを複数の積分手段に結合する。分配手段は、第1のクロック信号によって制御される。複数の積分手段は、それらが受け取るタップ電流を積分して、サンプルを形成する。生成されたタップ電流は、夫々、第1のクロック信号に従って所定のシーケンスで各積分手段へ送られる。積分手段は、夫々、第2のクロック信号によって制御される積分相及びサンプリング相を用いる。積分相の間、積分手段は順にタップ電流を受け取り、一方、休息相の間、タップ電流は受け取られず、回路のコンテンツはサンプリングされ、積分手段はリセットされる。  (もっと読む)

(もっと読む)

1 - 20 / 31

[ Back to top ]