Fターム[5J030CC04]の内容

音質制御、圧縮伸張、振幅制限 (2,281) | 振幅制限回路要素 (264) | 増幅器 (83) | 多段接続増幅器 (8)

Fターム[5J030CC04]に分類される特許

1 - 8 / 8

振幅制限増幅回路

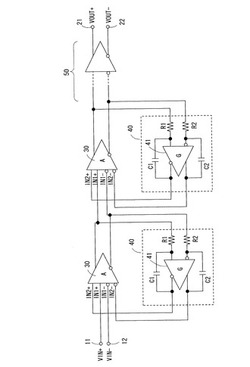

【課題】差動出力信号間のオフセット電圧を充分に抑圧し、出力信号のデューティ比の悪化を防ぐこと。

【解決手段】差動振幅制限増幅器30と、該差動振幅制限増幅器の出力差動信号をオフセット電圧抑制のために前記差動振幅制限幅器の入力側にフィードバックする差動アクティブ・ローパスフィルタ回路40と、からなる回路を、2段以上に亘って縦続接続したて構成する。

(もっと読む)

振幅制限増幅回路

【課題】差動入力を可能とし、入力される信号電力の損失を低減させる。

【解決手段】外部入力端子1に入力側が接続された平均値検出回路5Aと、非反転入力端子が外部入力端子1に接続され、反転入力端子が平均値検出回路5Aの出力側に接続された差動型振幅制限増幅回路4Aと、外部入力端子2に入力側が接続された平均値検出回路5Bと、非反転入力端子が外部入力端子2に接続され、反転入力端子が平均値検出回路5Bの出力側に接続され、差動出力端子対が差動型振幅制限増幅回路4Aの差動出力端子対に対して同相の組合せで並列接続された差動型振幅制限増幅回路4Bとを備える1段目差動増幅回路3A、および1段目差動増幅回路3Aの差動出力端子対の一方の端子に入力側が接続された平均値検出回路5Cと、非反転入力端子が平均値検出回路5Cの出力側に接続され、反転入力端子が1段目差動増幅回路3Aの差動出力端子対の他方の端子に接続された差動型振幅制限増幅回路7とを備える2段目差動増幅回路6を有する。

(もっと読む)

振幅制限増幅回路

【課題】同符号連続耐性と応答時間の短縮と残留オフセット電圧の抑圧とを同時に実現する。

【解決手段】バースト先頭においてはフィードフォワード型オフセット補償回路により瞬時にオフセットを補償し、その後フィードバック型オフセット補償回路によりフィードフォワード型オフセット補償回路で生じる長期的なオフセット変動を補償する。フィードフォワード型オフセット補償回路によるバースト先頭でのオフセット補償時には、フィードバック型オフセット補償回路のアナログスイッチ41をオフ、アナログスイッチ42をオンしておき、時定数の小さいローパスフィルタ22を必要な電圧に急速充電させる。この後オフセット補償回路のキャパシタへの瞬時的な充電が完了するタイミングで、アナログスイッチ41をオンしてローパスフィルタ22の出力電圧を差動増幅器13に入力させるとともに、時定数の大きなローパスフィルタ21を帰還ループに加える。

(もっと読む)

オペアンプのリミッタ回路

【課題】オペアンプに内蔵されるリミッタ回路において、オペアンプの出力電圧を任意の電圧に制限できるようにすることである。

【解決手段】PNPトランジスタQ6のベースには、直列接続されたトランジスタQ8、Q9が接続され、トランジスタQ8のエミッタには上限値Vupと等しい電圧が印加されている。出力段のPNPトランジスタQ7のベース電圧が上昇して、上限値VupからPNPトランジスタのエミッタ・ベース間の電圧降下を引いた電圧より大きくなると、トランジスタQ6がオンし、トランジスタQ7のベース電圧がそれ以上大きくならないように制限される。これにより、トランジスタQ7の出力電圧Voutが上限値Vupに制限される。

(もっと読む)

信号増幅回路

【課題】各要素の製造バラツキや温度依存性の影響を受けにくくして、出力特性である飽和電圧のバラツキが小さい信号増幅回路を提供する。

【解決手段】下限電圧制限回路20は、オペアンプ21の非反転入力端子がVref1端子50へ接続され、オペアンプ21の反転入力端子にはVout02端子が接続されている。またオペアンプ21の出力端子にはダイオード22のアノード端子が接続され、ダイオード22のカソード端子はVout端子02へ接続されている。上限電圧制限回路30は、オペアンプ31の非反転入力端子がVref2端子60へ接続され、オペアンプ31の反転入力端子にはVout端子02が接続されている。またオペアンプ31の出力端子にはダイオード32のカソード端子が接続され、ダイオード32のアノード端子はVout端子02へ接続されている。

(もっと読む)

瞬時応答振幅制限増幅回路

【課題】入力信号にノイズがのった場合でも、ダイナミックレンジが取れる瞬時応答振幅制限増幅回路の提供する。

【解決手段】入力信号と該入力信号をデータの1ビット以下だけ遅延した遅延信号との差信号を差動増幅回路2A,2B,2Cで増幅し、該差動増幅回路2A,2B,2Cの出力をそれぞれヒステリシス比較回路3A,3B,3Cに入力し、しきい値と比較する。該ヒステリシス比較回路3A,3B,3Cの出力の内の1つを選択回路5で選択する。振幅検出回路4は、ヒステリシス比較回路3A,3B,3Cの信号有りを示す出力の内から、最も利得が小さい経路で増幅された出力が選択回路5で選択されるような選択信号を出力する。

(もっと読む)

スイッチトキャパシタアンプ回路およびこれを用いた固体撮像装置

【課題】

スイッチトキャパシタアンプ回路およびこれを用いた固体撮像装置で任意の利得でログリニア可変する。

【解決手段】

アンプと、第1の時間位相に、入力信号が供給される入力端子と前記アンプの入力端子間に接続される第1の固定キャパシタと第1の可変キャパシタを有するn(nは1以上に整数)個の入力回路と、第2の時間位相に、アンプの出力端子に接続される、第2の固定キャパシタと第2の可変キャパシタを有するm(mは1以上の整数)個の帰還回路とを有し、第1と第2の可変キャパシタの総和を一定とした条件で可変して入出力特性がログリニアで可変するようにした。

(もっと読む)

リミッタアンプ

出力信号のDC成分を入力にフィードバックしてDCオフセットを相殺するDCフィードバック型のリミッタアンプは、動作状態と休止状態との切り替えが可能な差動増幅器(1,2)と、インピーダンス素子(5,6)と容量素子(3,4)とからなり、最終段の差動増幅器(2)の出力信号(out+,out−)からDC成分のみを取り出して入力段の差動増幅器(1)のフィードバック入力端子に入力するローパスフィルタと、インピーダンス素子(5,6)と並列に接続されたスイッチ(7,8)と、増幅器(1,2)が休止状態から動作状態になるときスイッチ(7,8)を一定時間閉状態にする制御回路(11)とを備える。  (もっと読む)

(もっと読む)

1 - 8 / 8

[ Back to top ]