Fターム[5J039EE01]の内容

Fターム[5J039EE01]の下位に属するFターム

二出力のインターロックをとるもの (1)

ノンオーバーラップ化 (8)

Fターム[5J039EE01]に分類される特許

1 - 8 / 8

半導体装置

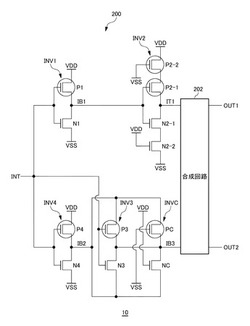

【課題】入力信号に基づいて位相の一致した相補の出力信号を生成する。

【解決手段】半導体装置に含まれるスプリッター回路10は、入力信号INTを受けて反転信号IB1を出力するインバータINV1と、反転信号IB1を受けて非反転信号IT1(第1の出力信号)を出力するインバータINV2が縦続接続される信号パスPASS1を含む。また、スプリッター回路10は、入力信号INTを受けて反転信号IB3(第2の出力信号)を出力するインバータINV3を含む信号パスPASS2を含む。また、インバータINV3と補助インバータINVCは出力信号線を共有する。インバータINV3と補助インバータINVCは、共に、入力信号INTの反転信号を電源とする。

(もっと読む)

半導体装置、電子機器、及び出力波形歪み改善方法

【課題】N本のクロック信号を出力した際に生ずる出力波形歪みを改善した装置構成を提供する。

【解決手段】半導体装置は、所定周波数の入力クロック信号CLK−Iを入力して同一周波数の複数のクロック信号CLK1からCLKNを出力する。前記入力クロック信号は遅延部1_1から遅延部1_N−1により所定の遅延時間差を与えられ、前記複数のクロック信号として出力される。前記複数のクロック信号の立ち上がり及び立ち下がりを分散することで、共通の電源レギュレータ11への負荷が低減する。

(もっと読む)

クロックバッファ回路及びこれを用いたクロック分配回路

【課題】小さな回路規模により広帯域のクロック信号に対応できるクロックバッファ回路を提供すること。

【解決手段】本発明の一態様であるクロックバッファ回路100は、ドライバ部11及びLCタンク部21を有する。ドライバ部11は、クロック入力IN及びINBからの入力クロック信号の少なくとも正転出力を、それぞれクロック出力OUT及びOUTBへ出力する。LCタンク部は、ドライバ部11とクロック出力OUT及びOUTBとの間に配置される。ドライバ部11は、入力クロック信号の周波数に対応した制御信号に応じて、ドライバ部11の入力と出力とを短絡させるスイッチSW1及びSW2を有する。

(もっと読む)

半導体装置

【課題】マルチプレクサとクロック分割回路との間における相互の電源ノイズの影響を低減する。

【解決手段】外部クロック信号CKに基づいて内部クロック信号LCLK1を生成するDLL回路100と、内部クロック信号LCLK1に基づいて、互いに位相の異なる内部クロック信号LCLK2,LCLK2Bを生成するクロック分割回路200と、内部データ信号CD,CEに基づいて、クロック信号LCLK2,LCLK2Bにそれぞれ同期した内部データ信号DQP,DQNを出力するマルチプレクサ300とを備える。クロック分割回路200に供給される内部電源電圧VPERI2とマルチプレクサ300に供給される内部電源電圧VPERI3は、互いに異なる電源回路82,83によって生成され、且つ、該半導体装置内で分離されている。これにより、相互にノイズの影響を及ぼし合うことがなくなる。

(もっと読む)

クロック分配回路及びその回路を含む半導体回路装置

【課題】

半導体チップを製造する際の製造バラツキ又は半導体チップ内の半導体回路の動作条件による、複数の最終バッファから出力される複数のクロック間の位相差を軽減することが可能なクロック分配回路を提供することを目的とする。

【解決手段】

回路装置内に配置されたクロック分配回路であって、リング状のクロック配線と、前記クロック配線に接続し、自己発振により、前記クロック配線内に第1クロック信号を発生させる発振回路と、前記回路装置内において、2以上の場所それぞれに、配置され、第2クロック信号を出力する2以上の位相調整回路と、を備え、前記位相調整回路それぞれは、配置場所に応じた位相を有する前記第1クロック信号を受け取り、前記位相調整回路それぞれが受け取った前記第1クロック信号間の位相差よりも、前記位相調整回路それぞれが出力する前記第2クロック信号間の位相差を減じる調整を行うことを特徴とするクロック分配回路。

(もっと読む)

単相差動変換回路

【課題】

正相出力信号と逆相出力信号とが180°の位相差で位相が一致する単相差動変換回路を提供する。

【解決手段】

単相差動変換回路は,単相入力信号が入力される入力端子と,正相出力信号が出力される正相出力端子と,正相出力信号と差動関係にある逆相出力信号が出力される逆相出力端子と,入力端子と正相出力端子との間に設けられ,直列に接続された第1,第2のインバータを少なくとも含む第1のインバータ列と,入力端子と逆相出力端子との間に設けられ,直列に接続された第3,第4,第5のインバータを少なくとも含み第1のインバータ列よりも段数が1段多い第2のインバータ列とを有し,第1のインバータ列は,さらに,第1のインバータの出力端子にドレインが接続され,導通しない電圧にゲートが接続されたトランジスタを有するダミーインバータを有する。好ましくは,第1,第2,ダミー,第3,第4,第5のインバータのゲート幅の比が,m/2:m2:m/2:1:m:m2であり,前記mはインバータの増倍率である。

(もっと読む)

相補信号生成回路

【課題】

同相信号と逆相信号とのスルーレート差や遅延差を低減するとともに、製造ばらつきによる影響を低減できる相補信号生成回路を提供することができる。

【解決手段】

本発明にかかる相補信号生成回路は、入力信号に基づく逆相信号S21を反転した同相信号S22を生成するインバータ22と、逆相信号S21に応じて電源電位VDDとBAR端子間を導通させるトランジスタN12と、同相信号S22に応じてBAR端子と接地電位GND間を導通させるトランジスタN12と、同相信号S22に応じて電源電位VDDとTRUE端子間を導通させるトランジスタN13と、逆相信号S21に応じてTRUE端子と接地電位GND間を導通させるトランジスタN14と、を備えるものである。

(もっと読む)

デューティ補正機能を有する電圧制御発振機

【課題】簡単な回路でデューティ50%のクロックをより安定的に発生することが可能で、雑音特性に優れたデューティ補正機能付きの電圧制御発振機を提供する

【解決手段】デューティ補正機能を有する電圧制御発振機は、制御電圧VCによる発振周波数を有し、相互180度の位相差を有する第1及び第2信号SV+、SV−を生成して第1、第2発振出力端VO+、VO−を通じ出力するVCO部100、及び上記VCO部100の第1、第2発振出力端VO+、VO−を通った第1及び第2信号SV+、SV−によって50%のデューティを有するクロック信号SCLKを生成するデューティ補正部200を含む。

(もっと読む)

1 - 8 / 8

[ Back to top ]