Fターム[5J039EE08]の内容

Fターム[5J039EE08]の下位に属するFターム

単安定素子によるもの

遅延線によるもの (39)

Fターム[5J039EE08]に分類される特許

1 - 11 / 11

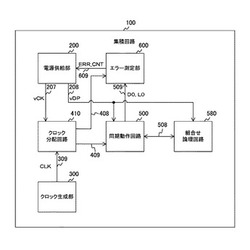

集積回路

【課題】集積回路において電力消費量を容易に低減する。

【解決手段】集積回路は、クロック分配回路、同期動作回路、論理回路、および、電源供給部を備える。クロック分配回路は、所定のタイミングを指示するクロック信号を分配する。同期動作回路は、クロック信号に同期して動作する。論理回路は、同期動作回路の動作結果に基づいて所定の論理演算を実行する。電源供給部は、クロック分配回路を駆動させるクロック分配回路駆動電圧より低い電圧を論理回路に論理回路駆動電圧として供給する。

(もっと読む)

信号生成回路及びその信号生成方法

【課題】信号生成回路において、容易に、十分な出力信号レベルを確保したまま、スプリアスとなる高調波を除去し、正弦波を生成することである。

【解決手段】本発明の信号生成回路の一態様は、第1の入力信号に基づき第1の信号を出力する第1の分周器1bと、第2の入力信号に基づき第2の信号を出力する第2の分周器1bと、第1の入力信号と第2の入力信号との間に第1の位相差φを与える第1の移相器2a、2bと、第1の信号と第2の信号とを合成し、出力信号を生成する合成回路3a〜3dと、を有し、第1の移相器2a、2bは、第1の信号において除去対象となる第1の高調波成分が、第1の信号と第2の信号との間で逆位相となる第1の位相差φを第1の入力信号に付加して第2の入力信号を生成する。

(もっと読む)

半導体集積回路装置及びクロックスキュー計測方法

【課題】クロックスキューをより正確に計測できる半導体集積回路装置及びクロックスキュー計測方法を提供する。

【解決手段】LSI100内部のクロック信号を入力するクロック入力端子1と、クロックスキューを計測するためのクロックスキュー計測信号を入力する計測信号入力端子2と、クロック信号とクロックスキュー計測信号とが入力される複数のF/F3と、計測信号入力端子2から複数のF/F3にクロックスキュー計測信号を分配する複数の計測信号分配ドライバ7と、を備え、複数のF/F3は、複数のF/F群5に分けられ、F/F群5内の全てのF/F3は、同一の計測信号分配ドライバ7と直接に信号線のみを介して接続され、複数のF/F3の出力信号に基づいて、複数のF/F3間におけるクロックスキューを計測するように構成した。

(もっと読む)

クロック分配回路およびそれを用いたインターフェース装置

【課題】データの伝送速度および信頼性の低下を防止できるようにしたクロック分配回路およびそれを用いたインターフェース装置を提供する。

【解決手段】入力されたクロックを制御電圧によって可変とされた遅延を有するようにして分配クロックとして出力する電圧制御分配手段、及び前記データと前記分配クロックの位相差を用いて前記制御電圧を生成する制御電圧生成手段を備える。

(もっと読む)

ASIC及び画像形成装置

【課題】 スイッチング電流(過渡的な貫通電流)等による瞬間の過渡電流が、内部配線を流れる事による配線からの電磁波の直接輻射、及びその結果生じる内部電源の電圧降下や、急激な電圧変化によって、その信号がIO出力端子に重畳され出力される事で生じる間接輻射による不要輻射が、無視できないレベルとなってきている。

【解決手段】 エーシック内部のクロックのスキュー調整を分散化させそのエーシックを用いたシステムでエーシックで不要輻射が生じないようにする。特に同一のクロック端子に接続されてその端子からのクロックスキューが互いに異なるブロックを少なくとも2つ以上形成させ互いにクロックオンするタイミングがことならせ少なくとも同じ電源ライン間に複数のブロックにまたがって配置してコンタクトで電源接続されていることを特徴とする。

(もっと読む)

集積回路電源ノイズ低減方法および集積回路電源ノイズ低減システム

【課題】 集積回路の電源から放出されるノイズを効率良く低減することができる集積回路電源ノイズ低減方法および集積回路電源ノイズ低減システムを提供すること。

【解決手段】 トランジスタが作動するときの貫通電流によって発生するIC1の電源ノイズを低減する集積回路電源ノイズ低減方法において、前記IC1のベースクロックに対して一定周期単位で位相を遅らせたディレイクロックを複数生成するクロック分散手順と、前記複数のディレイクロックにより動作する回路ブロックを複数の回路ブロック11,12,13,14に分割する回路ブロック分割手順と、各回路ブロック11,12,13,14により生成された位相のずれたノイズ波形と電源ノイズ波形を干渉させて電源ノイズを低減する電源ノイズ低減手順と、を有する。

(もっと読む)

クロック信号を発生するクロック発生回路及び方法

【課題】クロック信号を発生するクロック発生回路及び方法を公開する。

【解決手段】クロック発生回路は、外部クロック信号を直接受信して、反転された外部クロック信号を発生するインバータと、一番目のループ回路が反転外部クロック信号を受信してn(nは2以上の定数)個のノードをそれぞれ備え、M−1(Mは1以上の定数)個のループ回路のそれぞれがn個のノードの対応する1つからn個の中間内部クロック信号それぞれを発生し、n個の中間内部クロック信号の周波数が外部クロック信号及び反転外部クロック信号の周波数の倍数であることを特徴とする直列に配列されたM個のループ回路と、それぞれが直列に接続されて以前のループ回路から対応する中間内部クロック信号を受信し、対応する中間内部クロック信号を次のループ回路に出力するM−1個のインバータそれぞれと、を具備するn個のインバータの集合で構成されている。

(もっと読む)

クロックツリー合成装置、クロックツリー合成方法、制御プログラムおよび可読記録媒体

【課題】複数のクロック信号源と、複数のクロック信号源が各入力端子に接続された論理回路との各クロック出力について、同期関係を解析してクロックツリーを最良に生成する。

【解決手段】複数のクロック信号源と、この複数のクロック信号源が各入力端子に接続された論理回路との各クロック出力について、クロック同期関係解析手段10によって、同期関係を解析し、この解析結果に基づいて、クロックツリー構成手段20によって、クロックツリーを生成するため、クロックツリーを再構成することなく、クロックスキューを低減することができる。また、論理回路からクロックが供給されるクロック同期素子(フリップフロップ)が、どちらの信号源に同期して動作するかが分かるため、クロックスキューが小さく、消費電力が少ないクロックツリーを簡単に構成してタイミング違反による回路誤動作を防ぐことができる。

(もっと読む)

半導体集積回路のクロック構成方法およびそのプログラム

【課題】実際のデバイス上でのクロックスキューの増大を抑制し、オンチップばらつき耐性を強くする。

【解決手段】所定数のフリップ・フロップ(FF)を含む領域G1〜G8を2つの群に群分けする。このとき、境界線の横切るデータ接続経路の数が最小となるようにする。ここでは、データ接続経路A1、A2を横切るようにすると、境界線が横切るデータ接続経路数が2で最小となる。さらに、領域G1〜G4、領域G5〜G8を群分けした後に、クロックツリー合成(CTS)を行う。このようにしてクロック構成を行うことにより、実際のデバイス上でのクロックスキューの増大を抑制し、オンチップばらつき耐性を強くすることができる。

(もっと読む)

大規模半導体集積回路装置

【課題】各入力回路の位置に応じた適切な到達遅延時間を有する複数のクロックツリーを備えたことにより、動作周波数等の設計マージンが小さく、歩留まりの高い大規模半導体集積回路装置を提供することを目的とする。

【解決手段】同期回路を動作させるための基本クロックを発生させる原発振器と、CPUやメモリや特定用途用に構成されたロジック等を指す機能ブロックと、原発振器10で生成されるクロックを入力し、機能ブロックを駆動するクロックツリーと、機能ブロック間で情報の授受を行う非同期FIFO等で構成されるブロックである非同期I/Fブロック15と、を備えて構成し、各機能ブロックのLSI上の位置に応じて、クロックツリーの到達遅延時間を適切に設定する。

(もっと読む)

ワイドレンジクロック発生器

第1のクロック発生回路と、周波数分割回路と、複数のマルチプレクサとを有する、ワイドレンジ複数位相クロック発生器である。第1のクロック発生回路は、それぞれが、第1の周波数および複数の異なる位相角のうちのそれぞれ1つをそれぞれが有する複数の第1のクロック信号を生成する。周波数分割回路は、第1のクロック発生回路から、複数の第1のクロック信号を受信して、第2の周波数および複数の異なる位相角のうちのそれぞれ1つをそれぞれが有する複数の第2のクロック信号を生成する。マルチプレクサは、それぞれが、第1のクロック信号のうちのそれぞれ1つを受信するように結合された第1の入力と、第2のクロック信号のうちの、第1のクロック信号のうちの前記1つと実質的に同じ位相角を有するそれぞれ1つを受信するように結合された第2の入力とを有する。  (もっと読む)

(もっと読む)

1 - 11 / 11

[ Back to top ]