Fターム[5J039EE10]の内容

パルスの操作 (9,993) | パルス分配 (453) | 多相出力 (225) | 非同期駆動のもの (99) | 直列接続の出力段を持つもの (50) | 遅延線によるもの (39)

Fターム[5J039EE10]に分類される特許

1 - 20 / 39

半導体装置

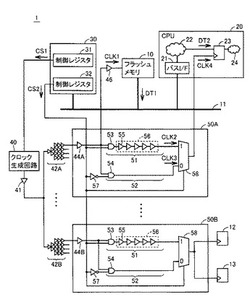

【課題】不揮発性メモリを備えた半導体装置において、高速動作の場合と低速動作の場合とに切替え可能にするとともに、低速動作時の消費電力を従来よりも削減する。

【解決手段】半導体装置1において、クロック生成回路40は、高周波モード時には低周波モード時よりも周波数の高いクロックを生成する。中央処理装置20は、データバス11を介して不揮発性メモリ10から読み出された読出データを取得する。クロック遅延部50Aは、縦続接続された複数段のバッファ55を介した第1の経路51と複数段のバッファ55を迂回した第2の経路52とを含む。クロック遅延部50Aは、高周波モード時には、クロック生成回路40からのクロックを第1の経路51を介して中央処理装置20に供給し、低周波モード時には、クロック生成回路40からのクロックを第2の経路52を介して中央処理装置20に供給する。

(もっと読む)

半導体装置及びこれを用いた情報処理システム

【課題】遅延回路の遅延量の最小値よりも短い相間隔を有する多相クロック信号を小さな回路規模で生成する。

【解決手段】縦列接続された遅延回路UD1〜UDnからなり、入力クロック信号IGCKをk周期遅延させるディレイラインと、遅延回路UD1〜UDnからそれぞれ出力される出力クロック信号Node1〜Nodenに基づいて互いに位相の異なる多相クロック信号DTCK1を生成するルーティング回路130とを備える。nとkの最大公約数をGCM、入力クロック信号IGCKの1サイクルをGCK、多相クロック信号DTCK1の相間隔をUIとした場合、相間隔UIの長さは、UI=GCK×GCM/nで与えられる。これにより、1個の遅延回路の遅延量の最小値よりも短い相間隔を有する多相クロック信号を小さな回路規模で生成することが可能となる。

(もっと読む)

CDR回路、受信装置、および通信システム

【課題】簡易な回路構成で、高速かつジッタ入力に強く、信号エラーの発生を抑止することが可能なCDR回路、受信装置、および通信システムを提供する。

【解決手段】CDR回路310は、遅延素子312−1〜312−4を含み、定期的に信号遷移の挿入されたデータ入力をトリガとしてクロックを抽出する分周器320と、分周器で抽出されたクロックに同期して入力データ信号をラッチするラッチ315−1〜315−8とを有する。

(もっと読む)

半導体設計装置

【課題】セットアップ違反やホールド違反を発生させずに、電力を消費するタイミングを分散させることができる半導体設計装置を提供する。

【解決手段】STA部5は、フリップフロップのクロックレイテンシの現在の設計値に基づいて、フリップフロップのセットアップ時間のマージンであるセットアップスラックを算出する。HSLD部6は、算出したセットアップスラックに基づいて、タイミング違反を起こさない範囲で、フリップフロップのクロックレイテンシを現在の設計値よりも早める方向に調整する。PAS部7は、HSLD部6によるレイテンシ制御の結果、クロックレイテンシ分布においてシンク数に閾値以上のピークが残る場合、HSLD部6による再計算後のタイミング情報により、タイミング違反を起こさない範囲で、フリップフロップのクロックレイテンシをスムージングする。

(もっと読む)

半導体集積回路のクロック遅延調整回路およびその制御方法

【課題】回路規模が増大する問題があった。

【解決手段】複数の回路ブロックと、入力するクロック信号を遅延制御信号に基づいて遅延したクロック信号を対応する前記複数の回路ブロックに供給する複数のクロック遅延回路と、前記複数の回路ブロックの遅延試験を行う制御回路と、前記遅延試験の結果に応じて、前記複数の回路ブロックのうち遅延処理が必要な回路ブロックの情報を記憶する救済グループ記憶回路と、前記遅延試験の結果に応じて、前記複数の回路ブロックのうち遅延処理が必要な回路ブロックの遅延値情報を記憶する、所定数の遅延設定回路と、前記救済グループ記憶回路が記憶した回路ブロックの情報に対応したクロック遅延回路に対し、前記遅延設定回路が記憶した遅延値情報に応じた前記遅延制御信号を割り当てる遅延設定割当制御回路と、を有する半導体集積回路のクロック信号調整回路。

(もっと読む)

クロック供給システム及び画像形成装置

【課題】SSCGの変調度を大きくすることなく、且つ低コストで、複数の電子部品から放射されるノイズを効果的に低減する。

【解決手段】一定周波数の第1クロック信号を生成する第1クロック生成器と、前記第1クロック信号の周波数変調を行うことで周期的に周波数が変動する第2クロック信号を生成する第2クロック生成器と、複数のクロック供給対象回路で使用される前記第2クロック信号の位相が、前記クロック供給対象回路毎に異なるように位相調整を行う位相調整回路とによってクロック供給システムを構成する。

(もっと読む)

デシリアライザ

【課題】PLL回路を用いずにクロックを同期させることを課題とする。

【解決手段】デシリアライザ部1は、PLL回路の代わりに、発振器2とクロック同期部10とを備える。クロック同期部10は、入力されたシリアルデータを段階的に遅延させることで異なる位相のデータを複数生成する。次に、クロック同期部10は、複数のシリアルデータそれぞれの位相と、発振器2によって発振されたクロックの位相とを比較する。そして、クロック同期部10は、比較結果に基づいて、発振器2によって発振されたクロックとの同期に適したシリアルデータを選択する。

(もっと読む)

オーバーサンプリング回路

【課題】オーバーサンプリング型CDR回路で用いる多相クロックの相互の位相差が等間隔になるように高精度に位相を補正できるオーバーサンプリング回路を提供する。

【解決手段】多相クロックを生成する多相クロック生成部200と、多相クロックの位相差を検出して、該検出結果に基づいて位相制御信号を発生する位相制御部205と、多相クロックの本数分の遅延回路を有し、多相クロックをそれぞれの遅延素子に入力された信号の通過時間を、位相制御信号に基づいて調整することで多相クロック間の位相差を調整する位相調整部203と、を備え、各遅延回路300は、直列に接続されたサイズの異なる複数のインバーターと、該複数のインバーターの後段に接続したインバーターと、からなり、複数のインバーターから選択される一つインバーターの出力抵抗と、後段に接続したインバーターの入力容量の積に基づいて通過時間を調整する。

(もっと読む)

非重複クロック生成のための技術

【解決手段】望ましい周波数範囲にわたって、正確な非重複時間及びクロックフェーズ遅延時間を生成する技術が提供される。一構成において、装置はそれに結合されるクロック生成回路への制御電圧を順に生成する遅延ロックループ(DLL)回路を含む非重複クロック生成回路を備えている。制御電圧はクロック生成回路によって生成される非重複遅延クロック信号の正確なタイミング関係を維持するように動作する。一態様において、DLL回路は知られたデューティサイクルによる入力クロックを受信し、入力クロックサイクルの特定の部分へのユニット遅延をフィックスする出力制御電圧を得る。更なる態様において、クロック生成回路は製造プロセス変化とは関係ない非重複時間(tnlp)でクロック信号の第1のセットから遅延されたクロック信号の第2のセット及びクロック信号の第1のセットを生成するDLL回路に結合される複数の電圧制御遅延セルを備えている。 (もっと読む)

論理回路におけるクロック分配のための遅延マッチング

【課題】論理回路におけるクロック分配のための遅延マッチング。

【解決手段】論理回路内部に分配された複数の信号間の伝播遅延差を補正するための技術。遅延マッチング回路は、フロップによって生成された内部のクロックからQへの遅延を模倣する。遅延マッチング回路は、再分配されようとしている、クロック信号のような原初の信号の伝播経路内に置かれる。一般に、遅延マッチング回路は、特定の構成を有する伝播ゲート・マルチプレクサを含むことができる。遅延マッチング回路は、原初の信号の分割された版により経験されたクロックからQへの遅延に実質的に等しい遅延を課する。このようにして、遅延マッチング回路は、原初の信号と分割された信号の立ち上がり端と立ち下がり端とが、実質的に一致することを確実にし、同期した動作を可能にする。これゆえ、遅延マッチング回路は、再分配された信号と分割された信号を同期させることができる。

(もっと読む)

ラッチ回路、フリップフロップ回路および半導体装置

【課題】ラッチ回路およびフリップフロップ回路のソフトエラー耐性の向上。

【解決手段】複数の回路ユニットIV1-IV4を有し、複数の回路ユニットの出力が他の反転回路の入力にフィードバックされ、2以上の入力端子1,2を有するデータ保持回路11と、2以上のクロックCK01,XCK01;CK02,XCK02にそれぞれ同期して、データ保持回路の2以上の入力端子に入力信号を入力する2以上の入力回路TG1,TG2と、を備え、データ保持回路は、2以上の入力端子に同時に入力信号Dinが入力されかつ2以上のクロックが同時に変化した時のみ、2以上の入力端子に正帰還がかかる。

(もっと読む)

多相クロック生成回路、オーバーサンプリング回路及び位相シフト回路

【課題】より位相差の微小な多相クロックを生成しつつ、消費電流の増大を抑制した多相クロック生成回路及びオーバーサンプリング回路を提供する。

【解決手段】1対の入出力端子と、遅延量制御端子にバイアスした電圧に応じた遅延量を発生させる2つの遅延ラインの出力の位相差を検出する位相比較器13と、位相比較器13の出力を平均化する平均化フィルタ14とを備え、一方の遅延量制御端子に基準電圧を接続し、他方の遅延量制御端子に平均化フィルタ14の出力を接続し各遅延ラインの出力が所定の位相差を持つように制御する遅延量制御部11と、複数かつ同数個の遅延素子を直列に接続した複数の遅延ライン21を備え、各遅延ライン21は基準電圧を接続した遅延素子22の数及び平均化フィルタ14の出力電圧を接続した遅延素子の数の組み合わせを異ならせたクロック遅延部20とを備え、所定の位相差を持つ多相クロックを生成する。

(もっと読む)

クロック信号生成装置および離散時間型回路

【課題】電源電圧、環境温度などの外部変動要因により、離散時間型回路において必要となるクロック信号に変動が生じた場合などにおいて、離散時間型回路が必要とするノンオーバーラップ時間、およびクロック信号のデューティ比を最適に設定することができるクロック信号生成装置を提供すること。

【解決手段】本発明のクロック信号生成装置において、クロック信号遅延算出部は、クロック信号生成回路の可変遅延回路における外部変動要因による遅延特性をモニターする遅延検出回路を有して、N相のクロック信号の遅延量を算出し、クロック信号遅延制御部は、遅延変動データ部に記憶されている外部変動要因をパラメータとした遅延変動データと、算出されたN相のクロック信号の遅延量とに基づいて、可変遅延回路における遅延量を可変するよう構成されている。

(もっと読む)

半導体メモリ装置及びその駆動方法

【課題】デューティ補正された遅延固定クロックを生成することができ、1つのDLLだけでもデューティ補正が可能で、かつ、入力されるクロック信号のデューティ比を効率的に補正して出力することができる半導体メモリ装置を提供すること。

【解決手段】遅延固定動作により遅延固定クロックを生成するDLL回路と、前記遅延固定クロックと、その遅延固定クロックの偶数倍に分周したクロックとを用いて、前記遅延固定クロックのデューティ比を補正するデューティ補正回路とを備える半導体メモリ装置を提供する。

(もっと読む)

半導体装置、半導体集積回路装置、及び許容位相差測定回路

【課題】低コストで電流ピークを効果的に抑制することができる半導体装置を得る。

【解決手段】ステップST1において、モジュールA21とモジュールB22とのクロック位相を一致させた後、ステップST2において、モジュールA21からモジュールB22にデータ転送を行う。その後、ステップST3において、モジュールA21のクロックCLKAとモジュールB22のクロックCLKBとのクロック位相差を所定の大きさに設定した後、ステップST4において、モジュールA21とモジュールB22とがそれぞれ独立に所定の演算処理を行う。そして、ステップST5において、モジュールA21のクロックCLKAとCPU25のクロックCLKPとの位相を一致させた後、ステップST6においてモジュールA21の演算結果をCPU25で読み取る。

(もっと読む)

半導体集積回路

【課題】半導体集積回路の外部入出力信号のタイミングを自動的に調整する。

【解決手段】半導体集積回路は、内部セルの動作クロック信号に同期して当該内部セルから出力されたデータ信号又は外部から入力されたデータ信号をラッチするフリップフロップ(10)を有する入出力セル(1)を備えている。

(もっと読む)

集積回路電源ノイズ低減方法および集積回路電源ノイズ低減システム

【課題】 集積回路の電源から放出されるノイズを効率良く低減することができる集積回路電源ノイズ低減方法および集積回路電源ノイズ低減システムを提供すること。

【解決手段】 トランジスタが作動するときの貫通電流によって発生するIC1の電源ノイズを低減する集積回路電源ノイズ低減方法において、前記IC1のベースクロックに対して一定周期単位で位相を遅らせたディレイクロックを複数生成するクロック分散手順と、前記複数のディレイクロックにより動作する回路ブロックを複数の回路ブロック11,12,13,14に分割する回路ブロック分割手順と、各回路ブロック11,12,13,14により生成された位相のずれたノイズ波形と電源ノイズ波形を干渉させて電源ノイズを低減する電源ノイズ低減手順と、を有する。

(もっと読む)

ASIC及び画像形成装置

【課題】 スイッチング電流(過渡的な貫通電流)等による瞬間の過渡電流が、内部配線を流れる事による配線からの電磁波の直接輻射、及びその結果生じる内部電源の電圧降下や、急激な電圧変化によって、その信号がIO出力端子に重畳され出力される事で生じる間接輻射による不要輻射が、無視できないレベルとなってきている。

【解決手段】 エーシック内部のクロックのスキュー調整を分散化させそのエーシックを用いたシステムでエーシックで不要輻射が生じないようにする。特に同一のクロック端子に接続されてその端子からのクロックスキューが互いに異なるブロックを少なくとも2つ以上形成させ互いにクロックオンするタイミングがことならせ少なくとも同じ電源ライン間に複数のブロックにまたがって配置してコンタクトで電源接続されていることを特徴とする。

(もっと読む)

可変周波数多相発振器

【課題】簡単なデューティサイクル制御と、広い周波数レンジと、簡単な周波数調整構成と、低消費電力を備え、集積回路に組み込まれ、且つ、その集積回路を複雑にすることのない多相出力を有する可変周波数多相発振器を提供する装置および方法を提供すること。

【解決手段】多相信号を供給するための可変周波数多相発振器が開示される。この可変周波数多相発振器は、相関器、複数の遅延セル、およびNOR回路を備える。上記相関器のそれぞれは、電流供給部、キャパシタ、コンパレータ、スイッチ、及び論理ユニットを備える。上記複数の遅延セルは、大きな周波数レンジの範囲内で相が相関性を有する多相信号を発生させる。上記多相信号の周波数とデューティサイクルは調整可能である。

(もっと読む)

EMIノイズを低減した同期回路の設計方法

【課題】 どの場所にどれだけスキューを付けられるかを検証して、消費電流が流れるタイミングを時間軸上で分散させることで、EMIのいずのピークを低減することができる同期回路の設計方法を提供すること。

【解決手段】 本発明に係る同期回路の設計方法は、ネットリストを含む所与の条件を入力して、自動配置配線ツールを用いて同期回路の一次配置配線を実施する第1工程と、配置配線された同期回路のクロックツリーに従って、クロックソースから各末端経路までのクロックの到達時間差であるスキューを解析する第2工程と、解析されたスキューがセットアップ/ホールドタイムに対してマージンを有する複数のモジュールI,II,III,IVに分割する第3工程と、分割された複数のモジュールI,II,III,IVの少なくとも一つにクロックスキュー設定回路10を追加挿入する第4工程と、クロックスキュー設定回路10を追加して、二次配置配線を実施する第5工程と、を有する。

(もっと読む)

1 - 20 / 39

[ Back to top ]