Fターム[5J039EE19]の内容

Fターム[5J039EE19]に分類される特許

1 - 5 / 5

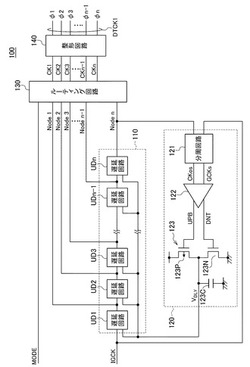

半導体装置及びこれを用いた情報処理システム

【課題】遅延回路の遅延量の最小値よりも短い相間隔を有する多相クロック信号を小さな回路規模で生成する。

【解決手段】縦列接続された遅延回路UD1〜UDnからなり、入力クロック信号IGCKをk周期遅延させるディレイラインと、遅延回路UD1〜UDnからそれぞれ出力される出力クロック信号Node1〜Nodenに基づいて互いに位相の異なる多相クロック信号DTCK1を生成するルーティング回路130とを備える。nとkの最大公約数をGCM、入力クロック信号IGCKの1サイクルをGCK、多相クロック信号DTCK1の相間隔をUIとした場合、相間隔UIの長さは、UI=GCK×GCM/nで与えられる。これにより、1個の遅延回路の遅延量の最小値よりも短い相間隔を有する多相クロック信号を小さな回路規模で生成することが可能となる。

(もっと読む)

多相クロック発生回路、及び多相クロック発生方法

【課題】回路規模の増加を抑えかつ出力信号のジッタ特性を低下させずに、複数の動作周波数に対応できる多相クロック発生回路を提供する。

【解決手段】多相クロック発生回路は、位相の異なる複数のリファレンスクロック信号が入力され、該リファレンスクロック信号が取り得る複数の周波数ごとに設けられた遅延パスであって該リファレンスクロック信号に対して予め定められた位相差を生じさせる複数の遅延パスと、リファレンスクロック信号の周波数に基づいて、複数の遅延パスのうち、リファレンスクロック信号の周波数に対応する遅延パスを選択するスイッチ部と、スイッチ部が選択した遅延パスにより、位相差が変更された複数のリファレンスクロック信号から所定の位相差を有する複数のクロック出力信号を生成する位相補間回路とを備える。

(もっと読む)

多相クロック発生回路

【課題】位相補間回路を広帯域な動作周波数で性能良く使用するのは困難であった。

【解決手段】多相クロック発生回路10は、位相の異なる複数のリファレンスクロックから位相補間を用いて任意位相の多相クロックを生成する。位相選択回路12は、制御信号に応じてスルー・レイトが変化する可変スルー・レイト回路である。位相補間回路13-1、13-2は、位相選択回路12を通じて入力される互いに90°位相の相違する2つのリファレンスクロックを補間して中間の位相の出力クロックを生成する。

(もっと読む)

半導体デバイスおよびディスプレイ装置

【課題】クロック信号の復帰時に発生する誤動作を防止する。

【解決手段】クロック分配回路10は、クロック信号CKを受け、複数の経路P1〜P3に分配する。デジタル回路30は、複数の経路P1〜P3に対応づけられた複数の領域R1〜R3に分割されている。各領域R1〜R3が共通の電源電圧Vddを受ける。また各領域R1〜R3はクロック分配回路10により分配されたクロック信号CK1〜CK3と同期動作する。クロック分配回路10は、クロック信号CKが非入力状態から入力状態に遷移するとき、複数の経路P1〜P3それぞれに対して、時間差を付けてクロック信号を分配する。

(もっと読む)

半導体集積回路

【課題】複数の順序回路として少なくともレベルセンス型順序回路を用いたシステムにおいて、動作周波数を高めると共に、信頼性を向上させる。

【解決手段】マイクロコンピュータ(1)は、クロック供給元とされるクロック発生回路(2)と、クロック信号CLKに同期動作する機能モジュールと、機能モジュールに含まれ、クロック供給先とされるレベルセンス型順序回路(12〜14)と、クロック信号をレベルセンス型順序回路に伝播するクロック供給系(11)等とを備える。クロック供給系は、クロック発生回路から出力されるクロック信号を複数の分岐を介して末端に伝播するクロック配線(20)を有する。クロック配線の途中には、少なくともパルス生成回路(26,28,29)が配置される。パルス生成回路は、レベルセンス型順序回路の入力動作期間の終点を規定するクロック信号の立ち下がりエッジの変化タイミングを可変とする。

(もっと読む)

1 - 5 / 5

[ Back to top ]