Fターム[5J039NN03]の内容

Fターム[5J039NN03]に分類される特許

1 - 8 / 8

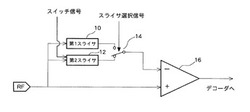

二値化回路

【課題】RFアナログ信号に直流成分が含まれていても正しく二値化する。

【解決手段】光ディスクから読み取ったRFアナログ信号をコンパレータ16でスライスレベルと比較することで二値化する。第1スライサ10はRFアナログ信号のピークレベルとボトムレベルの平均値をスライスレベルとして出力し、第2スライサ12は信号列の連続したパターンの部分におけるピークレベルとボトムレベルの平均値をスライスレベルとして出力する。切替スイッチ14でスライスレベルを切り替えて出力する。

(もっと読む)

半導体メモリ装置及びその動作方法

【課題】半導体メモリ装置においてCMLレベルでスイングするクロックが伝送される経路を多重化することによって、動作モードに関わらず消費する電流量を常に最小に維持することのできる半導体メモリ装置を提供する。

【解決手段】本発明の半導体メモリ装置は、イネーブル信号に応答してCMLソースクロックがクロック伝送ラインを介して伝達された後にCMOSレベルでスイングするよう変換して出力する第1クロック伝達パスと、イネーブル信号に応答してソースクロックをCMOSレベルでスイングするよう変換した後にクロック伝送ラインを介して伝達されて出力する第2クロック伝達パスと、第1クロック伝達パス及び第2クロック伝達パスの出力クロックに応答してデータを出力するデータ出力手段と、を備える。

(もっと読む)

ピークホールド回路

【課題】高速動作に適し、且つピーク検出の精度を向上できるピークホールド回路を提供する。

【解決手段】第1ピークホールド回路20aは、入力信号Vinが供給される入力トランジスタQ1と、入力信号Vinのピーク値をホールドするコンデンサC1と、コンデンサC1の保持電圧が供給されるオペアンプ26と、補正用トランジスタQ2とを備える。また、入力トランジスタQ1に流れる電流を検出する電流検出回路30と、電流検出回路30において検出された電流のピーク値をホールドし、電流Ipとして補正用トランジスタQ2に供給するピーク電流ホールド回路35とを備える。

(もっと読む)

電子回路、情報再生装置

【課題】 セットアップ違反に対するより一般的な検出技術を提供する。

【解決手段】 外部からの入力データを受ける第1のフリップフロップと、前記入力データを受けるラッチと、このラッチの出力と前記第1のフリップフロップの出力との排他的論理和を入力する第2のフリップフロップとを備えた電子回路。また前記第1のフリップフロップの出力を入力とし前記第2のフリップフロップの出力に基づく通知信号を抑制信号入力として用いる電子回路を具備した情報再生装置。

(もっと読む)

半導体装置

【課題】 基準電圧が入力される増幅回路内のトランジスタにおいて製造プロセスの変動に起因する閾値の変動が生じた場合に外部入力信号に対して高速な出力を得られる半導体装置を提供する。

【解決手段】半導体装置1は、外部電源電圧Vccと接地電圧Vssとを供給され、外部電源電圧Vccを基に基準電圧Vrefを生成する基準電位発生回路2と、外部電源電圧Vccと接地電圧Vssとを供給され、前記基準電位発生回路2で生成される前記基準電圧Vrefと外部入力信号Vinの電圧とを比較してその比較結果に応じて出力信号Voutを生成する増幅回路3と、前記基準電圧Vrefを調節するためのデータが記憶された記憶回路4とを有する。

(もっと読む)

個々のパルスの調節可能な開始時点および終了時点を有するパルス列を形成する方法とパルス発生器

【課題】個々のパルスの調節可能な開始時点および終了時点を有するパルス列を形成する改善された方法を提供する。

【解決手段】第1のクロック信号および第2のクロック信号それぞれ1つずつからなる組を提供し、1つの組の第1のクロック信号および第2のクロック信号の特性からタイミングベクトルに従い部分パルスを形成し、パルス列を部分パルスの重畳によって形成する。

(もっと読む)

ギガヘルツ周波数に効率的な遅延同期ループを有する多重位相クロック発生器を備える光学駆動回路

【課題】800MHzまたはそれ以上の周波数を有する入力クロックから、32個の異なる位相を発生させうる遅延同期ループ基盤の多重位相クロック発生器回路を備える光学(ディスク)駆動システムを提供する。

【解決手段】Nで分周されたクロックを、フィードバックループ内のM個の電圧制御される第1遅延素子に出力するための周波数分周器を有する遅延同期ループを備え、分周されていないクロックを遅延させて、M個の多重位相クロックを出力するために、フィードバックループの外部に同じM個の電圧制御される遅延素子を更に備える多重位相クロック発生器。光学駆動システムの光学駆動回路と、光学ディスク上の隣接する溝に書き込まれるマークの重複を防止するための書き込みストラテジを行う方法とを提供し、該回路及び方法は、GHzの周波数範囲で高解像度(例えば、T/32)でスイッチングする多重の書き込みストラテジ波形(チャンネル)を生成する。

(もっと読む)

信号検出回路

【課題】 高速信号に対応し、精度良く差動信号の検出が可能であり、回路のレイアウト面積を縮小し、消費電力を低減することができる。

【解決手段】 本発明による信号検出回路は、2つある差動比較回路の一方にオフセット調整回路抵抗Rb1を持たせ、一方の差動比較回路からの差動出力信号にオフセット電圧Voffを与え、2つの差動比較回路の逆相出力によって形成される差動出力信号を差動排他的論理和回路EOR3へ入力し、排他的論理和を出力して、オフセット調整回路抵抗Rb1で設定したレベル以上の差動入力信号を検出する。

(もっと読む)

1 - 8 / 8

[ Back to top ]