Fターム[5J042CA06]の内容

Fターム[5J042CA06]に分類される特許

1 - 8 / 8

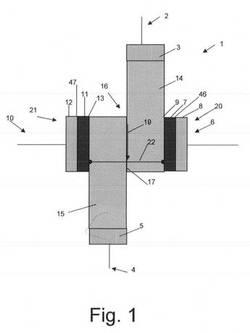

トンネルトランジスタ、トランジスタを含む論理ゲート、論理ゲートを使用するスタティックランダムアクセスメモリ、およびトンネルトランジスタの製造方法

【課題】第1、第2ゲートを有するトンネルトランジスタで、第1、第2のゲート間の電圧の差がより小さい場合にしようできるトンネルトランジスタを提供する。

【解決手段】ドレイン2、ソース4およびドレイン2とソース4との間で電流を制御するための少なくとも第1ゲート6とを含み、第1および第2のゲート誘電体材料7、11の第1側9、13が、それぞれ第1および第2の半導体部分14、15に実質的に沿って、実質的に接続して配置されたトンネルトランジスタ1。

(もっと読む)

多値記憶手段、多値バッファ手段および双方向性スイッチング手段

【課題】C・MOS・FET等の相補型3端子スイッチング手段を用いたオン・オフ駆動手段も使用できる双方向性スイッチング手段を提供する。

【解決手段】どちらも両主電極の役割がその印加電圧の方向により互いに入れ換わることができ、どちらも互いに相補関係に有る2つのオン・オフ制御スイッチング手段が有って、その両オン・オフ制御スイッチング手段のうち一方の主電極と他方の主電極を接続し、一方の開放された主電極と一方の制御電極の間に一方のオン・オフ駆動手段を設け、一方の開放された主電極と他方の制御電極の間に他方のオン・オフ駆動手段を設け、その両オン・オフ制御スイッチング手段の直列回路を双方向性のスイッチとして使用する。

(もっと読む)

論理回路および論理集積回路

【課題】論理和回路の後段に接続される電子回路でのデューティ比の変動を抑制でき、雑音や電源電圧変動あるいは温度変動に対しても、後段に接続される電子回路を安定に動作させる。

【解決手段】複数の論理信号(X0、X1、X2)入力に対し、すべての論理信号およびそれぞれの否定の組み合わせについての論理積回路群10と、この論理積回路群10の出力する論理積信号からあらかじめ設定された組み合わせでの第1の論理和回路21、22と、論理積回路群10の出力する論理積信号のうち、第1の論理和回路21、22が論理和を求める対象としていない論理積信号について、その論理和を求める第2の論理和回路23、24を有し、第1の論理和回路21、22の出力する論理和信号(Z0、Z1)と第2の論理和回路23、24の出力する論理和信号(Z0、Z1の否定)とが差動回路31、32の差動入力とされる。

(もっと読む)

並列に給電される多数の同一基本回路を含む集積回路

本発明は、1からNまで変化するそれらの順位jの順番に並列に置かれたN個の同一な基本回路(CE1,CE2,...CEN)の連続を備え、Nは少なくとも50に等しく、2つの導体(CA及びCB)により供給される、2つの基準電位Vref及びV0を全てが受ける必要がある集積回路に関する。第2導体の上流側入力は、並列に置かれた回路の連続の順位1の側に地理的に位置し、第1導体の上流側入力は、並列に置かれた回路の連続の順位Nの側に地理的に位置する。これは回路の連続に全て沿った基本回路に印加される電位差における、導体の非ゼロ抵抗から由来する誤差を減らす。

高い分解能(10ビット以上)を有するアナログ−デジタル(AD)変換器、又はデジタル−アナログ(DA)変換器への適用

(もっと読む)

信号制御回路及び信号制御方法

【課題】 オープンドレイン形式又はオープンコレクタ形式の出力バッファの出力信号線を用いて、効率的なデータ転送を実現する。

【解決手段】 本発明は、オープンドレイン形式又はオープンコレクタ形式の出力バッファの出力信号線の状態制御に関する。本発明は、出力信号線の電位を監視し、出力信号線の電位が、低電位状態から高電位状態に遷移したことを検出する手段と、出力バッファに論理信号を供給し、供給する論理信号の変化によって、出力信号線の電位が低電位状態から高電位状態に遷移を開始した後、出力信号線が高電位状態に遷移したことが検出されると、この遷移の検出がされた時点に応じて、出力信号線を高電位状態に保持する期間の終点を調節し、高電位状態の保持期間として所定の最小期間以上を確保する手段とを有すること特徴とする。

(もっと読む)

プログラマブル論理回路

【課題】配線の複雑化なく、短時間かつ容易に、論理の再構成を行う。

【解決手段】本発明の例に関わるプログラマブル論理回路は、第1の電源ノードN1と出力ノードO1との間に接続され、磁気固着層と磁気記録層の磁化方向の相対関係に応じてコンダクタンスが変化する第1のトランジスタSPと、第2の電源ノードN2と出力ノードO1との間に接続され、第1のトランジスタSPのコンダクタンスの最大値と最小値との間の値にコンダクタンスが設定される第2のトランジスタSNと、第3の電源ノードN3と出力ノードO1との間に直列接続される第3のトランジスタT1及び抵抗素子R1とを備える。入力信号A,Bを与え、かつ、第1及び第3の電源ノードN1,N2の間にスピン注入電流を流している状態で、出力ノードO1に出力される出力信号Yの検証を行う。

(もっと読む)

エクスクルーシブOR回路

【課題】エクスクルーシブOR回路をPLL回路の位相比較器として使用した場合に誤動作をなくする。

【解決手段】トランジスタQ1,Q2で構成される第1の差動回路のトランジスタのコレクタ端子が、論理振幅を発生させるための負荷抵抗R1,R2に接続される。トランジスタQ3のエミッタ端子が、第1の差動回路とエミッタ端子と共通となるように接続され、コレクタ端子は負荷抵抗R1に接続される。負荷抵抗R1,R2は電圧源9に、トランジスタQ1,Q2,Q3の共通エミッタ端子は電流源10に接続される。このような構成の第1の論理回路20と同構成の第2の論理回路21が2段並列に接続される。1〜4は入力端子、5〜8は出力端子である。

(もっと読む)

出力回路

【課題】 オンラインダウンロード機能を備える出力部の2つの入力端子の電圧が互いに相関がない電圧で決定されるので、起動時の突入電流が大きい。この突入電流を小さくするために定常状態での出力部の電圧を0Vにしていたが、過渡的にマイナス電位になるために寄生トランジスタをオンしてしまうという課題を解決する。

【解決手段】 ダウンロード切替デジタル信号でスイッチをオン・オフして一端が基準電位に接続された時定数回路内のコンデンサを充放電する時定数回路の出力を出力部の一方の入力端子に入力して、出力部の他方の入力端子に前記基準電位を印加するようにした。出力部の入力誤差が小さくなるので、これによる過大な突入電流が流れることはない。そのため、定常状態における出力部の電圧を自由に選ぶことができるので、寄生トランジスタをオンさせることもなくなる。

(もっと読む)

1 - 8 / 8

[ Back to top ]