Fターム[5J049AA22]の内容

Fターム[5J049AA22]に分類される特許

1 - 10 / 10

波形発生器及びそれを備えた信号発生装置並びに波形発生方法及び信号発生方法

【課題】各ビットデータの周波数オフセットの発生を低減しつつ、波形パターン列の接続部の位相を連続にすることができる波形発生器及びそれを備えた信号発生装置並びに波形発生方法及び信号発生方法を提供する。

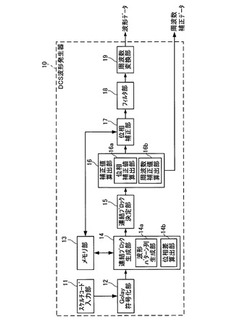

【解決手段】DCS波形発生器10は、波形パターンのブロックデータを生成するGolay符号化部12と、メモリ部13の記憶容量の範囲内で記憶可能な個数だけ波形パターンのブロックデータを連結した波形パターンブロック列を生成する波形パターン列生成部14aと、波形パターンブロック列の先頭の波形パターンのブロックデータから位相差が最小となる波形パターンのブロックデータまでを生成波形データとして決定する連結ブロック決定部15と、接続部位相差をゼロにする分配位相補正値を算出する位相補正値算出部16aと、周波数オフセットを算出する周波数補正値算出部16bと、を備える。

(もっと読む)

半導体試験装置および半導体試験方法

【課題】レート信号が高速になった場合でも、タイミングエッジ発生回路のタイムラグの影響を抑制して、試験速度の高速化を図ることを目的とする。

【解決手段】DUTの試験を行うための波形を発生させる半導体試験装置1は、それぞれ異なるタイミングをタイミングデータとして記憶し、1周期の間に波形を変化させる最大回数分の個数を設けた複数のタイミングメモリ10と、レート信号を基準としてタイミングデータのタイミングでタイミングエッジを発生し、タイミングメモリよりも多くの個数を設けた複数のタイミングエッジ発生回路11と、任意のタイミングメモリから任意のタイミングエッジ発生回路11にタイミングデータを入力させるマトリクス回路5と、タイミングエッジ発生回路11が発生したタイミングエッジに基づいて波形を出力する波形出力部6と、を備えている。

(もっと読む)

準固定回路

【課題】スクランブラ等の同じ機能の回路であっても、異なる種類の回路を1つの回路で実現することができる準固定回路を提供することである。

【解決手段】複数種類のCRC(Cycle Redundancy Check)回路の複数ビット同時処理が可能である準固定回路であって、複数のフリップフロップと、第1の入力ビット信号及び前記複数のフリップフロップの出力信号を基に選択的に排他的論理和を演算し、シフト1回目に相当する出力信号を出力するための第1の排他的論理和回路と、第2の入力ビット信号及び前記シフト1回目に相当する出力信号を基に選択的に排他的論理和を演算し、シフト2回目に相当する出力信号を出力するための第2の排他的論理和回路とを有する準固定回路が提供される。

(もっと読む)

ノイズ生成装置及びノイズ生成方法

【課題】ハードウェアによるノイズ発生処理を容易にし且つ処理部へのノイズデータの供

給速度を向上するのに好適なノイズ生成装置、ノイズ生成システム及びノイズ生成方法を

提供する。

【解決手段】ノイズ生成システム2を、ノイズ発生源10と、ノイズデータ生成装置20

とを含んだ構成とし、ノイズ発生源10は、比較的再現性の周期が長い乱数を発生する第

1の擬似乱数発生方法を用いて作成された第1のノイズデータを出力し、ノイズデータ生

成装置20は、ノイズデータ発生源10から、画素数Nの画像データの画素毎に、各画素

の各色に対応したn個の画素データに対して、1つの第1のノイズデータを取得する。更

に、前記取得した1つの第1のノイズデータに基づき、前記第1の擬似乱数発生方法より

も単純なアルゴリズムの第2の擬似乱数発生方法を用いて、n個以上の第2のノイズデー

タを生成し、当該生成した第2のノイズデータを画像処理部4に出力する。

(もっと読む)

データ発生装置

【課題】トリガ信号の到着から、実質的なデータ出力開始までの時間を安定させる。

【解決手段】メモリ54は、分周クロックD_CLKに従って並列データを供給する。アドレス・カウンタ52は、トリガ信号が到着するまでは同じアドレスをメモリ54供給し、トリガ信号が到着するとアドレスを進める。16進カウンタ62は、分周クロックよりも高速なクロックCLKをカウントし、分周クロックの周期毎にカウント値が循環する。トリガ情報ラッチ64は、トリガ信号を受けたときのカウンタ62のカウント値をラッチし、MUX58に供給する。MUX58は、ラッチ・カウント値に応じて、第1及び第2入力端子第1及び第2入力端子I1及びI2に入力された合計32ビットの並列データから、選択的に16ビットの並列データを生成する。並直列変換回路60は、MUX58からの組み替え並列データをクロックCLKに従って直列データに変換する。

(もっと読む)

乱数生成装置及び乱数生成方法

【課題】物理的条件や製造誤差によっても周期性を有さない乱数生成を行う。

【解決手段】抵抗とコンデンサとコイルと非線形受動素子とが接続されて発振回路を構成すると共に、前記抵抗とコンデンサとコイルの内少なくとも1素子の値を可変する素子値変更手段を備えたアナログカオス回路10と、前記アナログカオス回路10へ入力信号を供給する信号源20と、前記アナログカオス回路10の出力を所定周期にて取り出しディジタル化して下位側所定ビットを抽出する抽出部30と、前記抽出部30により抽出された所定回分のビットを並べて乱数とする乱数構成部40と、前記抽出部30の抽出周期に同期して前記素子値変更手段を制御し、素子値の変更を行う変更制御手段50とを具備する。

(もっと読む)

データ発生装置

【課題】トリガ信号に応じたデータ出力開始のタイミングを安定させる。

【解決手段】トリガ検出回路8は、トリガ信号と基準クロックの位相関係を示す位相情報を生成する。データ・パターン発生回路10では、トリガ信号に応じて、基準クロックに従って並列データを発生する。データ・シフト回路11は、位相情報に応じて、並列データ中のデータを所定順序に従って基準クロックに対してシフトしたシフト並列データに変換する。並直列変換回路16は、シフト並列データを直列データに変換する。

(もっと読む)

電子回路の動作安定化方法及びその電子装置

電力消費の低減のため、動作信号が到来しないと動作しない対象回路(10)を、定期的に動作させ続けるための動作信号発生回路(12,16)を設け、対象回路(10)をダミー動作する。対象回路(10)に含まれる回路素子の動作に影響する環境要因による影響を、安定あるいは均衡化させた状態で保持することが可能になり、消費電力を低減しつつ、実際の対象回路の動作時に安定かつ正確な動作が可能となる。  (もっと読む)

(もっと読む)

RTS生成回路

【課題】 受け渡しするデータの取りうる値が2のべき乗でないときもレーシングの影響を排除する。

【解決手段】 M分周カウンタ1はクロックfnxにより駆動されM個の数値を出力する。エンコーダ2はM分周カウンタの出力値を“1”の位置によって表現するMビットの値に変換する。演算回路3はエンコーダの出力にモジュロ2の演算を行う。D型FF4は演算回路の出力をクロックfsでラッチする。D型FF5はD型FF4の出力をユーザクロックでラッチする。デコーダ6はユーザクロックに同期してD型FF5の出力をエンコーダの出力値に戻す。N分周カウンタ7はfsで駆動されNカウントするとラッチ信号を出力する。D型FF8はこのラッチ信号でデコーダ6の出力をラッチする。

(もっと読む)

波形のシーケンスの生成

主シンボルシーケンスを生成し、シーケンス内の各シンボルをランダムに選択された波形に置き換えることにより、波形のシーケンスを生成する。主シンボルシーケンスは、狭い自己相関関数を有し、パルスの列であってもよく、それらパルスは、所定の構成のパケット内に配置される。波形を送信し、送信波形の表現を形成し且つその表現を遅延させ、その表現を、送信波形の反射の結果として受信される信号と相関させることにより、物体を検出することができる。 (もっと読む)

1 - 10 / 10

[ Back to top ]