Fターム[5J055EX22]の内容

Fターム[5J055EX22]に分類される特許

1 - 9 / 9

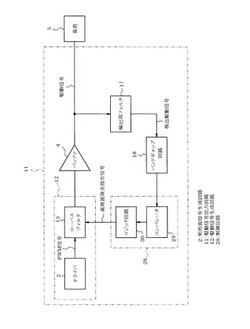

駆動信号出力回路

【課題】負荷、電源などの動作条件が変化しても、電磁妨害等を引き起こす周波数帯域の成分が除去された駆動信号を出力する。

【解決手段】負荷5に与えられる駆動信号をハイパスフィルタまたはバンドパスフィルタからなる検出用フィルタ17を介して検出し、その検出駆動信号をバンドギャップ回路18に入力する。バンドギャップ回路18は、固有の周波数特性を有し、検出駆動信号に固有の周波数帯域内の周波数成分が含まれていると出力電圧が低下する特性を持つ。制御回路28は、バンドギャップ回路18の出力電圧を基準電圧と比較し、検出駆動信号に固有の周波数帯域内の信号成分が含まれるか否かを判定する。含まれる場合には、ローパスフィルタ13により駆動信号から当該周波数帯域内の信号成分を除去する。

(もっと読む)

ゲートドライブ回路

【課題】ワイドバンドギャップ半導体からなるスイッチング素子の回生動作時の電力損失を抑制し、かつ、安定してターンオン/オフさせることができるゲートドライブ回路。

【解決手段】制御回路とスイッチング素子Q1のゲートとの間に接続され、コンデンサC1と抵抗R1とダイオードD1からなる直列回路と、スイッチング素子のゲートとソースとの間にPNP型トランジスタQ2が抵抗R2を介して接続され、トランジスタQ2のコレクタ・ベース間にダイオードD2が接続され、さらにトランジスタQ2のベースはダイオードD1のアノードに接続され、制御回路からのオフ信号が入力されると、トランジスタの接合電圧とダイオードD2との順方向電圧との差分電圧を残してゲートとソースとの間を短絡する。

(もっと読む)

電力用半導体素子の駆動保護回路

【課題】電力用半導体素子の制御電極の短絡動作時の電圧を通常動作時の電圧と同じ値に制限し、安全で確実な遮断を行うことが可能な電力用半導体素子の駆動保護回路の提供を目的とする。

【解決手段】本発明の電力用半導体素子の駆動保護回路は、電力用半導体素子F1と、その制御電極を駆動する駆動回路と、電力用半導体素子F1の制御電極の電圧Vgeが一定値を超えないよう制限する電圧保護回路とを備える。電圧保護回路は、電力用半導体素子F1の制御電極にエミッタが接続されたゲート放電用トランジスタTr1と、ゲート放電用トランジスタTr1にベース電位を与える電圧発生回路B1とを備え、電圧発生回路B1は、電力用半導体素子F1の駆動正電源電圧VDDから、前記駆動回路における電圧降下ΔV1を超える電圧が電力用半導体素子F1の制御電極に印加されたときに、ゲート放電用トランジスタTr1がオンできる電圧を出力する。

(もっと読む)

ゲート駆動回路

【課題】回路面積および製造コストの増大を招くことなく、ゲート電圧をクランプ値に収束するまでの応答時間を短くすることができるゲート駆動回路を提供する。

【解決手段】トランジスタQ11に過電流が流れる異常が生じると異常検出信号SaがHレベルになり、スイッチS11がオンする。その状態において信号線L13、L12間の電位差がクランプ値を超えて上昇しようとすると、ツェナーダイオードD11が降伏し、その降伏電流の大部分が増幅用トランジスタT12のベース電流となる。増幅用トランジスタT12の増幅作用によって、降伏電流を増幅した電流がクランプ用トランジスタT11のベースに供給される。クランプ用トランジスタT11は、供給されるベース電流に応じたコレクタ電流を信号線L11、L12間に流す。これにより、信号線L11、L12間の電位差が低下する。

(もっと読む)

スイッチ素子駆動回路

【課題】小型化及びコストダウンを図ることができるスイッチ素子駆動回路を提供する。

【解決手段】スイッチ素子駆動回路10は、スイッチ素子1のゲート電極1gに二次巻線n2が接続されたトランス11と、トランス11の一次巻線n1に電流が流れるオン期間と一次巻線n1に電流が流れないオフ期間を交互に設けて、スイッチ素子1をオン/オフさせる制御回路12を備える。制御回路12は、オン期間に一次巻線n1に流れる電流に基づいて、スイッチ素子1に接続された負荷状態をモニタし、負荷状態に応じて二次側に供給する出力を制御する。

(もっと読む)

リセット回路及び電子装置

【課題】本発明は、パワーオンした瞬間に生じる雑音を除去することができる静音制御回路及び該静音制御回路を有する電子装置を提供することを目的とする。

【解決手段】本発明に係る電子装置は、処理ユニット、静音制御回路、オーディオアンプ及びオーディオ出力インターフェースユニットを備え、前記オーディオアンプは、前記電子装置が生成するオーディオ信号を増幅し、且つ増幅されたオーディオ信号を前記オーディオ出力インターフェースユニットに出力し、前記処理ユニットは、静音制御信号を出力し、前記静音制御回路は、前記静音制御信号によって前記オーディオアンプを制御して静音状態と再生状態との間で切替させるメイン回路と、前記電子装置にパワーオンした瞬間、前記オーディオアンプの出力を接地により釈放させて、前記オーディオアンプと前記オーディオ出力インターフェースユニットとの間の通信を切る補助回路と、を備える。

(もっと読む)

ゲート駆動回路

【課題】MOS−FETを確実にオフさせることができ、かつ、複雑な構成を追加することのない、ゲート駆動回路を提供する。

【解決手段】パワーMOS−FETを駆動するためのゲート駆動回路において、前記MOS−FETのゲート端子に第1の抵抗を介してオンさせるための電圧を印加する第1のスイッチング素子と、前記MOS−FETのゲート端子に第2の抵抗を介してオフさせるための電圧に接続させる第2のスイッチング素子とを備え、前記第1の抵抗の抵抗値は前記第2の抵抗の抵抗値よりも大きく設定されているものである。

(もっと読む)

出力トランジスタの駆動制御装置

【課題】台形波電圧信号に基づき出力トランジスタを駆動して通信信号を送信する構成において、出力トランジスタを動作させる必要がない場合は確実にOFFにできる駆動制御装置を提供する。

【解決手段】トランシーバIC20において、駆動回路34を構成するカレントミラー回路33のトランジスタQ13側には、出力トランジスタQ14のベースを接続すると共に台形波電圧信号を印加し、カレントミラー回路33を構成するトランジスタQ11にベース電流を供給する定電流回路35を通信線3上にハイレベル信号を出力する場合はOFFさせる。

(もっと読む)

リセット信号出力回路を備えた電子機器

【課題】電子機器において、起動時等における電源電圧をモニタして、適宜リセット信号を出力するための部品を別途追加することなく、リセット信号出力回路を安価に構成し、機器のコストダウンを図る。

【解決手段】温度信号出力回路5に用いられているICに含まれる余剰のコンパレータを用いて、リセット信号出力回路4のコンパレータ10,20を構成する。コンパレータ10の−入力端子には抵抗R11,R12によってVcc1を分圧して得た所定電圧V1を、+入力端子には抵抗R21,R22によってVcc2を分圧して得た所定電圧V2をそれぞれ印加する。さらに、+入力端子に接続したコンデンサCによって+入力端子の電圧変動を遅延させ、Vcc1が十分に安定するまでコンパレータ10が制御回路2にローのリセット信号を継続して出力し、制御回路2の動作を停止させる。

(もっと読む)

1 - 9 / 9

[ Back to top ]