Fターム[5J056AA28]の内容

論理回路 (30,215) | 回路の種類 (3,583) | インターフェース、レベルシフト、レベル変換 (1,016) | 信号線 (3)

Fターム[5J056AA28]に分類される特許

1 - 3 / 3

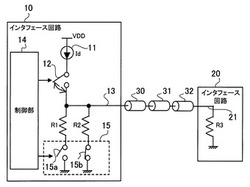

インタフェース回路及び送受信システム

【課題】伝送線路が規格を満たさない場合においても、伝送波形の規格を満足させることが可能なインタフェース回路及び送受信システムを提供する。

【解決手段】フレキシブル配線板のように、インピーダンスの大きな伝送線路がある場合、制御部14は信号送信時に、終端抵抗を信号受信時よりも大きくなるようにする(たとえば、抵抗R1<R2の場合、抵抗R2を選択する)。これにより、初期電圧が大きくなり、伝送波形の規格を満たすことが可能になる。

(もっと読む)

通信システム

【課題】マスタの第1のデバイスからスレーブの第2のデバイスに確実且つ容易にアクセスすることである。

【解決手段】バスコントローラFPGA1と、バスコントローラFPGA1と通信接続され、ライトクロック信号WCLKが一線路で順に伝送される複数のローカルFPGA21〜24と、を備え、バスコントローラFPGA1からのライトクロック信号WCLKの線路が最も長いローカルFPGA24は、リードクロック信号RCLKを出力して他のローカルFPGA23〜21を一線路で順に介してバスコントローラFPGA1に伝送し、各ローカルFPGA21〜24は、リードクロック信号RCLKに同期して入力信号を出力してバスコントローラFPGA1へ伝送し、各ローカルFPGA21〜24及びバスコントローラFPGA1の間のリードクロック信号RCLKの線路長と、前記入力信号の線路長とが等しい。

(もっと読む)

半導体集積回路の配置配線方法及び半導体集積回路の配置配線支援プログラム

【課題】クロックゲート回路の多重化及び統合によって非同期信号パスにおける故障検出率が低下せず且つ故障検出論理に変更を生じさせない半導体集積回路の配置配線方法を提供する。

【解決手段】クロックツリー経路に複数のクロックゲート回路を配置したとき、クロックゲート回路が出力するクロック信号のスキューを許容範囲に収めるためにクロックゲート回路の多重化又は統合を行うかを判定する。統合を行うときは、前記統合によって廃止するクロックゲート回路(CGC2)に代えて、当該クロックゲート回路のクロックイネーブル信号(CEN)の入力端子を故障検出経路まで接続する回路要素(3)を配置する。前記多重化を行うときは、多重化によって追加するクロックゲート回路に新たなスキャンラッチを割り当てて接続する。

(もっと読む)

1 - 3 / 3

[ Back to top ]