Fターム[5J056DD13]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | FET (1,892) | MISFET、MOSFET、IGFET (1,327)

Fターム[5J056DD13]に分類される特許

1,321 - 1,327 / 1,327

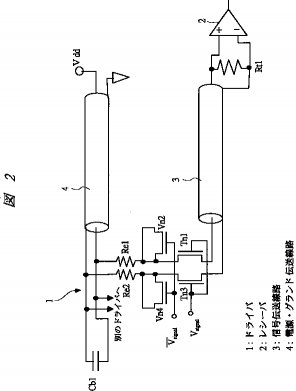

信号伝送システム

【課題】 できるだけ従来のシステム構成と部品構成を肯定しながら、数十GHz帯のディジタル高速信号を通すための信号伝送技術を提供する。

【解決手段】 電子回路全体に渡るトランジスタの論理回路、メモリ回路に含まれるドライバ1とレシーバ2の構成において、ドライバ1は信号伝送線路3を通じてレシーバ2に、電源・グランド伝送線路4を通じて電源Vddにそれぞれ接続される信号伝送システムであって、ドライバ1およびレシーバ2は全て実質的差動入力、差動出力とし、ドライバ1の実質的差動出力の出力端では電源またはグランドへの接続を有することなく、またレシーバ2は実質的差動入力の信号の電位差を検知することで受信し、さらに信号伝送線路3は分配配線がない、構造とする。

(もっと読む)

半導体集積回路

【課題】 本発明の目的は、高速・低消費電力の半導体集積回路を提供することにある。

【解決手段】 動作状態にある回路と待機状態にある回路を混在するようにして、回路毎にバックゲート電圧を設定可能にする。

【効果】 待機時には小電流とし低消費電力性を得て、動作時には大電流として高速性を得ることができる。

(もっと読む)

耐高電圧および伸展性ドライバ回路

【課題】 高レベルの電圧耐性および伸展性双方を有し、電源ピンが2本で済む入出力ドライバ回路を提供する。

【解決手段】 入出力ドライバ回路は、回路の出力ライン(30)と出力電源端子(42)との間に、1つのみの代わりに、2つのPMOSスイッチング・トランジスタ(T1A,T1B)を用いることによって、機能性デジタル回路(14)と他のデジタル回路のための共通バス(18)との間に、バッファ・インターフェースを備え、高いレベルの電圧耐性および伸展性を達成しつつ、必要な電源ピン(38,42)を2つのみに抑えた。トランジスタをオフに切り替えるには、出力電源(40)の電圧をそれらの一方のゲートに印加し、出力ライン電圧を他方のゲートに印加する。これによって、出力ライン電圧が出力電源レベルを超過したか否かには係らず、必要なときに、確実にトランジスタの少なくとも一方を最大限オフにする。

(もっと読む)

高速信号伝送配線実装構造

【課題】特に送信側と受信側からなる信号伝送系に関して、送信側半導体装置と受信側半導体装置とを接続する伝送用配線を往復する反射波に起因する信号の時間的揺らぎを抑え、ジッタを低減するための高速信号伝送配線実装構造を提供する。

【解決手段】送信基板100のインピーダンス不整合個所である半導体装置15aの出力回路と出力配線16aとの接続点と、受信基板200のインピーダンス不整合個所である接続点26との間の距離を、信号伝送時間が信号切替周期の半分の時間の整数倍となるように定める。これにより、送信基板100及び受信基板200のそれぞれのインピーダンス不整合個所で反射する信号によるジッタの影響を抑えることができ、その結果高速で信号切替周期の短い信号伝送に耐えうる高速信号伝送配線実装構造を提供できる効果がある。

(もっと読む)

半導体回路

【課題】 半導体回路において、回路動作の履歴により動作速度が変化しないようにすること、寄生バイポーラトランジスタがオンするのを防止すること、及び設計データの共通化を図ること。

【解決手段】 電界効果形トランジスタのボディーと電源とを抵抗(RBMP1,RBMN1)を介して接続する。

【効果】 本発明を用いると、切り換わり後、ボディーの電位が初期状態に復帰するので、上記課題を解決できる。

(もっと読む)

半導体集積回路装置

【課題】 入力回路の簡素化と製品管理の取り扱いを簡便にしつつ、実質的な低消費電力化及び素子の微細化に適合して安定した入出力伝達特性を実現できる入力回路を備えた半導体集積回路装置を提供する。

【解決手段】 外部端子から供給される入力信号を受ける差動増幅回路に第1と第2の動作電圧を第1と第2のスイッチMOSFETを介して供給するようにし、バイアス電圧発生回路により上記入力信号が上記第1と第2の動作電圧の中心電圧付近にあるときに上記第1と第2スイッチMOSFETをオン状態にし、その入力信号が継続的に一定期間上記第1電圧又は第2電圧にあるときには、それに対応した出力信号を形成すべく上記第1又は第2スイッチMOSFETのいずれか一方をオン状態に他方をオフ状態にする制御電圧を形成し、上記第1動作電圧と第2動作電圧に対応した第1振幅の入力信号と、上記第1動作電圧と第2動作電圧の間の所定の中間電圧に対応した第2振幅の入力信号の双方の供給を可能とする。

(もっと読む)

入力回路及び半導体集積回路装置

【課題】外部信号に応答した内部信号を生成する入力回路であって、増幅時に発生する外部信号のエッジから内部信号の立ち上がりエッジ及び立ち下がりエッジの相対的な遅延を改善する。

【解決手段】差動回路は、外部信号DQS ,DQと基準電圧Vref がそれぞれ入力される一対のNMOSトランジスタTN1,TN2を備え、外部信号DQS ,DQと基準電圧Vref に基づいて一対のNMOSトランジスタTN1,TN2にそれぞれ流れる電流に応じて、外部信号DQS ,DQに応答した内部信号dqsz,dqz を出力する。電流調整回路としてのNMOSトランジスタTN4は、外部信号DQS ,DQに対する内部信号dqsz,dqz のレベルに応答して差動回路の電流量を調整すべくオンオフ動作する。

(もっと読む)

1,321 - 1,327 / 1,327

[ Back to top ]