Fターム[5J056DD51]の内容

Fターム[5J056DD51]の下位に属するFターム

浮遊容量、寄生容量 (42)

Fターム[5J056DD51]に分類される特許

581 - 589 / 589

ダイナミックバックゲートバイアスを伴うブートストラップダイオードエミュレータ

【解決手段】ハーフブリッジスイッチング回路で使用するためのブートストラップダイオードエミュレータ回路が提供される。スイッチング回路は、負荷ノードにおいてトーテムポール構造の形で互いに繋がれているトランジスタと、これらのトランジスタを駆動するための駆動回路と、高圧側駆動回路に電力を供給するためのブートストラップコンデンサとを含む。ブートストラップダイオードエミュレータ回路は、ゲート、バックゲート、ソース、およびドレインを有し、そのドレインを高圧側供給ノードに結合され、そのソースを低圧側供給ノードに結合されているLDMOSトランジスタと、LDMOSトランジスタのゲートに電気的に結合されているゲート制御回路と、LDMOSトランジスタのバックゲートに電気的に結合されているダイナミックバックゲートバイアス回路とを備える。ダイナミックバックゲートバイアス回路は、LDMOSがオンにされたときに、LDMOSトランジスタのドレインの電圧に近いけれども同電圧よりも僅かに低い電圧をLDMOSトランジスタのバックゲートに印加することによって、LDMOSトランジスタのバックゲートを動的にバイアスするように動作可能である。 (もっと読む)

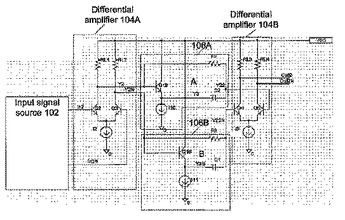

ドライブインピーダンスを低下させ、低減されたDCオフセットを提供する技術

簡潔には、最小コモンモード電圧の抑制で、低いRC時定数を有する複数の差動増幅器を結合する技術である。増幅器は入力信号源(102)、第1差動増幅器(104A)、第2差動増幅器(104B)、第1カップリングデバイス(106A)、第2カップリングデバイス(106B)を有する。入力信号源(102)は、第1差動増幅器(104a)に入力信号を供給する。

(もっと読む)

(もっと読む)

適応型入力/出力バッファ及びその方法

複数のプログラム可能遅延セルを有する複数の入力/出力チャネルを備えるコントローラは、それぞれ複数の遅延セルに導入される、複数の遅延時間を制御する複数のディジタル値を記憶するそれぞれ複数のレジスタをさらに備える。複数のレジスタにプログラムされた複数の値は、コントローラ及び複数のチャネルに結合された1つ以上のデバイス間の複数の信号のタイミングをテストすることで決定される。複数のテストは、逐次的な複数のテスト値のセットからの複数のテスト値で、複数のレジスタをセットする段階と、複数の信号の特定のパターンを、コントローラから1つ以上のデバイスへドライブする段階と、パターンの複数の部分が、1つ以上のデバイスに、正確に受信されてるかをチェックする段階とを備える。複数の信号を調整する段階は、複数のセットアップ及びホールドタイム制約に関する複数の信号のセンタリングを備える。

(もっと読む)

(もっと読む)

負電圧のスイングに対して耐性のある入力段

負の信号スイングを有する入力信号(s(t))を受け取るための信号入力端(1)に接続可能なレベル・シフタ(15)を備える装置(10)。レベル・シフタ(15)は、正の信号スイングを有する出力信号(r(t))を提供するために、入力信号(s(t))のDCシフトを提供する。レベル・シフタ(15)は、第1の入力端(11)、第2の入力端(12)、および出力端(13)を有する増幅器(17)を備える。第1のコンデンサ(C1)、第2のコンデンサ(C2)、基準電圧源(16)、およびスイッチとして働くトランジスタ(14;74)は以下のように回路網に構成されている。すなわち、第1のコンデンサ(C1)が信号入力端(1)と第1の入力端(11)との間に配置され、第2のコンデンサ(C2)が出力端(13)と第1の入力端(11)との間のフィードバック・ループ(18)中に配置され、基準電圧源(16)が第2の入力端(12)に接続されている。トランジスタ(14)は、第2のコンデンサ(C2)を橋絡する枝路(19)中に配置され、それによって、レベル・シフタ(15)が時々リセットされることを可能にするために、制御信号(CNTRL)がトランジスタ(14)のゲート(14.1)に印加可能になっている。  (もっと読む)

(もっと読む)

センタタップ終端回路及びセンタタップ終端回路を有するプリント配線板

【課題】差動信号伝送線路の終端回路において、センタタップ終端回路を形成することにより差動インピーダンスが変動するため、コモンモード電流成分が発生し放射ノイズが発生する。

【解決手段】差動信号伝送線路の往路伝送線路と復路伝送線路の間に、同じ抵抗値の2つの抵抗を直列に接続し、2つの抵抗の接続部とプリント配線板のGNDとの間に、キャパシタを接続したセンタタップ終端回路において、往路伝送線路と復路伝送線路を一定の間隔で配線し、抵抗とキャパシタは往路伝送線路と復路伝送線路の外側に配置し、接続部は往路伝送線路と復路伝送線路と立体的に交差するように形成する。これにより、差動信号のtr/tf特性をほぼ一致させ、スキューの発生も防止することができる。また、差動インピーダンスの不整合がなく、高品質の信号波形を保つ事ができるため、放射ノイズの発生を大幅に抑制することができる。

(もっと読む)

差動信号伝送線路の終端回路

【課題】差動信号伝送線路の終端回路において、ディファレンシャルモード信号及びコモンモード信号に対して、整合センタータップ終端回路を実現しする。また、センタータップ終端回路を単一部品で構成する事により、実装面積を縮小するとともに、部品・実装コストの削減も達成する。

【解決手段】差動信号伝送線路における2つの線路の差動インピーダンスの約1/2である抵抗値を有する第1、第2の抵抗素子を、受信側ICの入力端に直列にして接続し、第1、第2の抵抗素子の中点とプリント配線板のGNDとの間に、第3の抵抗素子と第1のコンデンサ素子を直列に接続する。また、これらの抵抗素子とコンデンサ素子からなるセンタータップ終端回路部品をチップ抵抗部品に、電極、抵抗皮膜、誘電体皮膜を層状に重ね合わせる事により形成して、単一部品で実現する。

(もっと読む)

高速信号伝送システム

【課題】本発明は、2GHz以上の高速なLSIチップと接続され、該LSIチップと信号のやり取りをするチップ外線路に数十GHz帯ディジタル高速信号を通すことである。

【解決手段】本発明の高速信号伝送システムは、トランジスタキャリアのポンプアップ、ポンプダウンを自動的に行うデバイス構造、受信情報をフィードバックし、送信側で波形調整する遺伝的アルゴリズム回路の挿入、トランジスタから出て行く配線の伝送線路化、回路のコモン電源を排除した構成を作る。上記チップ外線路の送端または終端側の一方で基準電位を確認するため電源またはグランドへの接続を有するが、該基準電位を確認した送端または終端側の反対側の終端または送端では電源またはグランドへの接続を有さない。

(もっと読む)

出力回路装置

【課題】 電源電圧のダイナミックな変動により遅延が変化すると、例えば、クロックバッファのクロック信号にジッター(jitter)が含まれ、高速で正確なタイミングでの動作が困難になる。

【解決手段】 第1の電源線Vddと第2の電源線Vssとの間に少なくとも1つの分離用トランジスタ2a(2a',2b,2b')を有する制御回路を介して接続された出力回路1a(1b)を備える出力回路装置であって、前記分離用トランジスタの制御電極には、一定のレベルに保持された制御電圧Vba(Vba',Vbb,Vbb')が印加され、前記制御電圧は、前記第1または第2の電源線の電圧における高周波成分を減衰させるレベルの電圧であるように構成する。

(もっと読む)

半導体回路

【課題】 半導体回路において、回路動作の履歴により動作速度が変化しないようにすること、寄生バイポーラトランジスタがオンするのを防止すること、及び設計データの共通化を図ること。

【解決手段】 電界効果形トランジスタのボディーと電源とを抵抗(RBMP1,RBMN1)を介して接続する。

【効果】 本発明を用いると、切り換わり後、ボディーの電位が初期状態に復帰するので、上記課題を解決できる。

(もっと読む)

581 - 589 / 589

[ Back to top ]