Fターム[5J056DD52]の内容

Fターム[5J056DD52]に分類される特許

1 - 20 / 42

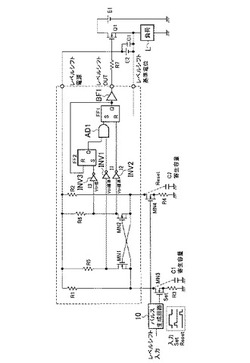

レベルシフト回路

【課題】レベルシフト基準電位が下がった場合にスイッチング素子を安全且つ確実に停止できるレベルシフト回路。

【解決手段】レベルシフト電源に接続された抵抗R1にドレインが接続されソースがグランドに接続されたMOSFETMN3、R1と同じ抵抗値を有しレベルシフト電源に接続された抵抗R2にドレインが接続されソースがグランドに接続されたMOSFETMN4、入力信号に基づきMN3,MN4のオン/オフを制御するパルス生成回路10、MN3がオンである場合にセット信号を生成しMN4がオンである場合にリセット信号を生成する制御部MN1,MN2,R5,R6、制御部で生成されたセット信号とリセット信号とに基づき入力信号をレベルシフトした出力信号を出力しスイッチング素子Q1を動作させるフリップフロップFF1、レベルシフト基準電位が負電位に下がったことを検出してスイッチング素子を停止させるスイッチング動作停止部INV3,FF2,AD1を備える。

(もっと読む)

半導体装置

【課題】出力回路のSSN(Simultaneous Switching Noise)の振動ノイズの低減を可能とする半導体装置の提供。

【解決手段】第1及び第2の電源線と、前記第1の電源線VDDQと前記第2の電源線VSSQとの間に配置された出力回路12と、前記第1の電源線と前記第2の電源線との間に配置されたノイズキャンセル回路13とを備え、前記ノイズキャンセル回路13は、前記出力回路の前記出力ノードの論理レベルへの切り替え時に発生する所定の周期で指数関数的に減衰振動する電源ノイズに対して、前記電源に、前記振動から半周期分遅れ、前記振動と逆向きに減衰振動する電源ノイズを発生し、互いに打ち消し合わせる。

(もっと読む)

レベルシフト回路およびスイッチング電源装置

【課題】 高耐圧プロセスを使用することなく、回路的に高耐圧化したレベルシフト回路を実現できるようにする。

【解決手段】 一対のCMOSインバータを有し一方のインバータの出力ノードを他方のインバータのPチャネル型MOSトランジスタのゲート端子に交差結合してなるラッチ回路(22)と、該ラッチ回路のいずれか一方の出力ノードに接続されたCMOSインバータからなる出力段(23)とを有するレベルシフト回路において、ラッチ回路を構成する一対のCMOSインバータの各Pチャネル型のMOSトランジスタ(Mp1,Mp2)とNチャネル型のMOSトランジスタ(Mn1,Mn2)との間に、ゲート端子が電源電圧と接地電位の中間の電位が印加される第3電圧端子(FGND)に接続されたPチャネル型のMOSトランジスタ(Mp4,Mp5)をそれぞれ直列形態で設けた。

(もっと読む)

半導体回路および半導体装置

【課題】簡易な構成で電荷の再利用効率を高め、複数のLSIを搭載したシステム全体のエネルギー効率を向上することが可能な半導体回路および半導体装置を提供する。

【解決手段】入力端子20にLレベルの信号が入力されたとき、回路素子10の出力端子22に接続される信号線24の配線容量Cpに正の電荷が充電される。入力端子20にHレベルの信号が入力されたとき、NMOSトランジスタNr1は、論理素子のNMOSトランジスタN1が導通するのと同時に導通する。これにより、信号線24から放電される電荷の一部が、NMOSトランジスタNr1およびダイオードD1を介して、電荷回収線2に移動する。電荷回収線2が回収した電荷は、電荷再利用端子3を介して半導体チップ1Aの外部に放出されると、電荷再利用線30に接続された電荷回収用の容量素子Cextに蓄積される。蓄積され電荷は、他の半導体回路等の電源端子に供給される。

(もっと読む)

半導体集積回路装置

【課題】保護対象の回路ブロックの上に配置された導電パターンに加えられた改変の検出精度を向上するための技術を提供することを目的とする。

【解決手段】半導体基板に配置された回路ブロックと、回路ブロックのうち保護対象の部分の上層に配置された導電パターンと、導電パターンの第1部分の電位を基準電位にリセットするリセット部と、第1部分を電流供給ラインに接続する接続部と、第1部分の電位を基準電位にリセットした後に第1部分を電流供給ラインに接続してから一定時間経過後の第1部分の電圧が事前に設定された範囲に含まれるか否かを判定し、一定時間経過後の電圧が事前に設定された範囲に含まれない場合に導電パターンに改変が加えられたことを検出する検出回路とを有する半導体集積回路装置が提供される。第1部分の電圧の変化は、導電パターンの回路定数に依存する。

(もっと読む)

レベルシフト回路及びスイッチング電源装置

【課題】dv/dt印加時に誤動作を防止し且つローサイド側からハイサイド側へ信号を伝達し低電圧でも広い範囲で動作するレベルシフト回路。

【解決手段】dv/dt過渡信号が印加され且つ入力信号が入力されないとき第1抵抗R1を含むセット側負荷抵抗R1,R9,MP1のオン抵抗及び第2抵抗R2を含むリセット側負荷抵抗R2,R10,MP2のオン抵抗を第1抵抗及び第2抵抗よりも小さくし、トランジスタMN3がオンである場合にセット信号を生成し且つセット側負荷抵抗をリセット側負荷抵抗よりも大きくし、トランジスタMN4がオンである場合にリセット信号を生成し且つリセット側負荷抵抗をセット側負荷抵抗よりも大きくする制御部MN1,MN2,MP1,MP2,R1,R2,R9,R10、セット信号とリセット信号とに基づいて入力信号をレベルシフトした出力信号を出力するフリップフロップ12を備える。

(もっと読む)

レベルシフト回路及びスイッチング電源装置

【課題】dv/dt印加時に誤動作を防止し且つローサイド側からハイサイド側へ信号を伝達し低電圧でも広い範囲で動作するレベルシフト回路。

【解決手段】トランジスタMN3とトランジスタMN4とをオン/オフさせるパルス発生回路10、第1抵抗R1の両端に第3抵抗R9と非線形特性を有し且つ一定以上のdv/dt過渡信号が印加された場合にオンするダイオードD3〜D6とが接続された直列回路、第2抵抗R2の両端に第3抵抗と同じ抵抗値を有する第4抵抗R10とダイオードとが接続された直列回路、MN3がオンである場合にセット信号、MN4がオンである場合にリセット信号を生成し、MN3のドレインにおける電位とMN4のドレインにおける電位との間において電圧差が生じていない場合にはいずれの信号も生成しない制御部、セット信号とリセット信号とに基づいて入力信号をレベルシフトした出力信号を出力するフリップフロップ12を備える。

(もっと読む)

半導体装置

【課題】小型化、低電圧・低電力化ならびに高速化が可能なセンスアンプを提供する。

【解決手段】増幅作用をする交差結合された第1のMOSトランジスタと第2のMOSトランジスタのそれぞれのソースに直列に第3のMOSトランジスタと第4のMOSトランジスタを接続し、第3及び第4のMOSトランジスタの電流供給能力を第3及び第4のMOSトランジスタの制御電極に与える制御電圧で制御する。データ保持期間において、制御電圧により第3及び第4のMOSトランジスタに、データ保持に必要な最小限のサブスレッショルド電流を流し、ビット線電位を保持する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路のチップ面積とコストの増加や、電気的特性の問題を招くことなく、出力バッファ回路の出力電圧のリンギングを抑制する。

【解決手段】半導体集積回路200は、電源線10、電源抵抗11、接地線12、接地抵抗13、出力バッファ回路14,15,16、電源端子PVdd、接地端子PVss、出力端子PO1,PO2,PO3、及びリード端子17,18を含んで構成される。電源抵抗11は、電源線10と出力バッファ回路14の電源電位入力端との接続点N1と電源端子PVddとの間に接続されている。接地抵抗13は、接地線12と出力バッファ回路14の接地電位入力端との接続点N4と接地端子PVssとの間に接続されている。

(もっと読む)

半導体集積回路装置

【課題】スリープ状態の論理回路ブロックにおける寄生容量を用いることにより、電源共振雑音などの電源ノイズを大幅に低減する。

【解決手段】電源ノイズ測定回路9によって電源電圧VDDをモニタし、電源電圧VDDが任意の基準電圧以上となると、制御信号CONを出力し、スイッチコントローラ8は、仮想基準電位VSSAに蓄積された電荷を放出し、その後、任意の期間が経過すると、仮想基準電位VSSAに電荷を蓄積するようにスイッチ部6を制御することによって、基準電位VSS、および電源電圧VDDの電位を下降/上昇させ、電源電圧VDDの電源共振雑音をキャンセルする。

(もっと読む)

炭化珪素絶縁ゲート電界効果トランジスタを用いたインバータ回路および論理ゲート回路

【課題】動作速度を高速化できる SiC MISFETで構成された論理ゲート回路デバイスを得る。

【解決手段】nチャネルエンハンスメント型SiC MISFET(22)と、nチャネルデプリーション型SiC MISFET(22、22b)とでインバータ、NAND/NOR論理ゲート回路を構成する。

(もっと読む)

差動増幅器

【課題】入力端子にノイズが発生する。

【解決手段】第1の電流経路は、第1の電源端子と第1の出力端子間に接続され、制御端子に差動入力信号の一方が入力される第1のトランジスタと、第2の電源端子と第1の出力端子との間に接続され、制御端子に差動入力信号の他方が入力される第2のトランジスタと、第1の電源端子と第1のトランジスタとの間に接続される第1のスイッチ回路とを有し、第2の電流経路は、第2の電源端子と第2の出力端子との間に接続され、制御端子に差動入力信号の一方が入力される第3のトランジスタと、第1の電源端子と第2の出力端子との間に接続され、制御端子に差動入力信号の他方が入力される第4のトランジスタと、第2の電源端子と第3のトランジスタとの間に接続される第2のスイッチ回路とを有し、第1、第2のスイッチ回路は、制御信号により導通状態が制御される差動増幅器。

(もっと読む)

レベルシフト回路

【課題】定常状態においては電力消費が少なく、且つ、電源投入時においても出力状態の確定が保証されるレベルシフト回路を提供する。

【解決手段】一次側の電位系より高電位の二次側の電位系に論理値信号を伝達するレベルシフト回路であって、一次側の電位系で動作するパルス生成回路11とNチャンネルMOSFETM11およびM12から構成される入力回路10と、二次側の電位系で動作するインバータU21およびU22を、互いの入力と出力の間に接続された抵抗を介して環状に接続して構成されるラッチ回路20と、二次側の高電位あるいは低電位に設定する初期値設定回路31あるいは32を備え、少なくとも一方のインバータの入力に初期値設定回路を接続することにより、電源投入時の出力状態を確定する。

(もっと読む)

I/Oセルの出力回路

【課題】終端抵抗若しくはダンピング抵抗として機能する抵抗を備えた出力バッファ回路の出力特性と面積効率を向上させる。

【解決手段】出力トランジスタT11,T12の出力ノードを配線L1〜L5及び抵抗R11,R12を介してパッド11に接続した出力回路において、抵抗R11,R12の両側に出力トランジスタを形成する複数の領域12,13を相対向するようにレイアウトし、領域12,13の外側にパッド11をレイアウトした。

(もっと読む)

半導体装置、シフトレジスタ、電子機器

【課題】パルス出力回路内のノイズを低減し、より確実な動作を保証する半導体装置を提供する。

【解決手段】クロック信号等の振幅を有する信号に接続されたTFTが、パルス出力が無い期間にもON、OFFが確定する構成とする。具体的には、第1の振幅補償回路110の有する二つの入力部のうち一つを、トランジスタ106のゲート電極と電気的に接続させ、且つ第2の振幅補償回路120の出力部とも電気的に接続させる。また、第3の入力端子は、第1の振幅補償回路110には入力されず、第2の振幅補償回路120のみに入力される。この構成により、TFT105のゲート電極はTFT102,106を介してLレベルに確定され、従来例のようなノイズが発生することもない。

(もっと読む)

出力バッファ回路及び半導体装置

【課題】プリエンファシス機能を有し、ジッタを低減する出力バッファ回路の提供。

【解決手段】第1の論理信号を入力して伝送線路(L)を駆動する第1のバッファ回路(M1)と、第1の論理信号に対して所定の論理関係にある第2の論理信号を入力し、出力が第1のバッファ回路の出力と共通接続された反転バッファ(T4,T5)と、反転バッファと第1の電源(VDD)間に接続され、制御端子に入力される信号に基づき、オン・オフ制御される第1のスイッチ(T3)と、反転バッファと第2の電源(VSS)間に接続され、制御端子に入力される信号に基づき、第1のスイッチと連動してオン・オフ制御される第2のスイッチ(T6)と、を備えたプリエンファシス制御用の第2のバッファ回路(M2)を備える。

(もっと読む)

レベルシフト回路及びそれを用いたドライバと表示装置

【課題】低振幅の入力信号を高速に高振幅信号に変換するレベルシフト回路の提供。

【解決手段】第1及び第2の入力信号vi1、vi2に基づき、第1及び第2の出力端子の一方を第1のレベルシフト回路10と、第2のレベルシフト回路20と、第1の制御信号S0に基づき、前記第1及び第2の出力端子のうち、前記第1及び第2の入力信号が前記第1及び第2の入力端子に入力される時点で前記第2電圧レベルとされている一つの出力端子について、前記一つの出力端子と前記第2の給電端子間の電流経路を、前記第1及び第2の入力信号が前記第1及び第2の入力端子に入力される時点を含む所定期間、切断し、前記所定期間の後、前記一つの出力端子と前記第2の給電端子間の電流経路の切断を解除する制御を行う手段を備え、前記第1及び第2の出力端子の出力振幅は、前記第1及び第2の入力信号の振幅よりも大とされる。

(もっと読む)

マルチスレッショルドCMOS(MTCMOS)回路におけるチャージリサイクリング(CR)トランジスタのサイジング及び配置

【課題】パワーゲーティングされた(power-gated)回路におけるモード移行時のエネルギー消費を低減する。

【解決手段】第1の回路ブロックと第1のスリープトランジスタとの間の接続は仮想グラウンドノードである。回路は、それぞれがグラウンドに直接接続され電源に第2のスリープトランジスタを介して接続された複数の回路ブロックの第2の行を含む。第2の回路ブロックと第2のスリープトランジスタとの間の接続は仮想電源ノードである。回路は、仮想グラウンドノードを仮想電源ノードに接続し、アクティブモードからスリープモードへの移行、またはスリープモードからアクティブモードへの移行、またはその両方の移行の時に、第1の行の第1の回路ブロックと第2の行の第2の回路ブロックとの間のチャージリサイクリングを可能とするトランスミッションゲートまたはパストランジスタを有する。

(もっと読む)

レベルシフト回路およびこれを用いたDC−DCコンバータ

【課題】低電位系のMOSFETのドレイン−基板間に存在する寄生容量の影響により高電位系のラッチ回路が誤動作してしまうことを防止するレベルシフト回路を提供する。

【解決手段】本実施形態では、容量(C)51,52を配することにより、ノイズを吸収してラッチ回路100の誤動作を防止している。即ち、ラッチ回路100のインバータ(U1)41,インバータ(U2)42の入力端子と、高電位系であるラッチ回路100の基準電圧となる端子(V2L)6との間に、容量(C) 51,52を接続しているので、ノイズを容量(C)51,52に吸収させることが可能となり、ラッチ回路100の誤動作を防止することができる。

(もっと読む)

半導体集積回路装置

【課題】従来の半導体集積回路装置では、消費電流の変動に伴う電源ノイズの増大を効率的に抑制することができない問題があった。

【解決手段】本発明にかかる半導体集積回路装置は、内部回路に電源を供給する第1及び第2の電源配線と、第1の電源配線と前記第2の電源配線とを接続する電源スイッチ16と、内部回路におけるノイズを測定する電源ノイズ測定回路12a、12b、17と、電源ノイズ測定回路12a、12b、17の測定結果に基づいて電源スイッチ16の導通状態を制御する制御回路14と、を有する半導体集積回路装置である。

(もっと読む)

1 - 20 / 42

[ Back to top ]