Fターム[5J056GG01]の内容

Fターム[5J056GG01]の下位に属するFターム

段階的に制御するもの (163)

Fターム[5J056GG01]に分類される特許

1 - 11 / 11

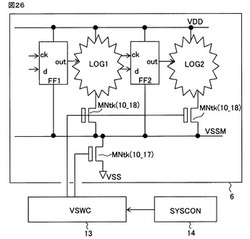

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

容量性スピーカ駆動回路

【課題】高音の音声信号が所定のレベル以上で所定時間以上入力されたときに、利得を低減させて高音過電流が発生することを防止する。

【解決手段】出力ドライバのパワートランジスタに流れる電流が所定時間以上にわたって所定値を超えた場合に高音過電流検出信号を発生する高音過電流検出手段と、前記高音過電流検出信号が発生されると前記プリアンプの通過周波数帯域を低くさせる通過周波数帯域切替手段とを設けた。

(もっと読む)

半導体装置、電源スイッチの制御方法及びその設計方法

【課題】従来の半導体装置では、電源制御領域への突入電流の発生を抑制するためにチップ面積が増大する問題があった。

【解決手段】本発明にかかる半導体装置は、オン抵抗が大きな第1のスイッチトランジスタSWLと、オン抵抗が小さな第2のスイッチトランジスタSWSと、を有し、第1、第2のスイッチトランジスタSWL、SWSは、異なる領域に電流を供給し、第1のスイッチトランジスタSWSは、制御信号CONTを直列的に伝搬するように直列に接続され、第2のスイッチトランジスタSWLは、前記制御信号を直列的に伝搬するように直列に接続され、第2のスイッチトランジスタSWLのうち初段に配置される第2のスイッチトランジスタSWLは、第1のスイッチトランジスタSWSのうち最も後ろに配置される第1のスイッチトランジスタSWSが出力する制御信号CONTが入力される。

(もっと読む)

デューティサイクル補正を行う方法

【課題】不均一なデューティサイクルを有する入力信号のデューティサイクル補正を行う方法を提供する。

【解決手段】不均一なデューティサイクルを有する入力信号をコンデンサ・デジェネレイティング差動対回路に入力し、前記回路内の1つ以上のコンデンサの両端に、前記入力信号のデューティサイクルの正の部分と負の部分との継続時間の差を表わす直流電圧を形成し、差動対回路のスイッチング動作を通じてデューティサイクルを有する出力信号を形成し、それによって出力信号のデューティサイクルの正の部分と負の部分の継続時間が、入力信号とスイッチングレベルとの交差点により規定される。必要に応じて、出力信号のデューティサイクルが少なくとも実質的に均一になるまで、信号(およびスイッチングレベル)が調整される。

(もっと読む)

COGアプリケーションのためのインターフェースシステム

本発明は、伝送ラインを通じて半導体チップの間に電流の形態でデータを送る電流駆動方式の送信機と受信機及び、これを適用したCOGアプリケーションのためのインターフェースシステムを提供する。送ろうとするデータの論理状態を示す差動電流を外部電流なしに正データ電流と負データ電流の差によって独立的に生成して送ることで電流源の設計及び工程上の原因に影響を受けないで伝送ライン対に印加される電流の大きさを一定なように維持することができる独立電流信号を利用した電流駆動方式の送信機と、伝送ラインを通じて受信した電流のレベル差を単一IVコンバータで同時に電圧レベルに変換して、トゥルーラインとバーライン(bar line)の誤差を減少させることができる独立電流信号を利用した電流駆動方式の受信機、及びこのような送信機と受信機を利用して伝送信号の歪曲を減らすことができるようにしたことを特徴とする。  (もっと読む)

(もっと読む)

電圧印加電流測定回路

【課題】負荷への電圧の供給を開始する際の立ち上がりを高速化することにより、電流の測定を効率的に行うことが可能な電圧印加電流測定回路を提供する。

【解決手段】電圧印加電流測定回路100は、レンジ2に切り換えられるとサミング点の電位を増幅させて第1、第2基準電圧と比較しこれら第1基準電圧と第2基準電圧の間にあるか否かを判定する。判定した結果、第1基準電圧と第2基準電圧の間にない場合には、回避スイッチ111をONとし電流が第2の抵抗器108を回避して流れてレンジ1と同様の時定数で高速化されて立ち上がる。判定した結果、第1基準電圧と第2基準電圧の間にある場合には、回避スイッチ111をOFFとし第1、第2の抵抗器107,108を流れて負荷114に供給された電流を測定する処理を行う。

(もっと読む)

出力回路

【課題】電源オフ時における誤認識を防止するとともに、電源オン時に消費電力の増加を抑えることができる出力回路を提供すること。

【解決手段】出力端子POと高電位電源AVD3との間に接続されたトランジスタTP2は、そのバックゲートの電位が制御部43により、高電位電源AVD3のオフ時にバックゲートの電位を出力端子POの電位に制御する。検出部42は、複数の抵抗R11〜R14により高電位電源AVD3の電位を検出した検出信号S11を出力する。その検出部42にはスタンバイ信号STBYに応答してオンオフするトランジスタT21が設けられ、該トランジスタT21は、スタンバイ信号STBYにより高電位電源AVD3のオン時にオフするように制御される。

(もっと読む)

差動電流駆動方式の送信システム

【課題】差動電流にデータを載せて、送信するための差動電流方式データ送信システムで、特に、半導体チップ外部の送信ラインに対する差動電流方式のデータ送信システムを提供すること。

【解決手段】本発明のトルーラインと、バーラインとからなる送信ラインに、電流差として、信号の送信を行う差動電流駆動方式の送信システムは、送信信号の論理値に応じて、前記送信ラインに電流差を与え、所定のタイミングに応じて、前記送信ラインを均等化(equalization)させる送信回路と、前記送信回路の信号送信及び送信ラインの均等化を制御するための送信制御部とからなる送信機と、前記送信ラインの電流差をミラーリングした後、電圧差に変換するためのIV変換回路と前記IV変換回路の電圧差を増幅するための差動増幅器とからなる受信機とを備えたことを特徴とする。

(もっと読む)

信号ドライバ

【課題】本発明は出力信号ドライバに関し、より具体的には波形操作、すなわちエンファシス機能を有する差動信号ドライバに関し、さらに具体的には電流モード論理、CMLアプリケーションに適した差動信号ドライバを提供する。

【解決手段】エンファシス・モード、非エンファシス・モード、およびアイドル・モードから選択的に切り替えることができる差動出力ドライバは出力リード線毎に1つのプルアップ装置および2つのプルダウン装置を使用する。プルアップ装置は好ましくは常に作動しており、望む挙動を提供するためにプルダウン装置の一方または他方、または両方が作動されまたはいずれも作動されない。いずれのプルダウン装置も単独でプルアップ装置を克服し出力リード線をエンファシス論理ローのレベルに引き下げるほど強くない。プルダウン装置の一方は単独で出力リード線を非エンファシス論理ローのレベルに引き下げる強さがある。

(もっと読む)

オフチップドライバ制御用カウンタ回路およびこれを用いたオフチップドライバの出力電流値変更方法

【課題】ウェーハ状態でPMOSとNMOSの工程特性の変動に応じてオフチップドライバのDC(あるいはAC)出力電流値を変更することが可能なオフチップドライバ制御用カウンタ回路およびそれを用いてオフチップドライバのDC(あるいはAC)出力電流値を変更する方法を提供する。

【解決手段】オフチップドライバ制御用カウンタ回路は、複数のオフチップドライバ制御信号を発生させるようにカウンティング動作を行う複数のカウンティング手段と、前記複数のオフチップドライバ制御信号の初期値を変更するためのセット入力信号とリセット入力信号を発生させる複数のヒューズブロックと、前記セット入力信号と前記リセット入力信号に応答して前記複数のオフチップドライバ制御信号の初期値を変更する複数の初期値変更部とを備えてなる。

(もっと読む)

擬似差動電流モード受信機

【課題】擬似差動電流モード受信機が開示される。

【解決手段】擬似差動電流モード受信機は、受信されたデータ電流をバッファリングして、入力インピーダンスは減少させ出力インピーダンスは増加させることによって、バッファリングされたデータ電流を生成するためのレギュレイティドカスコードバッファーを含む。又、信号変換機は、バッファリングされたデータ電流とレファレンス電流の差を示す出力信号を生成する。レファレンス電流も入力インピーダンスは減少させ出力インピーダンスは増加させることによって、レギュレイティドカスコードバッファーによってバッファリングされる。

(もっと読む)

1 - 11 / 11

[ Back to top ]