Fターム[5J067CA35]の内容

Fターム[5J067CA35]に分類される特許

1 - 15 / 15

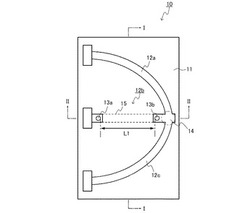

信号合成分配回路、電力増幅器および信号合成分配回路の製造方法

【課題】 簡単な構造で枝回路間の位相ずれによる利得低下を防止可能な信号合成分配回路を提供する。

【解決手段】 本発明の信号合成分配回路10は、基板11に、信号合成点または信号分配点14を有する複数の枝回路12a、12bおよび12cが配線され、前記複数の枝回路の少なくとも1本の枝回路12bが、他の枝回路12aおよび12cと異なる線路長であり、前記異なる線路長の枝回路12bの一部または全部15が、前記基板11中に配線されていることを特徴とする。

(もっと読む)

増幅回路

【課題】回路構成を複雑にすることなく、所望の周波数帯域において利得を向上させる増幅回路を提供する。

【解決手段】本発明の増幅回路は、半導体基板3と、前記半導体基板3上に形成され、高周波信号を増幅するトランジスタ1と、前記トランジスタ1のソース電極10sに接続された誘導性リアクタンス素子とを有し、前記誘導性リアクタンス素子は、前記半導体基板1の上方に形成され、有機物で構成される有機誘電体層6と、前記有機誘電体層6の前記半導体基板3側と反対側の面上に形成された配線を有する金属再配線層7とを含み、前記配線の一端は、前記トランジスタ1のソース電極10sに接続され、前記配線の他端は接地され、前記誘導性リアクタンス素子のリアクタンス値は、前記高周波信号の周波数帯域の中心周波数において10Ω以下である。

(もっと読む)

カスコード回路

【課題】ミリ波帯において、安定して動作するとともに、高利得または高出力なミリ波デバイスを実現することができるカスコード回路を提供することにある。

【解決手段】2つのトランジスタが縦続接続されたカスコード回路であって、ソースが接地されたHEMT1と、ソースがHEMT1のドレインに接続されたHEMT2と、HEMT2のゲートに接続され、反射利得を抑制する反射利得抑制抵抗3と、反射利得抑制抵抗3のHEMT2と反対側に接続され、所定周波数近傍の高周波信号を短絡するオープンスタブ4とを備えたものである。

(もっと読む)

二次巻線導体が一次巻線導体に磁気的に結合され、直列接続と並列接続を含むトポロジー構造を持つ変圧器電力合成器

【課題】複数の入力ポートと少なくとも1つの出力ポートを備え、高い変圧器結合効率と高い電力合成効率を達成するオンチップ変圧器電力合成器を提供する。

【解決手段】変圧器電力合成器は、複数の一次巻線導体と複数の二次巻線導体とを含む。一次巻線導体は、入力ポートにそれぞれ電気的に接続される。加えて、各一次巻線導体は対応する入力ポートのプラス端子とマイナス端子の間に電気的に接続されている。二次巻線導体は、一次巻線導体にそれぞれ磁気的に結合される。二次巻線導体は、出力ポートのプラス端子とマイナス端子の間に直列接続と並列接続を含むトポロジー構造を持つように構成される。

(もっと読む)

電源装置及び高周波回路システム

【課題】進行波管の通常動作時における最大ゲインの低下を招くことなく、安価な汎用部品を用いて、ヘリックス電圧及びコレクタ電圧の立ち上がり時にヘリックスに流れる電流を低減できる電源装置及びそれを備えた高周波回路システムを提供する。

【解決手段】へリックス電極とアノード電極間に接続されたツェナーダイオードと、ツェナーダイオードのカソードとアノード間を短絡または開放するトランジスタと、フォトトランジスタによりトランジスタをオン/オフするフォトカプラと、フォトカプラのフォトダイオードに対して直流電圧を供給または遮断するための第1のスイッチと、フォトダイオードに供給する直流電圧が印加されるコンデンサと、予め第1のスイッチをオンにしてフォトカプラ及びコンデンサに直流電圧を印加しておき、ヘリックス電圧の投入と同時に第1のスイッチをオフさせる制御部とを有する。

(もっと読む)

並列接続トランジスタ

【課題】配線のための面積増加なしに各トランジスタの入力信号の強度及び位相を均一にできる並列接続トランジスタを提供する。

【解決手段】並列接続トランジスタ50は、信号入力端子60に接続される伝送線路70、72と、伝送線路70及び72に沿って一列に配列されたトランジスタ84−1〜84−8及び88−1〜88−8と、伝送線路70、72に沿って一列に配列され、伝送線路70、72に一端が接続され、トランジスタ84−1〜84−8及び88−1〜88−8の対応する1つのベース端子に他端が接続された複数の容量素子82−1〜82−8及び86−1〜86−8とを含み、容量素子82−1〜82−8及び86−1〜86−8の容量値は、信号入力端子60からの伝送線路の線路長が大きいほど、小さくなっている。

(もっと読む)

差動増幅器

【課題】利得の低下を抑え、かつ小型で高利得な差動増幅器を得る

【解決手段】逆位相の信号がそれぞれ入力される第1の入力端子1aおよび第2の入力端子1bと、基本トランジスタセルをN段(Nは2以上の整数)並列接続してなり、逆位相の信号をそれぞれ増幅する第1の増幅器11および第2の増幅器12と、第1の出力端子3aおよび第2の出力端子3bとを備えた差動増幅器において、第1の増幅器11に含まれる基本トランジスタセルと第2の増幅器12に含まれる基本トランジスタセルとが互いに隣接する箇所を2箇所以上設けるように配列する。

(もっと読む)

増幅器

【課題】 高効率ドハティ増幅器の入力分配器の分配損によるゲイン低下を防止して高ゲインを図り、高次歪の増加を抑えて高次歪を低減できる増幅器を提供する。

【解決手段】 AB級で動作するキャリア増幅回路4とB級又はC級で動作するピーク増幅回路5からの出力をノード62で合成出力するものであって、分配器2で分配された信号に対して伝送線路33で線路の長さが調整されて低入力時の反射係数を変更し、キャリア増幅回路4からの信号をインピーダンス変換器64でインピーダンス変換し、ピーク増幅回路5からの信号について伝送線路65で損失がないよう低入力時のインピーダンスを大きくみせ、低入力時に、分配器2からピーク増幅回路5側の入力インピーダンスを無限大に近づけることで、低入力時の利得を上げる増幅器である。

(もっと読む)

マイクロ波電力増幅器

【課題】分配偏差を低減してFETセルの均一動作を図って利得と出力を向上することができるマイクロ波電力増幅器を得る。

【解決手段】複数のFETセル1から構成されているFETチップ2と、FETチップ2の入力側に接続された入力整合回路3と、FETチップ2の出力側に接続された出力整合回路4とを設けたマイクロ波電力増幅器であって、入力整合回路3、出力整合回路4の少なくとも一方は、FETチップ2に接続され、FETチップ側に信号の伝播方向に沿って複数本のスリット11又は12が異なる間隔で設けられたマイクロストリップ線路7又は9を含む。

(もっと読む)

導波管ベースの空間電力合成器において性能を向上させるための方法及び装置

電力合成アレイ及び電力合成アレイにおいて性能を向上させる方法は、複数のスロットラインモジュールが配置された導波管エンクロージャを含む。スロットラインモジュールは、該スロットラインモジュール構成にわたる電磁界強度の差異を克服して位相変化に対処するために異なる物理特性を有する入力及び出力アンテナを含む。異なる物理特性は、長手方向位置、厚さ、誘電率、及び回路素子構成の差異を含む。本要約は、サーチャ又は他の読者が技術的開示の内容を迅速に確認できるようにする要約を必要とする規則に則って提供するものである点を強調しておく。本要約が請求項の範囲又は意味を解釈又は限定するのに用いられることにはならないといった理解に従うものとする。 (もっと読む)

高周波ドハティ増幅器

【課題】 分配ロスを発生せず、高利得を得ることが可能な高周波ドハティ増幅器を提供すること。

【解決手段】 バラン102は、入力された高周波信号の電力が所定値未満の場合には、高周波信号を主増幅器102のみに出力し、一方、電力が所定値以上の場合には、高周波信号を主増幅器103と補助増幅器104に分配して出力するようにインピーダンスが調整される。主増幅器103及び補助増幅器104は、バラン102から入力された高周波信号を増幅する。バラン105は、主増幅器103から増幅されて出力された高周波信号と、補助増幅器104から増幅されて出力された高周波信号を合成する。

(もっと読む)

高出力差動増幅器

【課題】小型で利得が高く、高い出力が得られる高出力差動増幅器を得る。

【解決手段】基本トランジスタセルをN段(Nは2以上の整数)並列接続してなる第1の増幅器11および第2の増幅器12を有し、第1の増幅器11のエミッタ端子および第2の増幅器12のエミッタ端子を互いに接続して仮想接地点6を設け、第1の増幅器11のベース端子および第2の増幅器12のベース端子にそれぞれ逆位相となる信号を入力することにより、第1の増幅器11のコレクタ端子および第2の増幅器12のコレクタ端子から増幅された信号を出力する高出力差動増幅器において、第1の増幅器11および第2の増幅器12の対応する段の基本トランジスタセルのエミッタ電極同士を接続して1対ごとの仮想接地点6a〜6fを設け、1対ごとの仮想接地点6a〜6fを互いに接続したものである。

(もっと読む)

増幅器及び差動型分布増幅器

【課題】マッハツェンダ型LN光変調器を駆動するための増幅器等として使用される増幅器に関し、高利得特性を持ち、かつ、出力段の差動型分布増幅器の入力側動作バイアスポイントを容易に調整できるようにする。

【解決手段】ソースフォロア回路部68には電流源を設けず、ソースフォロアトランジスタ11、14のソースを本発明の差動型増幅器の第1実施形態69の入力端子18、19に接続する。差動型増幅器69の入力側伝送線路20、21の終端抵抗22、23の接続点25にソースフォロア回路部68に必要な電流源70を接続する。

(もっと読む)

マイクロ波回路

【課題】 特別な抵抗体の形成工程を設けることなく、非常に簡単な構成で、不要帯域での発振を抑えることができるマイクロ波回路を提供する。

【解決手段】 一面に分岐回路9、10などが形成され、他面側に接地導体1が設けられる誘電体基板2に貫通孔4が形成され、その貫通孔4内に多フィンガーFETチップ3が装着され、この貫通孔4の近傍で、誘電体基板2の一面に接地導体1と電気的に接続して接地導体膜5が設けられている。そして、多フィンガーFET3の複数のソース電極と接地導体膜5とが、第1の接続手段6により電気的に接続され、多フィンガーFETチップ3の複数のゲート電極と誘電体基板2の一面に設けられる入力側分岐回路9とが、第2の接続手段7により電気的に接続され、この第1の接続手段6の少なくとも1つは、第2の接続手段7の2つの間に設けられる構造になっている。

(もっと読む)

高周波接地構造

【課題】 本発明は、高周波接地を確実に行うことにより、増幅器の増幅率の低下を防止し、かつ異常発振を防ぐ等の良好な高周波特性を得ることができる高周波接地構造を提供する。

【解決手段】 回路基板上のパッケージMMIC30の部品直下に、実装するMMIC30の部品よりも若干小さな貫通穴38を開け、回路基板下部の金属基板35との間隙に高周波接地を強化する良導電性の金属部材32を配置する高周波接地構造である。

(もっと読む)

1 - 15 / 15

[ Back to top ]