Fターム[5J079BA34]の内容

電気機械共振器を用いた発振回路 (23,106) | 目的、効果 (4,554) | 波形整形 (124) | 歪低減 (97)

Fターム[5J079BA34]の下位に属するFターム

高調波歪スプリアス低減 (85)

Fターム[5J079BA34]に分類される特許

1 - 12 / 12

コルピッツ発振回路

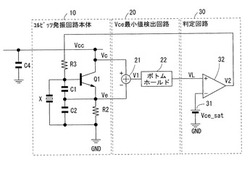

【課題】発振の定常状態における発振波形の歪みを低減すること。

【解決手段】コルピッツ発振回路本体10と、そのコルピッツ発振回路本体10の発振トランジスタQ1のエミッタとコレクタの差電圧の最小値VLを検出する最小値検出回路20と、該最小値検出回路20で検出された最小値VLと発振トランジスタQ1のコレクタ・エミッタ間飽和電圧Vce_satとを比較する判定回路30とを備え、判定回路30の判定結果に応じて発振トランジスタ10のベース電圧を制御し、発振トランジスタQ1のコレクタ・エミッタ間電圧が飽和領域に入らないようする。

(もっと読む)

水晶発振回路

【課題】出力波形の歪みを低減する水晶発振回路を提供する。

【解決手段】正・負電源ライン間に接続されたnMOSM4・pMOSM5と、nMOSM4・pMOSM5にバイアスを与えるnMOSM2・pMOSM3と、nMOSM4・pMOSM5の中心点と正・負電源ライン間に接続されたキャパシタC22・C24と、正・負電源ライン間に接続されたnMOSM14・pMOSM15と、nMOSM14・pMOSM15にバイアスを与えるnMOSM12・pMOSM13と、nMOSM14・pMOSM15の中心点と正・負電源ライン間に接続されたキャパシタC23・C25と、nMOSM2・pMOSM3の中心点とnMOSM12・pMOSM13の中心点との間に接続された水晶振動子X1とを備える。

(もっと読む)

圧電発振器

【課題】圧電発振器の低電源電圧化に対応可能とすると共に、安定した性能を有する圧電

発振器を提供することを目的とする。

【解決手段】圧電発振器1は、コルピッツ型の発振回路2と、発振回路2が出力する発振

信号より基本波周波数を濾波し、即ち通過させるフィルタ回路3と、発振回路2とフィル

タ回路3との間に接続されたダイオードD1とにより構成し、圧電発振器1には、ノイズ

を除去するためのバイパスコンデンサC5を介して電源電圧(Vcc)を印加している。

本発明においては、発振回路2とフィルタ回路3とをダイオードD1を経由して接続した

。

(もっと読む)

保護回路、発振回路、及び半導体集積回路

【課題】静電破壊耐性が高く、且つ、放電性能が優れた保護回路を提供する。

【解決手段】本発明の保護回路は、ドレインが外部端子に接続され、ゲートとソースとバックゲートが電源線4に接続されたPMOSトランジスタP1と、ゲートとソースとバックゲートが外部端子1に接続され、ドレインが接地線5に接続されたPMOSトランジスタP2とを備えている。

(もっと読む)

逓倍発振回路及びECL出力圧電発振回路

【課題】小型化で異常発振の発生を抑制できる逓倍発振回路を提供する。

【解決手段】水晶振動子Y1を有し所定の周波数で発振する水晶発振回路11と、水晶発

振回路11の発振出力に含まれる所定の高調波出力に同調する同調回路13と、増幅用ト

ランジスタQ2とこの増幅用トランジスタQ2コレクタ−ベース間に接続され自己バイア

ス機能とデカップリング機能を有する抵抗R4と、増幅用トランジスタQ2コレクタに接

続され、増幅用トランジスタQ2から出力される所定の高調波出力に同調する同調回路1

5と、同調回路13と同調回路15との間を結合する結合コンデンサC6とを備えるよう

にした。

(もっと読む)

発振回路

【課題】 ICの小型化、集積化に寄与し、より高い周波数の信号を安定して発生することができる発振回路を提供する。

【解決手段】 発振回路は、所定の共振周波数で共振する圧電振動子10と、差動接続された少なくとも一対の能動素子を有する差動増幅器と、を含み、圧電振動子10は一対の能動素子の間に接続されている。ここで、能動素子は電界効果トランジスタであり、圧電振動子10は、電界効果トランジスタのドレイン間またはゲート間に接続されていてもよい。

(もっと読む)

水晶発振器

【課題】 用途に応じて出力波形を変更することができる水晶発振器を提供する。

【解決手段】 水晶振動子2と発振回路とを備えた水晶発振器8において、複数の異なる波形を出力する複数の波形出力回路10〜12と、発振回路8の出力回路として、複数の波形出力回路10〜12からの何れか一つを選択するスイッチSW1a、SW1a〜SW3a、SW3bと、スイッチSW1a、SW1a〜SW3a、SW3bを選択するためのデータを記憶する内部メモリ回路6とを備えるようにした。

(もっと読む)

低ノイズ且つ高安定性を実現するクリスタルオシレータ

【課題】振幅が制御された差分信号を出力すると共にDCレベルを制御する、低ノイズ且つ高安定なクリスタルオシレータを実現する回路、方法および装置を提供する。

【解決手段】クリスタルオシレータ回路であって、フィードバックループを2つ有する。一方はクリスタルオシレータ信号のDCレベルを設定するために用いられ、他方はクリスタルオシレータ信号の振幅を調整するために使用される。DCレベル設定フィードバックループは、オシレータ信号のDC成分を2つの供給電圧の間に収まるように設定することができる。振幅制御ループは、クリスタルオシレータの出力信号の振幅を一定の範囲内に収める。振幅は、供給電圧をクリッピングすることなく安定性を高めジッタを低減することができる範囲内でスイングが最大となるように設定することができる。振幅制御回路は、ノイズ性能を改善するべくデジタル回路としてもよい。上記2つのループの時定数は、不安定化を避けるために分離してもよい。

(もっと読む)

水晶発振器回路および水晶発振器回路を内蔵する半導体装置

【課題】 対雑音に高い耐性をもつ差動回路を用いても、電源ノイズΔVに起因するジッタ特性を改善することはできなかった。

【解決手段】 水晶発振器回路は、水晶発振子(X0)を接続する第1端子(X1)及び第2端子(X2)と、第1増幅回路(1)と、第2増幅回路(2)とを具備する。第1増幅回路(1)は、第1端子(X1/OUT1)に入力を接続し、第2端子(X2/OUT2)に出力を接続する。第2増幅回路(2)は、第2端子(X2/OUT2)に入力を接続し、第1端子(X1/OUT1)に出力を接続する。水晶発振器回路は、第1端子(X1/OUT1)と第2端子(X2/OUT2)とを差動出力ノードとする。水晶発振器回路は、第1端子(X1/OUT1)から正電源(VCC)、負電源(VSS)をみたインピーダンスの比と、第2端子(X2/OUT2)から正電源(VCC)、負電源(VSS)をみたインピーダンスの比が等しくなるように構成される。

(もっと読む)

圧電発振器

【課題】所定のエージング特性をもつ圧電発振器を構成するために、水晶振動子と発振増幅用トランジスタを含む発振回路のほかに、増幅回路用と整流回路用とにトランジスタ各1個を必要とし、その他に整流用のダイオードを用いる回路構成となっており、回路が複雑で小型化、低コスト化の妨げとなっている。

【解決手段】発振回路1は水晶振動子X1、コンデンサC1、C2、C3により形成される発振ループと、発振用のトランジスタQ1とで構成されるピアース型発振回路とし、前記発振用トランジスタQ1のエミッタと共通の電位のエミッタをもつトランジスタQ2によるベース接地型の増幅回路2で発振回路出力を増幅する。このトランジスタQ2のコレクタ信号を、前記発振回路1のコンデンサC1と水晶振動子X1の直列回路の接続中点に帰還することによって前記水晶振動子X1の励振レベルを抑圧制御する。

(もっと読む)

圧電発振器

【課題】 コルピッツ型水晶発振器の発振を確実にすると共に位相雑音を改善する手段を得る。

【解決手段】 トランジスタのベース−接地間に水晶振動子を接続し、ベース−接地間に第1及び第2の容量を直列接続した回路を接続し、エミッタ−接地間に第1の抵抗を接続し、第1及び第2の容量の中点とエミッタ間に周波数選択素子を接続して構成したコルピッツ型水晶発振器であって、前記周波数選択素子に電界効果トランジスタのドレイン及びソースを並列接続し、ゲート接地間に第2の抵抗を接続し、ゲート電−源間に第3の容量を接続して圧電発振器を構成する。

(もっと読む)

多層基板の実装構造、その多層基板の実装構造を用いたクロック変換器およびそのクロック変換器を備えた電子機器

【課題】多層基板構造を工夫して各機能グループのグランドの電位を安定化させ、かつ、ノイズを生じさせないようにして、ジッタの少ないクロック変換器を実現する。

【解決手段】各機能グループとして分離されたAグループ1、Bグループ2、Cグループ3、Dグループ4中の回路部品は、それぞれ対応して設けられている第1層のグランドパターンに接続され、かつスルーホールを通して第3層の電源層に接続されている。各グランド層は共通化または分離される。各機能グループの第1層のグランドパターンは他の機能グループのグランドパターンから共通化または分離されているので、その電位は常に安定している。また、各機能グループ中の部品は第2層の第1グランド層、第4層の第2グランド層から離れているのでノイズの影響を受けない。

(もっと読む)

1 - 12 / 12

[ Back to top ]