Fターム[5J079BA35]の内容

電気機械共振器を用いた発振回路 (23,106) | 目的、効果 (4,554) | 波形整形 (124) | 歪低減 (97) | 高調波歪スプリアス低減 (85)

Fターム[5J079BA35]に分類される特許

1 - 20 / 85

圧電デバイス、及び電子機器

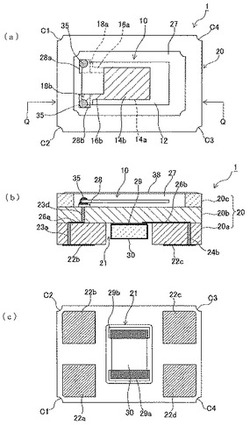

【課題】周波数温度特性が良好であり、且つ短期安定の優れた圧電デバイスを得る。

【解決手段】圧電デバイスは、圧電振動素子10と、感温部品30と、これらを収容する容器20と、を備え、容器20底部には実装端子22a〜22dが設けられている。実装端子22bと圧電振動素子10とを、第1の熱伝導部23a、23dと第1の配線パターン26aにより、電気的に接続し、且つ実装端子22cと感温部品30とを、第2の熱伝導部24bと第2の配線パターン26bとにより、電気的に接続して構成した圧電デバイスである。

(もっと読む)

水晶発振回路

【課題】差動回路を使用することで、貫通電流に起因した高調波ノイズの影響を排除した水晶発振回路を構成することができる。しかし、他の回路が動作することによって生じた高調波ノイズが、水晶発振回路の発振出力に影響を与える場合がある。そのため、電源電圧が変動したことによる影響を軽減し、発振出力のジッタを抑制した水晶発振回路が、望まれる。

【解決手段】水晶発振回路は、水晶振動子を含む共振回路と、共振回路と接続され、差動対を含む信号反転回路と、差動対にバイアス電流を供給する電流源回路と、信号反転回路及び電流源回路に電源を供給する電圧線と信号反転回路の間に接続され、水晶振動子の固有の発振周波数より低い遮断周波数を持つローパスフィルタ回路と、を備えている。

(もっと読む)

バッファ回路

【課題】出力波形を高調波が発生しない様に調整する事ができ、高次高調波の抑圧効果の高い水晶発振回路の提供。

【解決手段】水晶振動子を振動源とする発振回路部と、この発振回路部の出力信号を入力とするCMOSトランジスタのインバータからなる複数段のバッファ回路部11、12、13と、このバッファ回路部の出力から直流成分をカットするキャパシタCB1、CB2を介して増幅するCMOSプッシュプル型増幅回路14とを備えた水晶発振回路に於いて、バッファ回路部13のCMOSトランジスタTp4とCMOSトランジスタTn4間に抵抗素子R3、R4を接続し、その中間点はバッファ回路部13の出力として、前記抵抗素子と前記キャパシタとからなる時定数で出力信号の波形成形を行い、且つ前記抵抗素子のバイパス回路16をメモリ設定にて、MOSスイッチ手段17のオン/オフ切り替えにより可能とするメモリを備えてなる。

(もっと読む)

水晶発振器

【課題】電源電圧が低電圧化されても安定した発振動作が可能な水晶発振器を提供する。

【解決手段】本発明の水晶発振器は、高電位側電源と水晶振動子(2)の一端並びに他端との間に設けられた第1,第2の抵抗(R1,R2)と、その一方の主端子が前記水晶振動子の一端並びに他端と接続された第1,第2のトランジスタ(T1,T2)と、第1,第2のトランジスタの他方の主端子間に接続されたキャパシタ(C1)と、第1,第2のトランジスタの他方の主端子と低電位側電源との間に設けられた電流源(IR1,IR2)又は抵抗と、第1,第2のトランジスタの一方の主端子と第2,第1のトランジスタの制御端子との間に設けられ、一方の主端子の電圧に追従するとともに一方の主端子の電圧から直流オフセット電圧分降下した電圧を生成して制御端子に印加させる第1,第2の電圧フォロワ回路(4,5)と、を備える。

(もっと読む)

発振回路及び発振器

【課題】発振子と発振回路とのインピーダンス整合を容易にとることができる発振回路及び発振器を提供する。

【解決手段】発振回路100が、第1の入力端子4と、第1の出力端子5と、第1の入力端子4に接続される信号調整部10と、第1の入力端子4及び第1の出力端子5に接続される信号形成部20と、を含み、該信号調整部は、第1の素子13、第1の抵抗11、第2の抵抗12及び第1のコンデンサー14を有し、第1の素子13は、一方端が第1の入力端子4に接続され、他の一方端が第1の抵抗11の一方端、第2の抵抗の一方端及び第1のコンデンサーの一方端に接続され、第1の抵抗は、他の一方端が第1の電源2に接続され、第2の抵抗は、他の一方端が第2の電源3に接続され、第1のコンデンサーは、他の一方端が第2の電源に接続され、該信号形成部において、第1の出力端子から出力される信号は、第1の入力端子から入力された信号を基に形成される。

(もっと読む)

発振回路

【課題】 位相雑音を軽減すると共に、起動時の発振の成長を妨げず、温度や経時変化の影響を受けにくくして安定した出力を得ることができる発振回路を提供する。

【解決手段】 水晶振動子X1の一端が発振用トランジスタTr1のベースに接続されると共に他端が接地され、直列接続のコンデンサCb1,Cb2が水晶振動子X1に並列に接続されたコルピッツ発振回路において、発振用トランジスタTr1のベースの前段に、水晶振動子X1の発振周波数を狭帯域化するフィルタXfを挿入した発振回路であり、また、フィルタXfの前段にバッファ用トランジスタTr2を備えた発振回路である。

(もっと読む)

回路装置及び電子機器

【課題】無駄な電力消費やノイズの悪影響等を抑制できる回路装置及び電子機器等の提供。

【解決手段】回路装置は発振回路10とバッファー回路20を含む。バッファー回路20は、プリバッファーPBFと第1、第2の出力バッファーQBF1、QBF2を含む。第1のモードでは、第1の出力バッファーQBF1が動作イネーブル状態に設定され、第2の出力バッファーQBF2が動作ディスエーブル状態に設定される。第2のモードでは、第1の出力バッファーQBF1及び第2の出力バッファーQBF2が動作イネーブル状態に設定される。第1のモードでは、プリバッファーPBFの駆動能力が、第2のモードに比べて低い駆動能力に設定される。

(もっと読む)

発振器

【課題】純度の高い正弦波を出力するようにして、位相雑音を低減できる発振器を提供すること。

【解決手段】トランジスタ3を増幅部として用いたコルピッ型発振回路において、発振ループの外または中に波形整形用の水晶振動子5を設ける。そして発振用の水晶振動子1と波形整形用の水晶振動子5とは、共通の水晶片10に、電極対(11、12)及び電極対(51、52)を設けて構成する。水晶振動子1の電極11(12)と水晶振動子5の電極51(52)とは離間距離を大きくして互に弾性的に結合しないか、結合してもその程度が弱いようにすると共に、水晶振動子5の並列容量に対して並列共振を起こすインダクタを設ける。水晶振動子5と波形整形用の水晶振動子1とを、共通の圧電片を用いたSAW共振子として入れ替えた構成としてもよい。

(もっと読む)

水晶発振回路

【課題】出力波形の歪みを低減する水晶発振回路を提供する。

【解決手段】正・負電源ライン間に接続されたnMOSM4・pMOSM5と、nMOSM4・pMOSM5にバイアスを与えるnMOSM2・pMOSM3と、nMOSM4・pMOSM5の中心点と正・負電源ライン間に接続されたキャパシタC22・C24と、正・負電源ライン間に接続されたnMOSM14・pMOSM15と、nMOSM14・pMOSM15にバイアスを与えるnMOSM12・pMOSM13と、nMOSM14・pMOSM15の中心点と正・負電源ライン間に接続されたキャパシタC23・C25と、nMOSM2・pMOSM3の中心点とnMOSM12・pMOSM13の中心点との間に接続された水晶振動子X1とを備える。

(もっと読む)

発振器

【課題】 MEMS共振器を用いた発振器において、TIAの雑音の影響を低減し、発振器出力の位相雑音特性を改善することができる発振器を提供する。

【解決手段】 MEMS共振器7と、TIA5と、バッファアンプ9とを備えた発振器において、MEMS共振器7の出力をTIA5に入力する配線15に、電磁誘導により結合して、当該配線15を流れる電流を電圧に変換してバッファアンプ9に出力する電流/電圧変換器を備え、発振器出力を電流/電圧変換器から取り出すようにした発振器であり、また、当該電流/電圧変換器を、配線15を非接触に取り囲むように形成され、一端が接地され他端がバッファアンプ9に接続する発振出力コイル11とした発振器である。

(もっと読む)

表面実装型圧電発振器の搭載構造

【課題】 EMIノイズの悪影響を低減することができる。

【解決手段】 圧電振動素子と、集積回路素子と、絶縁性のベース2と、蓋3とを有する表面実装型圧電発振器1の搭載構造であって、前記ベースの一主面の端部に複数の外部端子電極と、この間に圧電振動素子測定端子が形成され、外部回路基板の一主面には、前記外部端子電極が接続される配線パッドと配線が形成された導電領域55と、これらが形成されていない他領域56とを有しており、前記回路基板の配線パッドと前記ベースの外部端子電極を接合した際に、前記圧電振動素子測定端子が対向配置される他領域では、表面の絶縁層の下にグランド電極に接続される導電層562が形成されてなる。

(もっと読む)

発振装置

【課題】発振周波数を決定する容量値の変化に伴う発振周波数の変動を抑え、且つ、位相雑音を低減することのできる発振装置を提供する。

【解決手段】発振装置は、ドレイン接地回路からなる第1増幅回路10と、第1増幅回路10の出力を増幅する、ゲート接地回路からなる第2増幅回路20と、第2増幅回路20の出力を第1増幅回路の入力に帰還させるコンデンサC1と、第1増幅回路10の入力側に設けられた共振器2と、共振器2及び第1増幅回路10内のトランジスタQ1に動作用のバイアス電圧を印加するバイアス回路12と、第2増幅回路20内のトランジスタQ2に動作用のバイアス電圧を印加するバイアス回路22とから構成される。この結果、位相雑音の発生を、単一のトランジスタからなるコルピッツ発振回路と同程度に抑えつつ、容量変化によって発振を起動できなくなったり、発振周波数が変動するのを防止できる。

(もっと読む)

濾波装置

【課題】水晶振動子、およびセラミック振動子にて、従来の方法では信号の波形歪みが生じ、また、最適な振幅にすることが困難である。そこで、波形歪みを改善し、最適な振幅にすることができる濾波装置を提供する。

【解決手段】電気信号を発振し所望の周波数を生成する発振部(11)と、発振部(11)によって発振された電気信号を濾過し緩衝信号を生成する第1濾波部(12)と、第1濾波部(12)に直列に接続し電気信号を生成する半導体部(9)と、半導体部(9)によって生成された電気信号を濾過し緩衝信号を生成する第2濾波部(13)と、を有し、第2濾波部(13)は、発振部(11)と直列に接続する濾波装置。

(もっと読む)

水晶発振回路

【課題】振幅制限を行いながらも消費電流量を低減することができる水晶発振回路を実現する。

【解決手段】インバータINVの入力端と出力端との間には、水晶振動子XDおよび抵抗器Rがそれぞれに並列に接続されている。インバータINVの入力端と出力端とは、キャパシタCによりグランドに接続されている。ダイオードDは、これらインバータINV、水晶振動子XD、抵抗器Rに対して、他の回路素子を介することなく単独で並列接続されている。この際、ダイオードDのアノードがインバータINVの入力端に接続され、ダイオードDのカソードがインバータINVの出力端に接続されている。

(もっと読む)

発振器

【課題】専用端子を設けることなくLPF用の外付けコンデンサーを接続する。

【解決手段】データ端子10と、データDAを書き込み可能な記憶回路20と、チップセレクト端子30と、データ端子10に接続されたコンデンサーC1と、圧電振動子40と、温度補償電圧VCによって圧電振動子40が発振する発振周波数を制御する発振回路50と、温度補償電圧VCを発生する温度補償制御回路60と、スイッチ回路100と、を含み、スイッチ回路100は、データ端子から入力されたデータDAの所定のビット値が第1の値に設定された場合、温度補償制御回路60と発振回路50とを接続かつデータ端子DAと記憶回路20とを接続し、データ端子から入力されたデータDAの所定のビット値が第2の値に設定された場合、温度補償制御回路60と発振回路50とを抵抗素子R1を介して接続かつデータ端子DAと発振回路50とを接続する切換動作を行う発振器1。

(もっと読む)

温度補償型圧電発振器

【課題】発熱素子の影響を軽減する。

【解決手段】圧電振動子10と、制御電圧VCに基づき圧電振動子10の発振周波数を制

御する発振回路150と、温度を検出し第1の電圧V1を出力する第1の温度検出器T1

と、温度を検出し第2の電圧V2を出力する第2の温度検出器T2と、第1の電圧V1と

第2の電圧V2との差の電圧である第3の電圧V3を出力する差分回路120と、第1の

電圧V1と第3の電圧V3との和の電圧である第4の電圧V4を出力する加算回路130

と、第4の電圧V4に基づき制御電圧VCを発生する制御電圧発生回路140と、を含む

温度補償型圧電発振器1。

(もっと読む)

圧電発振器

【課題】各種電子機器とのインピーダンス整合を考慮した圧電発振器。

【解決手段】電圧発生回路120と、電圧発生回路120が出力する制御電圧VCに基づ

いて所定の発振周波数で圧電振動子100を発振させる発振回路110と、発振回路11

0の発振出力をバッファするバッファ回路210と、外部出力端子OUTと、蛇行させた

配線パターンにより形成されるn個(nは1以上の整数)のインダクタンス素子L1〜L

3と、バッファ回路210の出力線211と外部出力端子OUTとの間にn個のインダク

タンス素子L1〜L3の各々を接続するか否か切り替える切替回路200と、を含む圧電

発振器1。

(もっと読む)

電子デバイス

【課題】小型化を図り、チップ部品等の電子部品を後付け可能な構造で、かつ電子部品と

の接続が安定した電子デバイスを提供することを目的としている。

【解決手段】本発明の電子デバイス10は、第1及び第2のフレキシブル基板20,40

と、第1及び第2のフレキシブル基板20,40の間に収容される内蔵電子部品100と

、を備え、第1のフレキシブル基板20の一方の面に電子部品実装用22の電極が形成さ

れ、他方の面に第1の内部電極24が形成され、第1のフレキシブル基板20に形成され

たビアホール26により電子部品実装用電極22と第1の内部電極24が電気的に接続さ

れ、第2のフレキシブル基板40の一方の面に第2の内部電極42が形成され、第1の内

部電極24と第2の内部電極42を導電性の接続部材60で接続し、第1のフレキシブル

基板20と第2のフレキシブル基板40との間に内蔵電子部品100及び接続部材60を

覆う樹脂部材70が形成されている。

(もっと読む)

圧電デバイス装置

【課題】 磁界シールド特性が優れた筐体に密閉した圧電デバイス装置を提供する。

【解決手段】 圧電デバイス(100)は、天部と側壁部とを有し第1金属材料からなる第1金属ケース(20)と、天部と側壁部とを有し第1金属ケースを覆うとともに、第1金属とは異なる第2金属材料からなる第2金属ケース(30)と、第1金属ケースの内側に固定された圧電振動片(10)と、第1金属ケースと第2金属ケースとが接合されるベース板(22)と、を備える。

(もっと読む)

副振動抑圧型の水晶発振回路

【課題】特にSCカットでのBモードを抑圧してCモードでの発振を確実にし、しかも部品点数を少なくした水晶発振回路を提供する。

【解決手段】水晶振動子3と第1及び第2コンデンサC1、C2とからなる発振用共振回路1と発振用トランジスタ2とを有し、ベース・コレクタ間に水晶振動子3を、エミッタ・コレクタ間に第1コンデンサC1を、エミッタ・ベース間に第2コンデンサC2を接続したコルピッツ型で、発振用トランジスタ2のエミッタ・コレクタ間又はエミッタ・ベース間は第1又は第2コンデンサC1、C2にLC直列回路4を並列接続したリアクタンス並列回路5からなり、リアクタンス並列回路5は主振動モードによる発振周波数f1oでは容量性となる共振特性を有し、LC直列回路4の共振周波数frは副振動モードによる振動周波数fo2に一致した構成とする。

(もっと読む)

1 - 20 / 85

[ Back to top ]