Fターム[5J079BA50]の内容

電気機械共振器を用いた発振回路 (23,106) | 目的、効果 (4,554) | 振動子の破壊防止 (98) | 対過大入力 (11)

Fターム[5J079BA50]に分類される特許

1 - 11 / 11

集積回路、それを用いた発振回路および電池駆動型電子機器

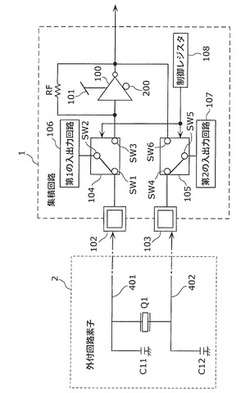

【課題】搭載された素子を破壊することなく、発振端子と汎用端子の兼用化を実現する。

【解決手段】第1の入出力端子102と、第1の入出力端子102に対応する第1の電子回路部106と、第2の入出力端子103と、第2の入出力端子103に対応する第2の電子回路部107と、入力部と出力部とを備え、制御信号200により出力部がハイインピーダンスにされる第3の電子回路部100と、第1の入出力端子102を、第1の電子回路部106、または、入力部と接続させる切り替え機能を有する第1のスイッチ104と、第2の入出力端子103を、第2の電子回路部107、または、出力部と接続させる切り替え機能を有する第2のスイッチ105と、第1のスイッチおよび第2のスイッチを切り替えるための制御信号出力する制御レジスタ108とを具備する。

(もっと読む)

半導体集積回路装置

【課題】リーク電流が増大した場合でも安定的に発振する発振回路の提供。

【解決手段】差動増幅器OPは、反転入力端子(−)を外部端子P1、抵抗素子R1の一端および静電保護回路11bに接続し、出力端子を外部端子P2、抵抗素子R1の他端および静電保護回路11cに接続し、非反転入力端子(+)を静電保護回路11aに接続すると共に抵抗素子R2を介して反転出力端子に接続する。静電保護回路11a、11b、11cは、逆バイアスに直列接続された2個のダイオードを電源、接地間に接続し、2個のダイオードの接続点を差動増幅器OPの非反転入力端子(+)、反転入力端子(−)、出力端子にそれぞれ接続する。外部において外部端子P1、P2間に水晶振動子XTLを接続し、外部端子P1に一端が接地された容量素子C1を接続し、外部端子P2に一端が接地された容量素子C2を接続し、発振回路を構成する。

(もっと読む)

表面実装用の水晶発振器

【課題】水晶片に対する電磁シールドを維持しつつ、ICチップを収容する実装基板の機械的強度が保たれ、ICチップ内の電子回路が浮遊容量の影響を受けにくく、かつ、ICチップ内の電子回路が機械的なダメージを受けることがない、表面実装用の水晶発振器を提供する。

【解決手段】積層セラミックからなる実装基板2の底壁層2aを第1の層2a1と第2の層2a2の2層構成としてこれら層2a1,2a2の積層面に金属膜からなる中間層14を設ける。ICチップ1は底壁層2aに対してバンプ6を用いた超音波熱圧着で固着する。中間層14では、ICチップ1の回路形成領域に対応して開口部を設ける。

(もっと読む)

圧電振動片及び圧電デバイス

【課題】 圧電振動片又は圧電デバイス内の電子素子が静電気の放電反応により損傷されることを回避するために、放電が起きにくい圧電振動片又は圧電デバイスを提供する。

【解決手段】 第1及び第2基部電極が形成されている基部と、基部から突出する第1振動腕部及び第2振動腕部と、 第1及び第2振動腕部に形成されている第1及び第2励振電極と、 第1基部電極と第1励振電極とを曲線状に形成された電極で接続する第1接続電極部と、 第2基部電極と第2励振電極とを曲線状に形成された電極で接続する第2接続電極部と、 を備える。

(もっと読む)

電子装置

【課題】発振特性の検査を行うことができると共に、発振不良の発生を抑制することができる電子装置を提供すること。

【解決手段】

振動子10と、振動子10と共に発振回路を形成する回路部20とを樹脂で封止してなる電子装置50であって、一方の端部が振動子10の両端にそれぞれ接続されると共に他方の端部が樹脂の外部に露出する振動子の発振特性検査用の検査端子41,42と、検査端子41,42と振動子10との間に設けられ、検査端子41,42の電位による影響から振動子10を保護する保護抵抗31,32とを備える。

(もっと読む)

圧電振動装置、発振回路及び電子装置

【課題】Qが高く、耐電力性に優れているだけでなく、印加電圧によるインピーダンス特性曲線の乱れが生じ難い、圧電振動装置を得る。

【解決手段】圧電薄膜4の下面に下部電極5が、上面に上部電極6が形成されている圧電振動部3が基板2から浮かされた状態で支持部9,10により支持されており、矩形の圧電振動部3の輪郭振動を利用しており、該輪郭振動と、圧電振動部3において生じる屈曲振動とが結合しないように、上記輪郭振動の共振周波数と屈曲振動の共振周波数とが隔てられている、圧電振動装置1。

(もっと読む)

半導体装置

【課題】製造プロセスの微細化と、しきい電圧の低下により、通常オフ状態となっているMOSトランジスタにリーク電流が発生する。また、製造プロセスによっては、NチャンネルMOSトランジスタとPチャンネルトランジスタとのリーク電流が等しいとは限らない場合があり、発振回路のような回路構成によっては、動作に問題を引き起こす可能性が高い。

【解決手段】本発明にかかる半導体装置は、制御電圧により駆動力が変化する第1のトランジスタを有する保護回路と、前記保護回路と同一の回路構成を有するモニター回路と、前記モニター回路が出力する電圧と、基準電圧との比較結果に基づいて前記制御電圧を生成する制御電圧生成回路とを有する。

(もっと読む)

発振回路

【課題】寄生容量のために発振波形が接地線側または電源線側に引き込まれることを抑制し、発振出力端子からはフル振幅の正常な発振波形が出力される発振回路を提供する。

【解決手段】圧電振動子Xの両端子が増幅器Aの入出力端子に接続され、増幅器Aの出力端子から発振波形が出力される発振回路において、増幅器Aの入力側に、P型拡散層とN型拡散層を有するダイオード型のESD保護回路B1が接続されている。増幅器Aの入力側のESD保護回路B1がP型拡散層とN型拡散層を有するダイオード型であるため、発振状態で増幅器Aの入力側で接地線側または電源線側に流れる電流はジャンクションリークのみで、発振波形が引き込まれるほどには電流は流れず、増幅器Aの入力側でも出力側でも発振波形はフル振幅波形を得ることが可能で、高周波で発振させるときでも、発振出力端子OUTからフル振幅波形を出力させることが可能となる。

(もっと読む)

発振回路、電子回路、これらを備えた半導体装置、時計及び電子機器

【課題】入出力端子を介して外部から侵入するサージ電圧から前記主要回路部分を保護することができ、しかも発振回路の電源電圧の変動の影響を受けることなく、安定した周波数で発振することができる発振回路、電子回路、これらを備えた半導体装置、時計及び電子機器を提供すること。

【解決手段】主電源の電源電圧の変動の影響を受けることなく、安定した周波数で発振することができる発振回路を提供すること。

発振回路40に設けられた静電保護回路200は、信号路と前記定電圧Vreg側との間に接続され、信号路に侵入する第1の極性の静電圧をダイオード72を介してバイパス用定電圧Vreg側へバイパスさせる第1の静電保護回路部210と、前記信号路とアース側との間に接続され、信号路に侵入する第2の極性の静電圧をダイオード74を介してアース側へバイパスさせる第2の静電保護回路部220とを含む。

(もっと読む)

表面実装用の水晶発振器

【課題】水晶振動子単体の独立した電気的特性を測定できて、しかもICチップの電気的な破壊を防止し、測定を容易にした表面実装発振器を提供する。

【解決手段】一対の励振電極11(ab)を有する水晶片3と発振回路を形成して水晶端子を有するICチップ2とを底面に実装電極を有する容器本体1内に収容した表面実装用の水晶発振器において、水晶片3の引出電極12(ab)に接続する水晶接続端子14(ab)とICチップ2の水晶端子に接続するICチップ接続端子10(ab)との接続線路15を、段部上で分断する。そして、水晶測定端子17(ab)の形成された側面とは異なる同一側面に延出する。次に、容器本体1の外表面に設けた水晶測定端子17(ab)によって、水晶振動子(水晶片3)の各特性を測定する。そして、水晶振動子の測定後に、例えば導電性接着剤13によって、分断した接続線路15の分割線路端子19を接続した構成とする。

(もっと読む)

圧電発振器

【課題】簡易な構造で小型化に対応可能であり、かつ発振回路の後段にバッファ回路を必要とせずに、出力負荷による影響を抑えることが可能な圧電発振器を提供することを目的とする。

【解決手段】電源と接地との間にPチャネル型のMOS−FETとNチャネル型のMOS−FETとの直列接続によるCMOS構造にて構成されたインバータ増幅器と第1の負荷インピーダンスとの接続回路を挿入し、前記インバータ増幅器の入力と接地との間に圧電振動子と周波数調整回路との直列回路を挿入し、前記インバータ増幅器の入力と前記インバータ増幅器と前記第1の負荷インピーダンスとの接続点に第2の負荷インピーダンスを直列に挿入接続し、更に、前記インバータ増幅器の入出力間に抵抗を接続することにより圧電発振発振器を構成したことを特徴とする。

(もっと読む)

1 - 11 / 11

[ Back to top ]