Fターム[5J079FB46]の内容

電気機械共振器を用いた発振回路 (23,106) | 回路要素 (2,263) | 波形整形回路 (9)

Fターム[5J079FB46]に分類される特許

1 - 9 / 9

バッファ回路

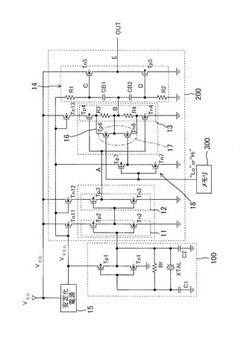

【課題】出力波形を高調波が発生しない様に調整する事ができ、高次高調波の抑圧効果の高い水晶発振回路の提供。

【解決手段】水晶振動子を振動源とする発振回路部と、この発振回路部の出力信号を入力とするCMOSトランジスタのインバータからなる複数段のバッファ回路部11、12、13と、このバッファ回路部の出力から直流成分をカットするキャパシタCB1、CB2を介して増幅するCMOSプッシュプル型増幅回路14とを備えた水晶発振回路に於いて、バッファ回路部13のCMOSトランジスタTp4とCMOSトランジスタTn4間に抵抗素子R3、R4を接続し、その中間点はバッファ回路部13の出力として、前記抵抗素子と前記キャパシタとからなる時定数で出力信号の波形成形を行い、且つ前記抵抗素子のバイパス回路16をメモリ設定にて、MOSスイッチ手段17のオン/オフ切り替えにより可能とするメモリを備えてなる。

(もっと読む)

水晶発振装置および半導体装置

【課題】低負荷容量値対応の水晶振動子を十分に適用することが可能な水晶発振装置を提供する。

【解決手段】例えば、配線基板PCB上に、発振入力信号XIN用の配線パターンLN_XINと、発振出力信号XOUT用の配線パターンLN_XOUTを設け、その間の領域に接地電源電圧VSS用の配線パターンLN_VSS1bを配置する。LN_XINとLN_XOUTの間には水晶振動子XTALを接続し、その負荷容量となる容量Cg,Cdの一端をLN_VSS1bに接続する。更に、これらの配線パターンを囲むようにVSS用の配線パターンLN_VSS1aを配置し、加えて、下層にもVSS用の配線パターンLN_VSSnを配置する。これらによって、XINノードとXOUTノード間の寄生容量の低減や、当該ノードのノイズ耐性の向上等が可能になる。

(もっと読む)

レベルシフト回路及びそれを用いた発振器

【課題】 出力波形の割れや抜けを無くし、回路の誤動作が防止される低電圧動作のレベルシフト回路を提供する。

【解決手段】 レベルシフト回路は、電源端子VDDにソースを接続した第1のPMOSトランジスタP1と、接地端子GNDにソースを接続したNMOSトランジスタN1と、PMOSP1のドレインとNMOSN1のドレインとの接続点に接続された出力端子OUTと、NMOSN1のゲートに接続された入力端子INと、電源端子VDDにソースを接続し、PMOSP1のゲートにドレイン及びゲートを接続し、このドレインを第2の抵抗R2を介して接地端子GNDに接続した第2のPMOSトランジスタP2とを有し、PMOSP1及びP2は、カレントミラー回路を構成している。レベルシフト回路の出力波形の割れや抜けが無くなって誤動作を防止することが可能になる。

(もっと読む)

集積回路装置及び電子機器

【課題】発振回路の性能を維持しながら静電気保護耐圧を向上できる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、振動子XTALの一端に接続される第1のパッドP1と、振動子XTALの他端に接続される第2のパッドP2と、振動子XTALの発振用のバッファー回路BFと、第1のパッドP1側の第1の接続ノードNC1と、バッファー回路BFの入力ノードNIとの間に設けられる第1の保護抵抗素子R1と、第2のパッドP2側の第2の接続ノードNC2と、バッファー回路BFの出力ノードNQとの間に設けられる第2の保護抵抗素子R2と、第1、第2の接続ノードNC1、NC2の一方に接続される容量回路CX1(CX2)とを含む。

(もっと読む)

圧電発振器

【課題】圧電発振器にスリープモードを備える。

【解決手段】圧電振動子100を発振させた発振信号Vpを出力する発振回路110と、発振回路110に電流Idを供給する電流源回路120と、発振回路110から出力された発振信号Vpを整形した出力信号OUTを出力するバッファ回路130と、スリープモードとノーマルモードとを切り替える制御信号SLを入力する制御端子140と、を含み、電流源回路120は、制御信号SLがスリープモードの時はノーマルモードの時に比べて発振回路110に供給する電流Idが少なくなるように切り替える第1の切替部124を含み、バッファ回路130は、制御信号SLがスリープモードの時はバッファ回路130を構成する素子への電流の供給を止める第2の切替部132と、制御信号SLがスリープモードの時は発振信号Vpが出力されないように切り替える第3の切替部133と、を含む圧電発振器1。

(もっと読む)

パルス発生回路

【課題】発振周波数が数MHz〜GHzの高周波用に適用可能であり、かつ消費電力が少ない、定電流回路を用いたパルス発生回路を提供すること。

【解決手段】パルス発生回路は、電源間に定電圧回路1を有し、電流制御素子7と波形発生部9とを直列に接続して、それらを定電圧回路1と並列に接続して構成されている。そして、波形発生部9は、平滑回路2と、水晶発振回路4と、水晶発振回路4からの出力を受けて最終出力波形のデューティ比を調整する出力デューティ調整回路5と、水晶発振回路4の発振波形と最終出力波形との位相差を調整する位相調整回路6と、を並列に接続して構成されている。使用する水晶振動子の周波数によっては、位相調整回路6の替わりに分周回路を並列に接続して構成されている。

(もっと読む)

ECL出力圧電発振器

【課題】小型化で負荷変動に強く、しかも理想的な出力波形を得ることができるECL出

力圧電発振器を提供する。

【解決手段】コルピッツ型の水晶発振回路11、ECL回路12、結合コンデンサC3、

及びデカップリング抵抗R5とから構成され、水晶発振回路11とECL回路12との間

を結合する結合コンデンサC3と、ECL回路12との間にデカップリング抵抗R5を挿

入して接続するようにした。これにより、水晶発振回路11から出力される発振出力信号

の波形調整が可能になると共に、水晶発振回路11に対するECL回路12の影響を小さ

くすることが可能になる。

(もっと読む)

発振器用基板

【課題】VCXOとPXOとに共有可能な印刷抵抗を使用した発振器用基板を提供する。

【解決手段】水晶振動子Y1と水晶発振回路11とから構成されるPXO、または圧電発

振回路と周波数電圧制御回路12とから構成されるVCXOに使用可能な発振器用基板で

あって、VCXOを構成する抵抗部品のうち、短絡部品に交換することによりVCXOを

PXOに変更できる抵抗R2以外を印刷抵抗により形成した。これにより1つの発振器用

基板21をVCXOとPXOにおいて共有して使用することができるため、発振器の低コ

スト化を実現することができる。また、VCXOをPXOに変更するための抵抗R2以外

を印刷抵抗により形成しているため圧電発振器を小型化することが可能になる。

(もっと読む)

発振回路

【課題】発振部の後段に接続する波形整形部の内部容量が発振部の発振周波数に与える影響を排除し、発振回路の異常発振を防止すること。

【解決手段】この発振回路は、所望の周波数で発振して発振信号を出力する発振部10と、前記発振部10の出力端に接続され前記発振信号を波形整形する波形整形部20と、前記発振部10と前記波形整形部20との間に介挿された抵抗30とを具備し、抵抗30と波形整形部20の内部容量22とでローパスフィルタを形成する。

(もっと読む)

1 - 9 / 9

[ Back to top ]