Fターム[5J079HA24]の内容

電気機械共振器を用いた発振回路 (23,106) | 実装、構造 (6,548) | 部品構造 (2,481) | 回路部素子の構造 (121) | コンデンサの構造 (20)

Fターム[5J079HA24]に分類される特許

1 - 20 / 20

水晶デバイスおよび電子機器

【課題】水晶デバイスおよび電子機器の小型化を図ること。

【解決手段】実施形態によれば、容器体と、水晶素子と、電解質部材とを備える水晶デバイスが提供される。容器体は、1または複数のキャビティを有する。水晶素子は、キャビティ内に配置される。電解質部材は、少なくとも一部がキャビティ内に配置される。また、実施形態によれば、これらの容器体と、水晶素子と、電解質部材とを備える水晶デバイスを搭載した電子機器が提供される。

(もっと読む)

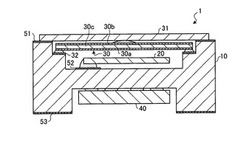

半導体装置

【課題】プロセスを簡素化し低コスト化を実現するとともに、さらに、システムを簡素化しノイズ対策を可能にするMEMSレゾネータ及びMEMSレゾネータの製造方法を提供する。

【解決手段】MEMSレゾネータの製造方法は、基板10上に形成された半導体デバイスとMEMS構造体部4とを有するMEMSレゾネータ2の製造方法であって、半導体デバイスは、上部電極30と下部電極26とを有するONOキャパシタ部6と、CMOS回路部8と、を含み、ONOキャパシタ部6の下部電極26を、第1シリコン層26を用いて、形成する。MEMS構造体部4の下部構造体16とONOキャパシタ部6の上部電極30とを、第2シリコン層52を用いて、形成する。及び、MEMS構造体部4の上部構造体18とCMOS回路部8のゲート電極34とを、第3シリコン層54を用いて、形成する。

(もっと読む)

半導体装置

【課題】プロセスを簡素化し低コスト化を実現するとともに、さらに、システムを簡素化しノイズ対策を可能にするMEMSレゾネータ及びMEMSレゾネータの製造方法を提供する。

【解決手段】MEMSレゾネータの製造方法は、基板10上に形成された半導体デバイスとMEMS構造体部4とを有するMEMSレゾネータ2の製造方法であって、半導体デバイスは、上部電極30と下部電極26とを有するONOキャパシタ部6と、CMOS回路部8と、を含み、ONOキャパシタ部6の下部電極26を、第1シリコン層26を用いて、形成する。MEMS構造体部4の下部構造体16とONOキャパシタ部6の上部電極30とを、第2シリコン層52を用いて、形成する。及び、MEMS構造体部4の上部構造体18とCMOS回路部8のゲート電極34とを、第3シリコン層54を用いて、形成する。

(もっと読む)

圧電振動片、圧電発振器

【課題】十分な周波数可変量を有する電圧制御型の圧電発振器、および、それに用いる圧電振動片を提供する。

【解決手段】水晶振動片1において、水晶基板の一方の主面側の第1突部5A上には、駆動用の電極である第1励振電極15Aが設けられ、水晶基板の一端側近傍には第1外部接続電極18Aが設けられている。第1励振電極15Aと第1外部接続電極18Aとは、第1電極間配線16Aにより電気的に接続されている。同様に、水晶基板の他方の主面の第2突部5B上には、第1励振電極15Aの対向電極である第2励振電極15Bが設けられ、水晶基板の一端側近傍の上記第1外部接続電極18Aと平面視で重ならない領域に設けられた第2外部接続電極18Bとが、第2電極間配線16Bにより電気的に接続されている。第1電極間配線16Aと、第2電極間配線16Bとは、平面視で重なる立体交差領域17を有している。

(もっと読む)

圧電デバイス及び圧電デバイスの製造方法

【課題】 透明ベースの外部端子側から切断可能である電気回路素子の接続電極の配線の一部を形成した圧電デバイスを提供する。

【解決手段】圧電デバイス(100)は、励振電極が形成された圧電振動片(21)と圧電振動片を囲む外枠部(22)とを有する水晶フレーム(20)と、圧電振動片を発振させる電気回路素子(IC)と、一方の面に形成され電気回路素子と接続される接続電極と、一方の面とは反対面に形成された外部端子とを有し外枠部の一方の面に接合する透明ベース(30)と、外枠部の他方の面に接合するリッド(10)と、を備える。

(もっと読む)

圧電発振器

【課題】圧電発振器の位相雑音(C/N)を低減する手段を得る。

【解決手段】圧電振動子Xと、少なくとも負荷容量C1、C2と周波数調整回路12を含

む発振用の増幅回路を有するICチップ5と、外部容量C5〜C7を有し、圧電振動子X

及びICチップ5を搭載可能な回路基板と、を備え、負荷容量C1、C2と外部容量C5

〜C7とが並列回路を成すように、負荷容量C1、C2と外部容量C5〜C7とを導体を

介して導通するように構成した。

(もっと読む)

圧電デバイスおよび電子機器

【課題】薄型化した圧電デバイスおよびこの圧電デバイスを搭載した電子機器を提供する。

【解決手段】圧電デバイス10は、ICチップ12と圧電振動片30とを積層方向に配置したものであって、ICチップ12の一方の面に内部パッド16および絶縁層を設け、前記絶縁層と前記一方の面との間に再配置配線18を設けて、再配置配線18の一端を内部パッド16に接続し、他端を前記一方の面の周縁部に配置し、前記他端には前記絶縁層を貫通する導通手段を設け、前記導通手段が前記絶縁層の外側表面に露出した部分に、ワイヤ28が接合する再配置内部パッド16を設け、ワイヤ28を配設した側とは反対の平面方向へ再配置内部パッド16からずれるとともに、内部パッド16に対向して圧電振動片30を配設した構成である。

(もっと読む)

MEMSレゾネータ及びMEMSレゾネータの製造方法

【課題】プロセスを簡素化し低コスト化を実現するとともに、さらに、システムを簡素化

しノイズ対策を可能にするMEMSレゾネータ及びMEMSレゾネータの製造方法を提供

する。

【解決手段】MEMSレゾネータの製造方法は、基板10上に形成された半導体デバイス

とMEMS構造体部4とを有するMEMSレゾネータ2の製造方法であって、半導体デバ

イスは、上部電極30と下部電極26とを有するONOキャパシタ部6と、CMOS回路

部8と、を含み、ONOキャパシタ部6の下部電極26を、第1シリコン層26を用いて

、形成する。MEMS構造体部4の下部構造体16とONOキャパシタ部6の上部電極3

0とを、第2シリコン層52を用いて、形成する。及び、MEMS構造体部4の上部構造

体18とCMOS回路部8のゲート電極34とを、第3シリコン層54を用いて、形成す

る。

(もっと読む)

表面実装用の水晶発振器

【課題】金属カバーの封止後の周波数調整を容易にした表面実装発振器の提供。

【解決手段】複数のセラミック層からなる凹状とした容器本体1内に発振閉ループを形成するICチップ2と水晶片3とを収容した表面実装用の水晶発振器において、前記発振閉ループ内に並列接続とした複数の容量を形成する複数の対をなす第1電極と第2電極を形成し、前記第1電極と接続する配線路を前記容器本体1の外側面に延出して露出し、前記配線路を切断して前記並列接続の容量値を可変し、発振周波数を調整した構成とする。

(もっと読む)

発振装置の製造方法及び発振装置

【課題】発振装置の発振周波数の調整において、歩留りを向上させやすくする。

【解決手段】半導体基板7に形成された第1電極に、圧電体で構成される圧電体膜を重ねて形成し、前記圧電体膜に、前記圧電体膜を挟んで前記第1電極に対向する第2電極を形成して、前記第1電極、前記圧電体膜及び前記第2電極を構成の一部として有する第1キャパシタを形成する工程と、容器3の底となる第3基板45に、容器3の内側及び外側の間を貫通する貫通孔61が設けられた容器3内に、半導体基板7を、半導体基板7が貫通孔61を塞ぐように、且つ平面視で、前記第1キャパシタが貫通孔61に重なるように実装する工程と、前記発振回路の発振周波数を測定した結果に基づいて、半導体基板7によって塞がれた貫通孔61内に容器3の外側から圧力P1を付与した状態で、貫通孔61を容器3の外側から塞ぐ工程と、を有する。

(もっと読む)

発振回路

【課題】寄生容量のために発振波形が接地線側または電源線側に引き込まれることを抑制し、発振出力端子からはフル振幅の正常な発振波形が出力される発振回路を提供する。

【解決手段】圧電振動子Xの両端子が増幅器Aの入出力端子に接続され、増幅器Aの出力端子から発振波形が出力される発振回路において、増幅器Aの入力側に、P型拡散層とN型拡散層を有するダイオード型のESD保護回路B1が接続されている。増幅器Aの入力側のESD保護回路B1がP型拡散層とN型拡散層を有するダイオード型であるため、発振状態で増幅器Aの入力側で接地線側または電源線側に流れる電流はジャンクションリークのみで、発振波形が引き込まれるほどには電流は流れず、増幅器Aの入力側でも出力側でも発振波形はフル振幅波形を得ることが可能で、高周波で発振させるときでも、発振出力端子OUTからフル振幅波形を出力させることが可能となる。

(もっと読む)

発振回路

【課題】周波数可変幅を拡大でき、容量素子の形成領域の面積縮小により小型化できるほか、固定容量素子に金属電極を用いて、容量としての機能を向上し、さらには、金属電極のパターニングの際にポリシリコン電極のエッジ部でオーバーエッチングによるシリコントレンチを起こす虞がない容量素子を備えた発振回路を提供する。

【課題の解決手段】増幅用のインバータと、発振周波数制御用の可変容量素子101,102と、直流信号遮断用の固定容量素子71,73,74,72と、振動子を外付けするための一対の端子と、周波数制御用信号を入力するための端子を備えた半導体集積回路に搭載する発振回路であって、半導体基板表面に可変容量素子101,102を形成し、この可変容量素子101,102の上に設けたフィールド酸化膜25a上に、ポリシリコン電極72と、絶縁膜73,74と、金属電極71とを順次積層して固定容量素子を形成する。

(もっと読む)

高周波フロントエンドモジュール及びその製造方法

【課題】高密度化を実現しつつ、加工精度や組立精度を向上することができる高周波フロントエンドモジュールを提供する。

【解決手段】高周波フロントエンドモジュール1において、第1の電極31、この第1の電極31上の誘電体膜32及びこの誘電体膜32上の第2の電極33を有し、第1の電極31、誘電体膜32及び第2の電極33の各々の膜厚及び面積のばらつきが0.2%以内に制御されたキャパシタ3と、キャパシタ3を表面上に作り付ける基板2とを備える。

(もっと読む)

発振器用ICチップ及びこれを用いた表面実装用の水晶発振器

【目的】コンデンサが接続される一対のIC端子間の導電路を排除して、特に雑音を低減した表面実装発振器を提供する。

【構成】コンデンサ4が電気的に接続する少なくとも一対の第1端子10(ab)を含む複数のIC端子を一主面に有し、水晶振動子とともに発振回路を形成する回路素子を集積化してなる発振器用ICチップ2において、前記一対の第1端子10(ab)と貫通電極12を経て電気的に接続するとともに、前記コンデンサ4が直接的に接続される一対の第2端子13(ab)を他主面に有する構成とする。また、これを用いて表面実装発振器を構成する。

(もっと読む)

圧電振動子の周波数調整方法および圧電振動子

【課題】 発振周波数の調整を容易、迅速に行なえるようにする。

【解決手段】 圧電振動子20は、パッケージ22に収容した圧電振動片を有する。パッケージ22の下面34には、コンデンサブロック38、40が設けてある。各コンデンサブロック38、40は、複数のコンデンサ素子48(48a〜48d)、50(50a〜50d)からなる。これらのコンデンサ素子48、50は、静電容量が公比を2とする等比数列となるように形成してある。各コンデンサ素子48の一方の電極52(52a〜52d)は、配線パターン42を介して外部電極36aに接続してある。各コンデンサ素子50の一方の電極52は、配線パターン46を介して外部電極36dに接続してある。外部電極36a、36dは、圧電振動片の励振電極に電気的に接続してある。配線パターン42、46の適宜の箇所を切断することにより、容量値を変えて周波数調整をすることができる。

(もっと読む)

弾性表面波装置

【課題】 集積回路とSAW振動子とを半導体基板上に一体化した場合においても、チップ面積の増大を抑制しつつ、SAW振動子に直流電圧がかからないように集積回路とSAW振動子とを接続する。

【解決手段】 集積回路12から引き出されたパッド電極15a、15bを半導体チップ11に形成するとともに、半導体チップ11上には、パッド電極15a、15bにかかるように配置された薄膜圧電体13を積層し、薄膜圧電体13上には、IDT電極14a、14bからそれぞれ引き出されたパッド電極16a、16bをそれぞれ形成し、パッド電極16a、16bは、薄膜圧電体13を介してパッド電極15a、15bとそれぞれ対向するように配置する。

(もっと読む)

周波数可変発振器

【課題】 実装面積の増大を抑制しつつ、周波数可変発振器に用いられる可変容量素子の大容量化を図る。

【解決手段】 周波数可変発振器には、帰還回路B11が形成された半導体チップ11が設けられるとともに、SAW振動子W11および可変容量コンデンサC11は半導体チップ11上に積層され、SAW振動子W11を構成する薄膜圧電体層14を用いることで、可変容量コンデンサC11を形成する。

(もっと読む)

MOS容量型半導体装置およびこれを用いた水晶発振器

【課題】

小型で且つ良好な容量変化の可能な高周波用の容量素子を構成する半導体装置を提供する。

【解決手段】

基板表面にゲート絶縁膜を介して形成されたゲート電極と、前記ゲート電極をはさむように配されるソース・ドレイン領域と、前記基板にコンタクトするためのコンタクト拡散領域を備えたバックゲートとを具備し、ソースまたはドレイン領域とゲート電極との間、およびゲート電極とバックゲートとの間に印加される電圧を調整することにより、ゲート絶縁膜に蓄積される電荷を調整可能にしたMOS容量型半導体装置において、前記ソース・ドレイン間距離または、前記バックゲートと前記ゲート電極との間隔とが、前記印加される電圧の周期内に、電子または正孔が前記ゲート絶縁膜と基板との界面に蓄積されうるように決定される。

(もっと読む)

コンデンサ及びそれを用いた発振回路

【課題】 低温部から高温部に亘り、振動子の温度による周波数変化特性を容易に補償することができるコンデンサ及びそれを用いた発振回路を提供する。

【解決手段】 温度による静電容量変化特性を有するコンデンサ1であって、誘電体2と、前記誘電体2に対向するバイメタル4とを備え、前記誘電体2には第一の電極3が形成され、前記バイメタル4には第二の電極としての導電性ゴム部材5(または導電性薄膜)が設けられ、温度変化により前記バイメタル4が湾曲し、前記誘電体2と前記導電性ゴム部材5(または導電性薄膜)の密着有効対向面積に応じて、前記第一の電極3の実効面積が変化し、静電容量が変化する。

(もっと読む)

複数の基板を備える構造、その構造の製造方法、および、その構造を用いた水晶発振器

【課題】基板の板面面積を有効活用して安価に小型化を促進できる複数の基板を備える構造を提供することである。

【解決手段】本発明の複数の基板を備える構造は、チップ状の回路素子がそれぞれ配設された複数の基板が電気的な配線を兼ねた支柱によって接続されて構成される複数の基板を備える構造において、前記複数の基板間を接続する支柱の少なくとも1つは前記回路素子のいずれかをも兼ねて構成されるとともに、前記支柱を兼ねた回路素子は、基板上に立たせるように配置されることを特徴とする複数の基板を備える構造である。

(もっと読む)

1 - 20 / 20

[ Back to top ]