Fターム[5J081FF03]の内容

LC分布定数、CR発振器 (9,854) | 構成要素(発振用能動素子、周波数決定素子以外) (1,204) | 回路構成 (543) | 分岐、結合 (7)

Fターム[5J081FF03]に分類される特許

1 - 7 / 7

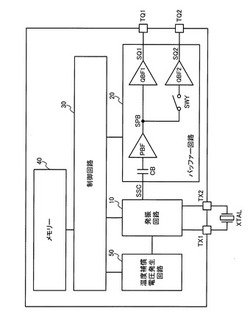

回路装置及び電子機器

【課題】無駄な電力消費やノイズの悪影響等を抑制できる回路装置及び電子機器等の提供。

【解決手段】回路装置は発振回路10とバッファー回路20を含む。バッファー回路20は、プリバッファーPBFと第1、第2の出力バッファーQBF1、QBF2を含む。第1のモードでは、第1の出力バッファーQBF1が動作イネーブル状態に設定され、第2の出力バッファーQBF2が動作ディスエーブル状態に設定される。第2のモードでは、第1の出力バッファーQBF1及び第2の出力バッファーQBF2が動作イネーブル状態に設定される。第1のモードでは、プリバッファーPBFの駆動能力が、第2のモードに比べて低い駆動能力に設定される。

(もっと読む)

発振器及び位相同期回路

【課題】十分に高い周波数帯域において、広帯域にわたって柔軟に発振周波数を調整すること。

【解決手段】信号線131は、電源から直流電圧Vdcが印加されると、電源に接続された始端を節とし、終端を腹とする4分の3波長の定在波を発生させる。ストリップ132−1〜132−nは、それぞれスイッチ133−1〜133−nを介してグランド層に接続されている。スイッチ133−1〜133−nは、切替制御部140による制御に従って、それぞれストリップ132−1〜132−nとグランド層との接続及び非接続を切り替える。スイッチ133−1〜133−nの接続及び非接続を切り替えることにより、擬似的に信号線131とグランド層の間の距離が調節され、伝送線路部130における実効誘電率が変化して、定在波の周波数を調整することができる。

(もっと読む)

位相同期発振器アレイ

【課題】小型でIC化が可能な位相同期発振器を実現すること。

【解決手段】 位相同期した複数の発振信号を得る位相同期発振器アレイにおいて、位相が180度異なる2つの信号を入力する第1入力端子と第2入力端子とを有したn個の第1差動増幅器から第n差動増幅器と、1≦k<nの全ての自然数kに対して、第k差動増幅器の第2入力端子と第k+1差動増幅器の第1入力端子との間の全て、及び、第n差動増幅器の第2入力端子と第1差動増幅器の第1入力端子との間を、それぞれ、逆相で結合するn個のフィルタFと、を設けたことを特徴とする位相同期発振器アレイ。フィルタFは、一方の差動増幅器1の第2入力端子B12と接地間に配設された第2インダクタL12と、他方の差動増幅器2の第1入力端子B21と接地間に配設された第1インダクタとL21、一方の差動増幅器1の第2入力端子と他方の差動増幅器2の第1入力端子との間を接続する第3容量C15と第3インダクタL23との直列接続回路とを有する。

(もっと読む)

フィルタ回路及び電圧制御発振回路

【課題】双方の信号線路の遅延を容易に一致させることができると共に、不要信号を相殺することができる。

【解決手段】この電圧制御発振回路は、発振回路部1と、発振信号を分岐すると共に互いに位相の反転した第1及び第2の信号を別々に出力する出力分波回路2と、出力分波回路2の出力段に並列に接続され同一構成を有し、トラップ周波数が異なるトラップ回路3、4と、トラップ回路の出力を合成する出力再合成回路とを備える。発振回路部1の電圧制御信号をトラップ回路3、4のバラクタダイオード32,34に印加してトラップ回路3、4のトラップ周波数を発振周波数に連動させる。

(もっと読む)

インピーダンス変換回路、高周波回路、及びインピーダンス変換回路のインピーダンス変換特性調整方法

【課題】誘電体チップ等の付加や、スタブ長の長いオープンスタブを用いることなく、インピーダンス変換の特性調整を可逆的に且つ微調整可能なようにしたインピーダンス変換回路及びそれを備えた高周波回路を構成する。

【解決手段】スタブST2の長さを固定したままスタブST1の長さを短くすると、インピーダンスZbはアドミッタンスチャート上を矢印A1で代表する方向に移動する。また、スタブST1の長さを固定したままスタブST2の長さを短くすると、インピーダンスZbはアドミッタンスチャート上の等コンダクタンス円上を矢印A2で代表して示すように移動する。したがって図中スミスチャートの中心とショート点とを直径とする円内では、インピーダンス軌跡は、スタブST1,ST2のトリミングによってインピーダンスは互いに可逆的に調整できることになる。

(もっと読む)

発振回路及びこれを備えた通信装置

【課題】高レベルでしかも高Q値の出力を得ることができる発振回路及びこれを備えた通信装置を提供する。

【解決手段】発振回路1を第1スロット線路2と第2スロット線路3と第3スロット線路4とFET5で構成した。第1スロット線路2を出力ポートとし、第2スロット線路3を、ショートスタブ30とDCカット線路31で構成し、ショートスタブ30の長さをλg/2〜3λg/4に設定した。また、第3スロット線路4も、ショートスタブ40とDCカット線路41で構成し、ショートスタブ40の長さをλg/4〜λg/2に設定した。そして、ゲート電極Gとドレイン電極Dとが第2スロット線路3を、ドレイン電極Dとソース電極Sとが第3スロット線路4を、ソース電極Sとゲート電極Gとが第1スロット線路2をそれぞれ挟むように、FET5を実装した。帯域反射型共振器6は長さλg/4のショートスタブである。

(もっと読む)

発振回路

【課題】 小型化かつ位相雑音を低減することができる発振回路を提供することを課題とする。

【解決手段】 差動対を構成する第1及び第2のトランジスタ(101,102)と、第1及び第2のトランジスタの第1の端子側に接続される出力合成回路(103)と、第1及び第2のトランジスタの第2の端子側に接続される電流源(106)とを有する発振回路が提供される。

(もっと読む)

1 - 7 / 7

[ Back to top ]