Fターム[5J104NA42]の内容

暗号化、復号化装置及び秘密通信 (108,990) | 構成要素 (27,346) | 物理的構成要素 (16,068) | 耐タンパーモジュール (369)

Fターム[5J104NA42]に分類される特許

361 - 369 / 369

差分電力解析を妨害する命令マスクや他の手法を備えた暗号アーキテクチャ

タイムライン・アラインメントを利用する情報漏洩攻撃を妨げる装置及び方法。上記装置及び方法によって、攻撃者が暗号化を解読することを可能にするために漏洩情報の時間的なアラインメントを行うことが可能でないようにランダムな数の命令が暗号化アルゴリズムに挿入される。  (もっと読む)

(もっと読む)

ホモグラフィックマスキングにより暗号アセンブリを保護する方法

本発明は、(cz+d)が0でなくf(−d/c)=a/cである場合に、f(z)=(az+b)/(cz+d)タイプのホモグラフィック関数fを使用する暗号計算プロセスを遂行することによって、アセンブリを保護する方法に関し、ここで関数fがマスク化変数に作用する同方法において、任意のkについてxが関数fの入力であってy=f(x+k)が関数fの出力である場合に、直接的にマスク化値x+m_i(XORタイプの加法マスキング)からマスク化値y+m_jへとなるように、(ax+b)/(cx+d)と定義される、無限量の加算をともないGF(2^k)に作用する数個の変換と、二つの点を交換する変換との合成を用いて、この演算を遂行することを特徴とする。 (もっと読む)

暗号又は復号を行うコンピュータシステム及びコンピュータプログラム

処理時間を観測するタイミング攻撃に対する耐性を有するコンピュータシステムを提供する。 コンピュータシステムは、平文又は暗号文に係る部分データを対応する変換データに変換するプロセスを経て、平文又は暗号文を暗号化又は復号する。変換表は、ライン表領域の先頭位置において、部分データに対応する1個の変換データを含み、他の位置において、前記変換に無関係のデータを含む。コンピュータプログラムは、取得した部分データを用いて、対応する前記変換データの前記変換表における位置を算出する演算命令群と、前記変換表から、算出された前記位置に存する前記変換データを読み出す読出命令群とを含む。 (もっと読む)

集積回路を備えた装置

本発明は、機能モジュール(2)を備えた集積回路(1)であって、該機能モジュール(2)は、データを処理しかつプログラムを実行することができる中央処理ユニット(4)とキャッシュメモリ(5)とを有している。この形式のモジュールの不正操作に対する

セキュリティの保証はこれまで非常に煩雑でかつ必然的にコストも高くなった。ここで本発明は、機能モジュール(2)が暗号化ユニット(6)を有し、該暗号化ユニットを用いてデータを暗号化可能および暗号解除可能とすることによって不都合な点が取り除かれるようにする。  (もっと読む)

(もっと読む)

パケット暗号処理代理装置

インターネット2に接続された相手装置3からパケットが受信されると、そのパケット中の送信元及び送信先のIPアドレス・ポート番号、プロトコルにより、フィルタ情報記憶部15を参照して、復号化するかバ

イパスするかを復号化判断部16で判断し、復号化と判断されると、暗号通信路情報記憶部12から、相手装置3とIPSec機能を持たない端末装置5とで予め合意された暗号通信路情報に基づいて受信パケットを復号化して端末装置5へ送る。暗号通信路情報は相手装置3と端末装置5の間にIPSecに準拠したパケット通信路を確立するために用い、識別番号、暗号化処理か署名処理かのプロトコル情報、暗号アルゴリズムや鍵情報、IPアドレス・ポート番号などである。相手はトランスポートモードを使用できる。  (もっと読む)

(もっと読む)

IC侵入検出

本発明は、暗号処理のための電子装置であって、接続手段を介して結合されている少なくとも2つの電子回路(IC、CC、CP)を有し、前記接続手段は、前記2つの電子回路の間にデータ信号を伝達する電子装置に関する。前記電子装置は、前記接続手段の容量の偏差を監視する監視回路(401)を更に有する。前記偏差が所定値を超えている場合、警告信号(411)が生成される。  (もっと読む)

(もっと読む)

テレビジョン受像機および電子デバイス装置

暗号解読部と映像表示部とが1つの筐体に格納されているテレビジョン受像機において、暗号化されたディジタル映像信号もしくは、アナログ映像信号に対して著作権保護を図る。 ディジタル映像信号入力端子に暗号化されたディジタル映像信号が入力されると、デコード回路で暗号を解かれ、コピー可能な状態である暗号解読後映像信号を得たのち、映像表示部において視覚化する。ここで、筐体蓋が開けられるとデコード制御回路は、暗号鍵といった暗号解読に必要なパラメータを無意味なパラメータに変更してデコード回路へ出力するため、暗号解読後映像信号は暗号解読されていない映像信号となる。 一方、保守時には、釦群(18)から所定のコードを入力することで、正規の暗号解読パラメータをデコード回路(13)へ出力する。 (もっと読む)

電力解析攻撃対策保護

第1の組み合わせ論理回路を有した暗号処理のための電子回路であって、この組み合わせ論理回路は、入力データに第1セットの論理演算を行って出力データを生成するように構成され、当該出力データは、入力データに対して関数関係を有する。この電子回路はさらに、同じ入力データに第2セットの論理演算を行って出力データを生成するよう構成された少なくとも第2の組み合わせ論理回路をさらに有し、当該出力データは、入力データに対して同一の関数関係を有する。第1セットの論理演算は、第2セットの論理演算とは異なり、電子回路は、入力データに論理演算を行い出力データを生成するように、少なくとも第1の組み合わせ論理回路及び第2の組み合わせ論理回路を有するセットのうちの1つの組み合わせ論理回路をダイナミックに選択するように構成されている。

(もっと読む)

(もっと読む)

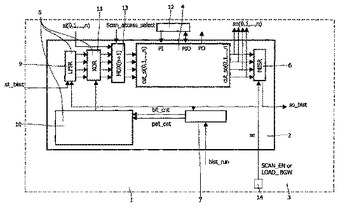

秘密サブモジュールを有する電子回路

本発明は、電子回路の残部に接続されるサブモジュールアセンブリ(2)を含む電子回路であって、前記サブモジュールアセンブリは、−機能を実行すると共にスキャンチェーンを有する秘密サブモジュール(4)と、−入力信号を前記スキャンチェーンにもたらすためのパターン発生器(5)及び前記スキャンチェーンからの出力信号を検査するための署名レジスタ(6)を含む組込自己テスト回路とを含む電子回路に関する。サブモジュールを秘密に保つため、スキャンチェーンは前記回路の残部に接続されていない。  (もっと読む)

(もっと読む)

361 - 369 / 369

[ Back to top ]