Fターム[5J106CC33]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数比較(弁別)回路 (250) | 周波数数値変換型 (8)

Fターム[5J106CC33]に分類される特許

1 - 8 / 8

自励発振型D級アンプおよび自励発振型D級アンプの自励発振周波数制御方法

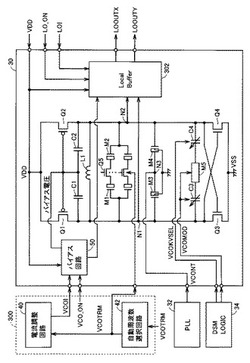

半導体装置

【課題】CMOSトランジスタによって構成されたVCOを備えた半導体装置において、発振信号の発振振幅のばらつきの抑制および低消費電力化を実現する。

【解決手段】VCO30は、CMOSトランジスタによって構成されたLCタンクVCOと、VCOの発振周波数帯域から一の発振周波数を選択するための周波数選択信号を生成する自動周波数選択回路42と、VCOの制御電圧を生成するPLL32と、周波数選択信号に基づいて差動型のMOSトランジスタのゲートに供給するバイアス電圧を調整するバイアス回路50とを備える。

(もっと読む)

サブサンプリングされた周波数ロックループを備える送受信機

タイム/デジタルコンバーター及びデジタル位相ロックループ

【課題】 本発明の目的は、入力される2つの信号の位相差だけでなく周波数の差まで検出することができるタイム/デジタルコンバーター及びこれを用いるデジタル位相ロックループを提供することを目的とする。

【解決手段】 タイム/デジタルコンバーターが開示される。本タイム/デジタルコンバーターは、第1信号及び第2信号を受信し、直列接続された複数の遅延素子を用いて第2信号を段階的に遅延させ、遅延された第2信号と第1信号とを比較して第1信号に対する第2信号の位相エラーを出力するコンバーターと、第1信号及び複数の遅延素子のノードのうち一つのノードから第3信号を受信し、第1信号及び第3信号に対する位相差を出力する位相周波数検出器と、位相周波数検出器の出力信号と第2信号を用いて、第1信号に対する第2信号の周波数エラーをデジタルコードに出力する周波数検出器と、を含む。これにより、本タイム/デジタルコンバーターは入力される2つの信号間の位相差だけでなく周波数の差まで検出することができる。

(もっと読む)

発振装置、受信装置および発振制御方法

【課題】発振周波数の制御の精度を向上させる。

【解決手段】検出部11は、基準信号の入力信号に対する周波数オフセットを検出する。コード生成部12aは、検出部11による周波数オフセットの検出状況に基づいて、所定ビット数のコードと周波数オフセットおよびDAC12bが電圧制御発振器13に印加する電圧との対応関係を設定する。また、コード生成部12aは、設定した対応関係に基づいて、周波数オフセットを補正する所定ビット数のコードを生成する。DAC12bは、コード生成部12aが生成したコードと上記の対応関係に基づいて、電圧制御発振器13に電圧を印加する。電圧制御発振器13は、DAC12bにより印加された電圧に応じた発振周波数の発振信号を出力する。

(もっと読む)

クロック生成回路およびその使用方法

【課題】基準信号の周波数を逓倍又は分周したクロック信号を生成するクロック生成回路において、一つの基準信号から任意周波数のクロック信号を発生可能とする。

【解決手段】クロック生成回路1は、リング状に連結したm個の遅延素子DUからなるパルス遅延回路10と、各遅延素子DUから順次出力される通過信号P1〜Pmに基づき、基準信号CKIの周期を遅延素子DUでの遅延時間を単位として表した周期データDTを生成する周期測定部20と、除数又は乗数として使用される設定値MNを格納する設定値レジスタ50と、周期データDTに、設定値MNを乗・除してクロック信号の出力周期を表す制御データCDを生成する制御部30と、制御データCDと通過信号P1〜Pmとに基づき、基準信号CKIを分周又は逓倍したクロック信号CKOを出力する出力部40とを備え、実数で表された設定値MNを用いる。

(もっと読む)

クロック生成制御回路

【課題】 CPUの負荷を軽減することが可能なクロック生成制御回路を提供する。

【解決手段】 本願発明は、発振回路が出力するクロック信号のパルス数を所定期間カウントし、所定期間及び周波数に応じた設定値と等しくなったときにカウント制御信号の出力レベルを切り替えるカウンタと、所定期間を示すタイミング信号とカウント制御信号とのタイミングの誤差を検出し、誤差検出信号を出力する誤差検出回路と、を備え、周波数制御回路は、誤差検出信号に基づいて制御信号を生成することで、上記課題を解決することができる。

(もっと読む)

半導体集積回路

【課題】 バーンインテスト時のように低周波数の基準クロック信号3を入力した場合にも、電圧制御発振器などのアナログ回路の特性を低周波数用に切り替えることなく、通常時使用する周波数範囲で各構成回路を動作させストレスをかけることで、PLL回路の評価を可能にする半導体集積回路を提供する。

【解決手段】 基準クロック信号3が低周波数のため、電圧制御発振器12の発振周波数が入力電圧対発振周波数特性の下限に達した場合は、周波数検出回路9により、セレクタ回路8がフリップフロップ回路4からの信号を選択するようにセレクト信号7を出力する。発振周波数が入力電圧対発振周波数特性の上限に達した場合は、周波数検出回路9により、セレクタ回路8が内部クロック信号6を選択するようにセレクト信号7を切り替え、発振周波数が、入力電圧対発振周波数特性の下限と上限の間となるようにする。

(もっと読む)

1 - 8 / 8

[ Back to top ]