Fターム[5J106QQ01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、機能 (379) | 出力周波数特性に関するもの (86)

Fターム[5J106QQ01]の下位に属するFターム

周波数可変ステップを基準周波数より小に (57)

出力周波数が掃引するもの (3)

非同期時の出力周波数の安定化 (5)

Fターム[5J106QQ01]に分類される特許

1 - 20 / 21

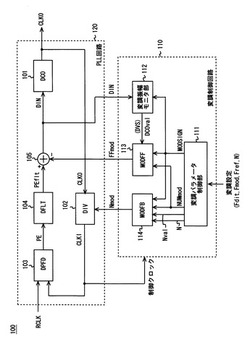

スペクトラム拡散クロック生成回路及びその制御方法

【課題】変調度が安定しない。

【解決手段】周波数変調した出力発振信号を出力するPLL回路を有するスペクトラム拡散信号生成回路であって、前記PLL回路は、入力した発振制御信号の値に応じた周波数で前記出力発振信号を出力する発振回路を備え、前記PLL回路によりフィードバックされたPLL信号の周波数を変調させる前記発振制御信号を生成し、この前記発振制御信号の最大値と最小値をモニタし、そのモニタ結果により前記発振制御信号の最大値と最小値を調整し、前記出力発振信号の変調度を所定の値に制御する周波数変調部を、有するスペクトラム拡散クロック生成回路。

(もっと読む)

デジタル制御型の周波数発生装置

【課題】本発明は、従来の周波数発生装置から共振チップを取り替えずに、その出力のクロック信号を需要の周波数に自由に調整することができる周波数発生装置を提供する。

【解決手段】所定の振動周波数を有する第1クロック信号を発生する発振器モジュールと、操作により、需要の周波数に対応して制御信号を発生するプログラマブル制御モジュールと、前記発振器モジュールからの前記第1クロック信号と前記プログラマブル制御モジュールからの前記制御信号とを受信し、前記両信号に基づいて前記需要の周波数を有する第2クロック信号を発生することができるように前記発振器モジュールと前記プログラマブル制御モジュールとに電気的に連結されている直接デジタル周波数シンセサイザとからなっていることを特徴とするデジタル制御型の周波数発生装置を提供する。

(もっと読む)

PLL回路

【課題】PLL回路の不安定状態や位相雑音特性の劣化を回避する。

【解決手段】

発振周波数が電圧制御発振器からのフィードバック信号と外部から入力される基準信号との位相差に応じて制御されるPLL回路において、前記フィードバック信号を分周する分周器と、前記基準信号を逓倍する逓倍器と、前記分周器からの出力信号と前記逓倍器からの出力信号とをミキシングし周波数変換するミキサと、前記ミキサからの出力信号を分周しデジタル分周信号を出力する第一のデジタル分周器と、前記基準信号を分周しデジタル分周信号を出力する第二のデジタル分周器と、前記第一のデジタル分周器からのデジタル分周信号と、前記第二のデジタル分周器からのデジタル分周信号とを、デジタル位相比較する位相比較器と、を備える。

(もっと読む)

ディジタル制御発振回路、周波数シンセサイザ及び無線通信機器

【課題】ディジタル発振回路自体の位相ノイズを増大させることなく、発振周波数が高く且つ最小周波数変化量が小さい周波数シンセサイザを実現できるようにする。

【解決手段】周波数シンセサイザは、ディジタル制御発振回路11と、発振周波数制御部12とを備えている。ディジタル制御発振回路11は、2本の導体が互いに間隔をおいて並行に配置された並行部15Aと、2本の導体が電気的に絶縁されて交差する交差部15Bとをそれぞれ奇数個有するループ状の伝送線路15と、アクティブ回路17と、第1の可変容量部21及び第2の可変容量部22とを有している。発振周波数制御部12は、第1の可変容量部21に含まれる第1の可変容量素子の高容量状態と低容量状態とを切り替える第1の制御信号をΣΔ変調するΣΔ変調回路40を有している。

(もっと読む)

フェーズロックループにおけるデジタル制御された発振器の出力のディザリング

PLLのデジタル制御された発振器(DCO)は、DCO_OUT信号がディザされた間隔で変化する周波数を持つように、ディザされる。一例では、DCOは、入って来るデジタルチューニングワードのディザされていないストリームを受け取り、ディザされた基準クロック信号REFDを受け取り、DCO_OUT信号を出力し、その周波数変化がディザされた間隔で起こるようになっている。PLLがセルラー電話の送信機の局部発振器で用いられる場合、DCOの新規なディザリングは、デジタルイメージノイズが、メイン局部発振器周波数からの特定の周波数オフセットで、より少なくなるように、デジタルイメージノイズを周波数拡散する。デジタルイメージノイズの周波数拡散によって、PLL基準クロックの周波数を増大する必要なく、ノイズの仕様を満たすことが可能になる。基準クロックの周波数の増大を回避して、ノイズの仕様を満たすことにより、パワーの消費の増大が回避される。  (もっと読む)

(もっと読む)

周波数シンセサイザおよびその制御方法

【課題】周波数シンセサイザがロック状態にあり、かつ、電圧制御発振器の電圧制御信号が一定の電圧範囲からはずれたときに、ロック状態を保ったまま、電圧制御信号を一定の電圧範囲に戻す。

【解決手段】ローパスフィルタ3が生成する制御電圧信号11によって直流バイアス電圧が制御された可変容量ダイオード52の他に補償用可変容量ダイオード53、54を電圧制御発振器5に設け、制御電圧信号11をモニタし、制御電圧信号11の電圧が可変容量ダイオード52の容量を容易に変えられる範囲外の電圧となったときに制御信号16、17のレベルを変化させるモニタ回路8と、その制御信号16、17のレベルの変化をロック状態が解除されないゆっくりとした電圧変化に鈍らせて補償用可変容量ダイオードに直流バイアス電圧を与える時定数回路72とを備える。

(もっと読む)

シンセサイザと、これを用いた受信装置、及び電子機器

【課題】温度に対する周波数の変化率が大きい振動子を用いた場合でも、安定した温度制御が可能なシンセサイザを提供すること。

【解決手段】本発明のシンセサイザと、これを用いた受信装置、及び電子機器は、MEMS振動子を有する基準発振器から出力された基準発振信号を基に第1局部発振信号を生成する第1シンセサイザ部と、第1シンセサイザ部から出力された第1局部発振信号に基づいて、温度変化によるMEMS振動子の周波数変動を検出する周波数変動検出器と、周波数変動検出器の検出結果に基づいて、第1局部発振信号の周波数調整を行う第1周波数調整部とを備える。この構成により、より精密な温度検出が可能となり、シンセサイザの温度補正を高精度に行うことが可能となり、MEMS振動子を用いたより小型のシンセサイザを実現できる。また、このシンセサイザを用いることで小型の受信機、電子機器を実現できる。

(もっと読む)

ローカル信号生成回路

【課題】従来のローカル信号生成回路は、回路面積と消費電力が大きくなる問題があった。

【解決手段】本発明にかかるローカル信号生成回路は、基準信号と帰還信号の位相差を検出し、誤差信号を出力する位相比較器21aと、誤差信号を受け昇圧電圧を生成するチャージポンプ回路22aと、昇圧電圧を整形してチューニング電圧Vtuを生成するループフィルタ23aと、チューニング電圧Vtuに基づき所定の周波数を有する第1の出力信号(I_high、Q_high)を生成する電圧制御発振器24aと、第1の出力信号(I_high、Q_high)を所定の周波数に分周した第2の出力信号(I_low、Q_low)として出力すると共に、第1の出力信号(I_high、Q_high)を前記所定の周波数に分周した分周信号を帰還信号を生成する分周器26aに出力するプリスケーラ25aと、を有するものである。

(もっと読む)

分周回路及びシンセサイザ

【課題】本発明は、分周回路に関し、小数分周の設定の自由度を向上することを目的とする。

【解決手段】クロック入力端子と、クロック入力端子からのクロックが入力される第1及び第2のフリップフロップ回路と、一対のプログラム入力端子と、第1及び第2のフリップフロップ回路の間に接続され一対のプログラム入力端子からの信号が入力される組み合わせ回路と、第2のフリップフロップ回路の出力を出力するクロック出力端子とを備え、第1のフリップフロップ回路の出力は組み合わせ回路を介して第2のフリップフロップ回路に入力され、第2のフリップフロップ回路の反転出力は第1のフリップフロップ回路に入力されるように構成する。

(もっと読む)

局部発振器および無線通信装置

【課題】 ループ帯域内のノイズ増大を招くことなく、ヘテロダイン方式におけるローカル周波数の変調精度を向上することを目的とする。

【解決手段】

本発明の局部発振器は、基準発振器214で生成された基準信号から複数の参照周波数に対応した複数の参照信号を生成する第1PLL312と、第1PLL312からの複数の参照信号から複数のローカル周波数に対応した複数のローカル信号を生成する第2PLL314と、を備えることを特徴としている。

(もっと読む)

拡散スペクトラムクロック生成装置

【課題】回路規模を大きくせずにEMIを十分に低減できる拡散スペクトラムクロック生成装置を提供する。

【解決手段】拡散スペクトラムクロック生成装置は、クロック信号を生成するPLL(Phase Locked Loop)回路1と、クロック信号の周波数変調を行う周波数変調回路2とを備え、周波数変調回路2は、カウンタ11と、設定レジスタ12,13と、マルチプレクサ14と、1/P分周器15と、ラッチレジスタ16と、アップダウンカウンタ17と、設定レジスタ18と、加算器19とを有する。Hershey-kiss変調プロファイルの1周期分を8等分した各相対時刻ごとの変調ポイントを直線でつないだ変調プロファイルを用いて、1/N分周器8の分周比を1周期に8回変化させるため、Hershey-kiss変調プロファイル用の特性テーブルを設けなくても、Hershey-kiss変調プロファイルと同様の周波数変調を行える。

(もっと読む)

集積回路装置

【課題】VCOを備える周波数シンセサイザに関し、VCOのf−V特性のばらつきに対処する手法を提案する。

【解決手段】制御電圧V1に応じて発振周波数f1が変化する第1の電圧制御発振器を備え、基準周波数に応じた周波数の信号を発振する第1の周波数シンセサイザと、制御電圧V2に応じて発振周波数f2が変化する第2の電圧制御発振器を備え、前記第1の周波数シンセサイザと同じチップ上に設けられており、前記基準周波数に応じた周波数の信号を発振する第2の周波数シンセサイザと、前記第1の電圧制御発振器の制御電圧V1をモニタし、前記第1の周波数シンセサイザの周波数がロックしているときにモニタされた前記制御電圧V1と基準電圧とを比較し、前記制御電圧V1と前記基準電圧との比較結果に基づいて、前記第2の電圧制御発振器のf2−V2(発振周波数−制御電圧)特性を変化させるコンパレータとを備えることを特徴とする集積回路装置。

(もっと読む)

フラクショナルNPLLシンセサイザ、フラクショナルNPLLシンセサイザの発振周波数帯域制限方法

【課題】不要な発振周波数帯域制限をかける事が無く、必要な回路を減らして、小サイズ低コストで実現できるフラクショナルNPLLシンセサイザ、フラクショナルNPLLシンセサイザの発振周波数帯域制限方法を提供する。

【解決手段】可変分周器4と、分周比制御回路5と、位相比較器1と、低域通過フィルタ2と、電圧制御発振器3とによって発振周波数を生成するフラクショナルNPLLシンセサイザにおいて、分周比制御回路5は、周波数偏移をかける対象であるビット列信号を全ビットに亘って蓄積記憶し、蓄積記憶したビット列信号の全ビットに亘って極性の切り換わりを判別して、極性が切り換わっているときのみ分周比を段階毎に変化させて発振周波数の偏移を段階毎に行う。

(もっと読む)

AM/FM受信機用PLLシンセサイザ回路とその切り替え方法

【課題】AM受信時とFM受信時の交差周波数を制御することでS/N特性を向上させるPLLシンセサイザ回路を提供する。

【解決手段】基準信号とPLLシンセサイザ回路の出力信号を分周した分周信号との間の位相差に応じた位相差信号を生成する位相比較回路と、位相差信号に基づいて電流制御をするとともに、AMで使用する場合とFMで使用する場合で電流制御を切替えてチャージポンプ信号を生成するチャージポンプ回路と、AMで使用する場合とFMで使用する場合で、チャージポンプ回路の電流制御を切り替えるためのレジスタ回路と、チャージポンプ信号を入力し平滑化して制御電圧として制御電圧信号に応じた周波数で発振して局部発振信号を出力するVCO回路と、局部発振信号を分周して分周信号として出力する分周回路と、を具備するAM/FM受信機用PLLシンセサイザ回路である。

(もっと読む)

位相同期ループ回路、半導体集積回路、および、受信装置

【課題】使用する電圧制御発振器の選択、および、その発振周波数範囲の設定をより効率的に行うことができる位相同期ループ回路を実現する。

【解決手段】位相同期ループ回路100の制御部103は、位相同期ループ回路100に接続する電圧制御発振器として、複数の電圧制御発振器VCO1〜VCOnのうちから、選局周波数を含む主発振周波数範囲をもつ電圧制御発振器を選択し、その後、選択された電圧制御発振器の発振周波数範囲を、選局周波数を含む副発振周波数範囲に設定する。

(もっと読む)

周波数シンセサイザ

【課題】新規な原理により、広帯域に亘って細かく周波数を設定でき、周波数の引き込み範囲が広い周波数シンセサイザを提供すること。

【解決手段】電圧制御発振部の出力周波数の正弦波信号を直交検波し、検波に用いた周波数信号の周波数との差分の周波数(速度)で回転するベクトルを作成し、電圧制御発振部の出力周波数が設定値になったときのベクトルの周波数を予め計算しておいて、電圧制御発振部を駆動したときにベクトルの周波数と前記計算された周波数との差分に相当する電圧信号を電圧制御発振部にフィードバックして、その差分がゼロになるようにPLLを形成する。従ってPLLがロックされたときに電圧制御発振部の出力周波数が設定周波数に調整される。またPLLのロック後に両者の開きが大きくなった後は設定値を積分回路部により積分して制御電圧に加える。

(もっと読む)

PLL回路及びチャージポンプ回路の駆動方法

【課題】PLL回路のロック時のループフィルタの出力電圧の変動を抑えることである。

【解決手段】基準クロック信号と帰還クロック信号の位相が一致したとき、基準クロック信号と帰還クロック信号の立ち下がりのタイミングで、オン時間の短いUP信号とDOWN信号をチャージポンプ回路の2個のMOSトランジスタに供給する。これにより、チャージポンプ回路の貫通電流を少なくできるので、貫通電流によるループフィルタの出力電圧の変動を抑えることができる。

(もっと読む)

プリスケーラ及びバッファ

【課題】広帯域化を図ることができるプリスケーラを提供すること。

【解決手段】プリスケーラ33は、バッファ部41とカウンタ43とを備える。バッファ部41は、駆動能力が異なる複数のインバータ回路52a〜52cからなる初段回路52と、直列接続された複数のインバータ回路54a〜54dと、帰還回路55とを備える。初段回路52の各インバータ回路52a〜52cは、第1スイッチ部51と第2スイッチ部53とにより、何れか1つに信号fvが入力され、出力端子が後段のインバータ回路54aに接続され、初段回路52における駆動能力が可変される。帰還回路55は、電圧V1,V2により設定される抵抗として機能する。

(もっと読む)

周波数シンセサイザ、通信機、及び周波数シンセサイズ方法

【課題】高精度のクロックを高速に切り換えることの出来る周波数シンセサイザ、通信機、及び周波数シンセサイズ方法を提供する。

【解決手段】高精度に生成された基準クロックを元に、デジタル的な演算とD/Aコンバータ、ローパスフィルタを用いて所望の周波数の正弦波信号を発生させ、その正弦波信号を元の基準クロックとミキシングし、適切なフィルタを通す事で所望の周波数の正弦波を生成する事ができる。また、ミキシング後のバンドパスフィルタの中心周波数や、上記正弦波信号を発生させる演算処理、あるいは出力部のセレクタを変化させる事で、基準クロックの周波数を変更する事無く周波数切り換えを行うので、高速な周波数切り換えを実現する事ができる。周波数生成に用いる正弦波信号はデジタル的な演算によって生成されるので、周波数制御を精度良く行う事ができる。

(もっと読む)

周波数差補償器

【課題】 二つの電圧制御型発振器のそれぞれの発振波形を位相は同期せずに周波数のみを等しくするような周波数差補償器を提供する。

【解決手段】 入力制御端子から得る制御電圧Vcntに応じた周波数fで発振する発振器01と、発振周波数fに依存した直流電圧値Vfを出力する周波数変換器02と、一定周波数frで発振する発振器03と、周波数frに依存した直流電圧値Vfrを出力する周波数変換器04と、周波数変換器02及び周波数変換器04の各出力値の差分に基づき出力値Vcmpを出力する比較器05と、出力値Vcmpに基づいて発振周波数Vfが発振周波数Vfrと等しくなるように入力制御端子へ制御電圧Vcntを出力する制御器06から構成される周波数差補償器とした。

(もっと読む)

1 - 20 / 21

[ Back to top ]