Fターム[5J106SS01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 細部の構成 (94) | 比較器の具体的回路が示されたもの (6)

Fターム[5J106SS01]に分類される特許

1 - 6 / 6

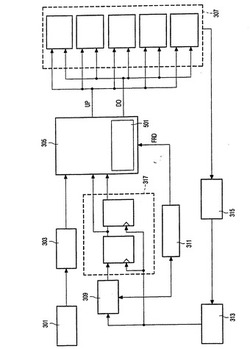

分数分割電荷補償手段を有する周波数シンセサイザ

【課題】分数−N補償法で用いられる電荷ポンプを容易に整合し、分数分割によって導入された望ましくない周波数成分を濾波する。

【解決手段】VCO周波数分割器309と基準周波数信号303との間の位相不整合の分数−NPLLにおける補償が可変電荷ポンプ装置307により行われる。移相比較器305は、電荷ポンプ装置の電荷ポンプのいくつかを早くオンにし、残りの電荷ポンプを遅れてオンにするために補償論理501を有する。このプロセスは、部分電荷を適切に補償するために正確な時点で等価電荷をオンにする。

(もっと読む)

位相検出回路

【課題】位相ロックループ周波数シンセサイザ設計における、大きな電圧制御発振器範囲(例えば、487MHz)、(例えば)1.2V電力供給電圧、および低い電力消費の要求を達成する。

【解決手段】位相検出回路は、参照信号を受信するように構成された参照入力と、フィードバック経路においてディバイダ回路からの分周信号を受信するように構成されたフィードバック入力と、参照信号と分周信号の間の周波数及び位相関係に従って位相ロックループ内のチャージポンプを制御するための制御パルスを生成するように構成されたパルス生成回路と、を有し、分周信号は、分周信号の周期の半分よりも短い長さを具備するパルスを有し、且つ、パルス生成回路は、分周信号のエッジ及び参照信号のエッジから制御パルスのエッジを定義するように、分周信号のパルスをマスクとして使用して参照信号をマスキングすることにより、制御パルスを生成するように構成されている。

(もっと読む)

周波数シンセサイザ

【課題】 低いジッター成分を持つ周波数シンセサイザと電力消耗が最小化された周波数シンセサイザを提供することを課題とする。

【解決手段】基準信号と比較信号が入力されて周波数と位相の差を検出し、これによって、アップ信号、又はダウン信号を発生させる位相比較器と、前記アップ信号又はダウン信号によって、電圧を充電又は放電して制御信号を出力する電荷ポンピング回路と、前記ポンピング回路より出力される制御信号によって、周波数を持つ信号を発振出力信号と出力する電圧制御発振器と、前記電圧制御発振器と連結されて、デューティサイクルを補正するデューティサイクル補正回路と、及び前記発振出力信号の周波数を分割して、前記位相比較器に前記比較信号を提供するフィードバッグディバイダーが含まれる。

(もっと読む)

位相同期ループ形周波数シンセサイザ

【課題】位相比較器のフリップフロップ間の誤差に起因するスプリアスを抑圧することができる位相同期ループ形周波数シンセサイザを得ることを目的とする。

【解決手段】位相比較器33から出力された位相比較信号Dnu(t)を第1の利得値αnuで電圧増幅するとともに、その位相比較器33から出力された位相比較信号Dnd(t)を第1の利得値αnuと異なる第2の利得値αndで電圧増幅し、電圧増幅後の位相比較信号Dnu(t)と電圧増幅後の第2の位相比較信号Dnd(t)との差分信号を出力する減算回路33を設ける。

(もっと読む)

PLL回路及びチャージポンプ回路の駆動方法

【課題】PLL回路のロック時のループフィルタの出力電圧の変動を抑えることである。

【解決手段】基準クロック信号と帰還クロック信号の位相が一致したとき、基準クロック信号と帰還クロック信号の立ち下がりのタイミングで、オン時間の短いUP信号とDOWN信号をチャージポンプ回路の2個のMOSトランジスタに供給する。これにより、チャージポンプ回路の貫通電流を少なくできるので、貫通電流によるループフィルタの出力電圧の変動を抑えることができる。

(もっと読む)

フラクショナル・スプリアスの低減方法、フラクショナル・スプリアスの発生を低減したフラクショナルN−PLL発振器

【課題】フラクショナルN−PLLにおけるフラクショナル・スプリアスの低減

【解決手段】非線形素子を有する位相比較器と位相比較器の出力信号の低周波成分に応答する可変周波数発振器とを備え、位相比較器には可変周波数発振器の出力信号を分周した信号と基準信号とが入力されるフラクショナルN−PLL発振器において、フラクショナル・スプリアスを低減する方法であって、前記位相比較器に入力される前記信号から、前記可変周波数発振器の発振周波数成分を除去し、それによりフラクショナル・スプリアスを低減する。図においては、ゲートを用いて、可変周波数発振器の発振周波数成分を除去する。

【選択図】図4

(もっと読む)

(もっと読む)

1 - 6 / 6

[ Back to top ]