Fターム[5J500DP02]の内容

Fターム[5J500DP02]に分類される特許

381 - 395 / 395

増幅器

【課題】 入出力信号が共にシングルエンド信号であっても、電源電圧よりも大きな最大出力電圧を出力することができる増幅器を実現することを目的にする。

【解決手段】 本発明は、入力電圧を増幅する増幅器に改良を加えたものである。本増幅器は、出力端子から出力される出力電圧を分圧して反転入力端子に帰還し、非反転入力端子に入力される前記入力電圧を安定したゲインで増幅する第1の演算増幅器と、この第1の演算増幅器に入力される正電源と負電源との電位を分圧し、分圧電位を出力する分圧回路と、正電源入力端子、負電源入力端子のそれぞれが前記第1の演算増幅器の正電源入力端子、負電源入力端子に接続され、出力端子が基準電位に接続され、非反転入力端子に分圧回路の分圧電位が入力され、反転入力端子が前記第1の演算増幅器の非反転入力端子に接続された第2の演算増幅器とを設けたことを特徴とするものである。

(もっと読む)

LCフィルタ付Dクラス増幅器

【課題】 Dクラス増幅器において静電保護用ダイオードをLCフィルタからの逆起電力によるターンオン動作から防止する。

【解決手段】 内部回路5とLCフィルタ3の間にショットキーバリアダイオード2を並列に接続する。ショットキーバリアダイオード2は静電保護用ダイオード8に比べて、飽和電圧が低く、回復時間も短い為、ショットキーバリアダイオード2からの逆起電力による静電保護用ダイオード8のターンオン動作をさせない電圧でクリップする。その結果、静電保護用ダイオード8はターンオンせず、静電保護用ダイオード(pn接合ダイオード)のチャージ時間の抜き去り時間というペナルティを免れる。ひいては、スピーカ4の音質向上に効果的である。

(もっと読む)

増幅器及び差動型分布増幅器

【課題】マッハツェンダ型LN光変調器を駆動するための増幅器等として使用される増幅器に関し、高利得特性を持ち、かつ、出力段の差動型分布増幅器の入力側動作バイアスポイントを容易に調整できるようにする。

【解決手段】ソースフォロア回路部68には電流源を設けず、ソースフォロアトランジスタ11、14のソースを本発明の差動型増幅器の第1実施形態69の入力端子18、19に接続する。差動型増幅器69の入力側伝送線路20、21の終端抵抗22、23の接続点25にソースフォロア回路部68に必要な電流源70を接続する。

(もっと読む)

CMLバッファ用のコモンモード・シフティング回路

【課題】CMLデバイスのコモンモード出力電圧を任意の電圧にシフトするためのコモンモード・シフティング回路を開示する。

【解決手段】定電流源がCMLデバイスの各出力に設けられる。定電流はそれぞれコモンモード出力電圧を上昇させるまたは低下させる傾向がある正または負の電流とすることができる。定電流源は、好ましくはCMLデバイス用の電源よりも高い電圧を有する交番電圧源に接続される。本発明はさらに、2つまたはそれ以上の出力ポートを有する電流モード論理回路の出力信号を調節する方法であって、電流モード論理回路の各出力ポートにおいて定電流を与えるステップを備え、それによって前記電流モード論理回路の各出力ポートにおけるコモンモード電圧がレベル・シフトされる方法を提供する。

(もっと読む)

ショック音抑制回路

【課題】BTL方式の音声出力装置において、スピーカ出力オン時のショック音の発生を抑制する。

【解決手段】基準電圧発生部5、第1のオペアンプ3及び第2のオペアンプ4の起動時からコンデンサC2の充電完了時までの間は、スイッチ11をオンすることにより、第1のオペアンプ3と第2のオペアンプ4の出力端子間、すなわち、両スピーカ入力端子6,7間に差電圧が生じなくなる。従って、スピーカ出力のオン時にショック音が発生しない。

(もっと読む)

パワーアンプ装置およびDC成分除去方法

【課題】いわゆるD級アンプと呼ばれるパワーアンプ装置であって、カップリングコンデンサを用いることなく、DCディザによるDC成分を除去することが可能なパワーアンプ装置を提供する。

【解決手段】パワースイッチング部4と、スイッチング信号生成部とを備えたいわゆるD級アンプ装置において、パワースイッチング部4にキャンセル信号生成手段としての機能を持たせ、スイッチング信号生成手段において形成されたハイサイドとローサイドの1対のドライブパルスOUT1+、OUT1−に対して、DCディザにより入力信号に生じているDC成分をキャンセルするためのキャンセル成分を含ませるようにする。

(もっと読む)

デュアルブリッジトランスデューサ用差動増幅器

複数のブリッジトランスデューサが、デュアル構成で提供される。各トランスデューサの一方の出力端子が、増幅器の差動入力に結合される。これらのトランスデューサの各他方の出力がそれぞれ一緒に結合され、デュアル能動負荷用のバイアスを制御するために使用される。トランスデューサは、バイポーラ技術と共に、ブリッジとしてホール効果、磁気抵抗またはピエゾ抵抗感知素子を使用して、モノリシックシリコン集積回路内で実施することができる。単一のホール効果トランスデューサを、差動増幅器の入力に結合することができ、センタータップ端子を使用して、デュアル能動負荷用のバイアスを制御することができる。  (もっと読む)

(もっと読む)

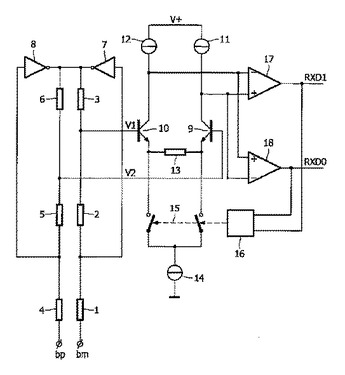

差動増幅器を用いた差動信号受信装置

本発明は、差動型データバス用受信器であって、2つの抵抗分岐(1、2、3:4、5、6)と、2つのトランジスタ(9、10)を有する差動増幅器と、抵抗器(13)と、さらに電流源(14)からの電流を、2つのトランジスタ(9、10)を結合する抵抗器(13)のいずれかの側に切り替え可能なスイッチ(15)を制御する制御ロジック(16)と、さらに反対極性を有する差動増幅器の2つのトランジスタ(9、10)に結合された2つの演算増幅器(17、18)とを有し、受信器において、制御ロジックが、2つの演算増幅器の出力信号から、「0」または「1」のどちらがバス上に予測されるかを検出するとともに、その受信器がそれに従って、受信されたバス信号との比較が行われるように、スイッチ(25)を設定する、受信器に関する。  (もっと読む)

(もっと読む)

アクチュエータ駆動回路

【課題】出力部の飽和状態から非飽和状態への変化応答時間を改善する。

【解決手段】第2の増幅部11の利得を大きくとることにより、第3,第4出力端子11a,11bの出力が飽和しても第1,第2出力端子10a,10bからの出力は飽和せず、入力の変動に合わせた帰還電流を入力側に帰還でき、飽和しても仮想短絡が持続し、反転入力端子2の電位が非反転入力端子3に対して乖離しない。このため第3,第4出力端子11a,11bの出力を飽和状態にして、入力部1の電位をステップ入力して飽和した出力を入力範囲内に戻したとき、第3,第4出力端子11a,11bの出力の過渡応答時間を短縮できる。

(もっと読む)

無線通信システムおよび半導体集積回路

【課題】 送信出力電力に対する検出出力の直線性が良好で、しかも温度依存性を持たない検出出力を得ることができる送信電力検波回路およびそれを用いた無線通信システムを提供する。

【解決手段】 複数のアンプ(AMP1〜AMP4)をシリーズに接続してなり各段のアンプの入力トランジスタ(Q1,Q2)のエミッタから整流出力を取り出して合成することで検波出力を得る整流検波部(111)と、該整流検波部を構成する上記アンプと類似の構成を有するダミーアンプ及び該ダミーアンプの出力を所定の比率で変化させる係数回路からなる温度特性補償用の電圧を発生する補償電圧生成回路(112)と、前記整流検波部の出力電圧から前記補償電圧生成回路で生成された補償電圧を減算することで温度依存性のない検波出力を得る加減算回路(112)と、により送信出力電力の検波回路を構成するようにした。

(もっと読む)

高忠実度で高出力の切り替え式増幅器

【課題】大きな出力を提供しかつ高い忠実度を与える出力段アーキテクチャを提供する。

【解決手段】傾斜増幅器出力段(10)を備えた傾斜増幅器機構について記載している。本デバイスは、MRIシステム内にあるような傾斜コイル(18)に対して電流を提供するために使用することができる。開示した回路は、第1の電圧で動作している第1のブリッジ増幅器(12)と、第2の電圧で動作している第2のブリッジ増幅器(14)と、第3の電圧で動作している第3のブリッジ増幅器(16)と、傾斜増幅器制御段(30)との直列結合を含んでいる。これらの増幅器は異なるレベルの出力電圧を提供することができると共に、あるレンジの出力電圧及び電流レベルを提供するために異なる時刻及び周波数で切り換えることができる。

(もっと読む)

負荷インピーダンスの較正手段を備えた平衡形ミクサ

較正装置(CC)が、第1の負荷インピーダンス手段(Z1)及び第2の負荷インピーダンス手段(Z2)をそれぞれ備えた第1の出力及び第2の出力を有する平衡形回路装置(MC)に結合されている。この較正装置(CC)は、線形化のために前記第1の負荷インピーダンス手段(Z1)及び前記第2の負荷インピーダンス手段(Z2)を負荷の不平衡状態に調整するよう構成された調整手段(ADM)と、前記負荷インピーダンス調整手段(ADM)と前記第1及び前記第2の出力との間に挿入されていて、前記負荷インピーダンス調整手段(ADM)を前記第1及び前記第2の出力のうち選択された一方にのみ選択的に結合して前記負荷インピーダンス調整手段(ADM)を前記第1の負荷インピーダンス手段(Z1)か前記第2の負荷インピーダンス手段(Z2)か、どちらか一方に並列接続するように構成された結合手段(CM)とを有する。  (もっと読む)

(もっと読む)

低スキューの対称差動出力信号を有するレールツーレール同相モード動作を有する高速差動レシーバ

レールツーレール同相モード電圧を有する小さな差動電圧を受けて増幅するための新たな方法および装置を提供する、新規な高速差動レシーバ(100)が開示される。レシーバの出力信号は、低いスキューと高い対称性を有する差動信号である。この高速差動レシーバ(100)は、結果として生じる信号が再結合され、標準化され、増幅される前の、差動位相分割方法論に基づく同相モード電圧の標準化に基づいている。方法は、差動信号分割ステージ(110)、これに続く同相モード電圧標準化ステージ(130)、そして制御された利得のトランスインピーダンスステージ(150)の使用と、次いで、対称であり性質的にバランスの取れた1つまたは2つのレールツーレール増幅ステージ(170)を用いた増幅と、を含む。  (もっと読む)

(もっと読む)

差動回路用複合負荷

改良負荷構成は電力消費を増加することなく回路帯域幅を増加する差動回路用に提供される。差動回路は一般に、相互に結合されたエミッタを有するトランジスタ(Q1,Q2)の差動対を含む。改良負荷構成は各トランジスタ(Q1,Q2)のコレクタに結合された負荷抵抗(R1,R2)および各々の負荷抵抗器(R1,R2)が結合されたインダクタから構成され、インダクタ(XF)は相互インダクタンスによって相互に結合されている。  (もっと読む)

(もっと読む)

高性能低雑音増幅器

二つの入力端子上において逆位相で一対の入力信号Sp及びSnを受信し、四つの出力端子上において逆位相で二対の出力電流SIp及びSInをもたらすための信号処理回路が提供されている。各々の入力信号Sp及びSnは増幅ユニットLNAUp及びLNAUnで増幅され、その後、分割ユニットSPLUp及びSPLUnで分割される。本発明は、二つの分割ユニットSPLUp及びSPLUnの各々が、前記増幅ユニット、すなわちそれぞれLNAUp及びLNAUnと前記出力端子の一つとの間に接続される少なくとも二つの分岐部、すなわちそれぞれBIp及びBQp並びにBIn及びBQnを含むように構成され、四つの分岐部BIp及びBQp並びにBIn及びBQnは各々、少なくとも一つのインピダンス部、すなわちそれぞれ同じ特性を有するRIp、RQp、RIn、及びRQnを含む。ミキサ回路は当該信号処理回路で容易にスタックされ得る。  (もっと読む)

(もっと読む)

381 - 395 / 395

[ Back to top ]