Fターム[5K029EE08]の内容

直流方式デジタル伝送 (8,390) | 通信方式 (506) | ビット同期伝送 (163) | 同期信号を伝送するもの (102) | 受信側から同期信号を送るもの (8)

Fターム[5K029EE08]に分類される特許

1 - 8 / 8

半導体デバイス、画像処理装置

【課題】複数のデータ伝送路のタイミングを低コストで同期可能な半導体デバイスを提供すること。

【解決手段】送信側から受信側にデータをシリアル送信する半導体デバイス100であって、データ転送の合間に、同期判定用のコードを送信する同期判定コード送信手段301,302と、送信側と受信側に共通のクロック信号を提供するクロック信号提供手段103と、クロック信号に同期して同じデータを送信する複数の伝送路117と、受信側に提供されたクロック信号の位相を、それぞれ異なる所定量遅延させ複数の遅延クロック信号を生成するクロック生成手段110と、遅延クロック信号に同期して伝送路を介して送信されたデータを取り込む複数の受信バッファ111と、コードを予め定められた規則に基づき検証して複数の受信バッファから1つの受信バッファを、複数の遅延クロック信号から1つの遅延クロック信号をそれぞれ選択する選択手段113、115と、を有する。

(もっと読む)

通信装置及びクロック制御方法

【課題】データ送信部に送信データが保留されている間の消費電力を低減することができる通信装置及びクロック制御方法を提供すること

【解決手段】本発明にかかる通信装置は、供給されたクロックにより駆動し、対向装置に対してデータの送信を行う送信処理部34と、送信処理部34に対してクロックを供給する送信クロック制御部20と、対向装置に対するデータ送信の停止を指示するポーズフレームを受信する受信処理部31と、を備え、受信処理部31がポーズフレームを受信した場合、送信処理部34は、対向装置に対するデータ送信を停止し、送信クロック制御部20は、ポーズフレームにおいて指定される送信停止期間中の送信処理部34に対するクロック供給を停止するものである。

(もっと読む)

シリアル通信システム及びシリアル通信方法

【課題】MDライン及びSDラインの両方を同時にデータ送信に使用することができるシリアル通信システムを提供する。

【解決手段】本発明のシリアル通信システム1は、第1のデバイス2と第2のデバイス3とを有し、第1のデバイス2と第2のデバイス3とは、第2のデバイス3が生成したシリアルクロックに基づいて、相互通信を開始するシリアル通信システムである。第1のデバイス2から第2のデバイス3への出力が、前フェーズにおいて受信したデータの最終ビット値と反転していると、第2のデバイス3は第1のデバイス2の通信準備状態が完了状態であると判断し、相互通信を開始する。

(もっと読む)

通信速度制御方法、通信速度制御システムおよび画像形成装置

【課題】最適な通信速度が不明な通信装置間で最適な通信速度を短時間に設定できる、通信速度制御方法、通信速度制御システムおよび画像形成装置を提供する。

【解決手段】調歩同期式通信を行う主局側装置と従局側装置との間の通信速度を制御する通信速度制御方法であって、主局側装置と従局側装置とを、主局側装置と従局側装置が常に通信可能な所定の初期通信速度に設定して、主局側装置と従局側装置との間で通信を開始し、従局側装置から主局側装置に、従局側装置のクロック周波数関連データ501を送信し、主局側装置は受信した従局側装置のクロック周波数関連データを参照して主局側装置と従局側装置との間の、初期通信速度より高速の所要の通信速度を決定し、主局側装置は従局側装置に、所要の通信速度、または従局側装置を所要の通信速度に設定するための分周比のデータ502を送信し、以後、主局側装置と従局側装置とを所要の通信速度に設定して、主局側装置と従局側装置との間の通信を継続する通信速度制御方法。

(もっと読む)

シリアル通信装置

【課題】マスター回路とスレーブ回路間で行なわれるシリアル通信において、設定操作なしで、高速通信ができ、低価格化で大電力を供給可能な1線式のシリアル通信装置を提供する。

【解決手段】外部からのパラレル入力信号をシリアル信号に変換して送信するスレーブ回路2と、該スレーブ回路2から受信したシリアル受信データをパラレル信号に変換して外部出力するマスター回路1を備えた。

(もっと読む)

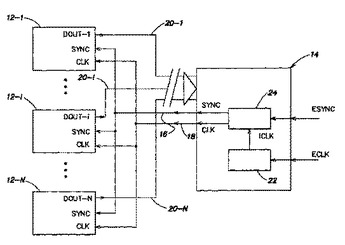

シリアルディジタルデータ通信インターフェイス

伝播遅延が数クロックサイクル長までおよび、ゆっくりと変動する可能性のある、データ送信機12からデータ受信機14へのデータ伝送のシリアルプロトコルおよびインターフェイス。データ受信機は、データ送信機にクロックを供給する。受信機または送信機のいずれかによって供給される同期信号は、クロックによって制御される転送レートで、データ伝送のフレームを始動させる。同期信号は、フレーム長として知られている、データヘッダーとそれに続く所定の数のデータビットの送信を調整する。データ受信機は、ヘッダービットを使用して、後続のデータビットをサンプリングする時間を決定する。フレームの長さは、ビット誤りを発生させるほど大きく伝播遅延ライン特性が変化しないことの十分な見込みを得るように限定される。システムは、各フレームの始点において、再同期する。  (もっと読む)

(もっと読む)

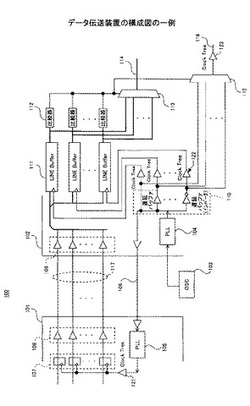

データ伝送装置及びデータ伝送方法

信号受信部(11)は、ツイストペアケーブル(31)を通じてアナログ信号を受信する。A/D変換部(12)は、アナログ信号をデジタル信号に変換する。位相検出部(14)は、デジタル信号の位相を検出して、受信タイミング信号を生成する。送信タイミング生成部(15)は、受信タイミング信号に基づいて、受信信号(A点)と送信信号(D点)とが所定の位相差となるように、送信処理部(16)がデジタル信号を出力するタイミングを制御する。送信処理部(16)は、このタイミングに従って、接続機器(20)から入力するデータにマッピングを施したデジタル信号を出力する。D/A変換部(17)は、デジタル信号をアナログ信号に変換する。信号送信部(18)は、アナログ信号をツイストペアケーブル(32)を通じて送信する。  (もっと読む)

(もっと読む)

データ通信回路

【課題】周波数またはデューティの相違で検出することにより、双方向のデータ通信を実現する2線式データ通信装置を提供する。

【解決手段】第1の送受信装置と第2の送受信装置を有した2線式データ通信であって、第1の送受信装置は第1の送信信号に応じたクロックのデューティを設定しこれに基づき発生するパルスとその反転関係にあるパルスを第2の送受信装置に送信し、また第2の送受信装置からの受信信号として、電流を検出する電流検出手段を備える。一方、第2の送受信装置は、送信されてきた信号を積分し基準電圧と比較を行う比較手段と、送信クロックに同期してデータを取り込む第1の送受信装置からのデータ受信手段と、第1の送受信装置に向け2線間のインピーダンスを第2の送信信号に応じて変化させる第2の制御手段とを備え、クロックのデューティを変えることによって、データを送信することを特徴とするデータ通信回路。

(もっと読む)

1 - 8 / 8

[ Back to top ]