Fターム[5K046EE21]の内容

有線伝送方式及び無線の等化、エコーの低減 (13,292) | 等化一般 (2,382) | 等化器構成 (876) | 回路要素 (47)

Fターム[5K046EE21]の下位に属するFターム

Fターム[5K046EE21]に分類される特許

1 - 13 / 13

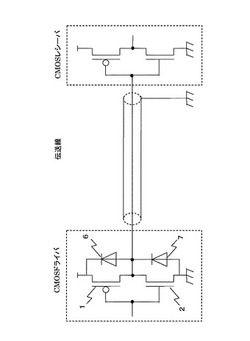

電気信号の伝送回路、IC、プリント配線板、機器およびシステム

【課題】CMOS伝送回路において、レシーバの動作を不安定にしたり不要輻射を放出したりするリンギングの発生を抑制した電気信号の伝送回路を提供する。

【解決手段】本発明の一態様は、CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、CMOSドライバのPMOS FET1と並列にアノード電極がドライバ出力端子につながれるように第1のダイオード6を接続し、CMOSドライバのNMOS FET2と並列にカソード電極がドライバ出力端子につながれるように第2のダイオード7を接続し、PMOS FET1のデバイストランスコンダクタンスと第1のダイオード6の(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにし、NMOS FET2のデバイストランスコンダクタンスと第2のダイオード7の(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにしたことを特徴とする電気信号の伝送回路である。

(もっと読む)

通信装置

【課題】送信・受信時に共用する電磁波対策を最適に運用し、且つ安価に構成することができる通信装置を提供する。

【解決手段】送信と受信とが切り替わるポートを持ったLAN用の通信装置において、矩形パルスを送受信するための送受信手段と、外部の対抗機と接続するための接続手段と、送受信手段のポートと接続手段との間に設けられ、送受信手段の送受信の切替に連動して矩形パルスをなまらせるための抵抗を通る経路もしくは抵抗を通らない経路を選択する選択手段と、を備えた。

(もっと読む)

高周波ESD保護回路

【課題】高周波領域においても悪影響を与えることなく動作可能な高周波ESD保護回路を提供する。

【解決手段】伝送線路11及び12は、差動信号を入力する入力端子1及び2との間に直列接続されており、いずれも入力信号の波長の1/4の線路長を有している。ESD保護素子13は伝送線路11と12との間の接続ノードAに一端を接続され、他端は接地端子GNDに接続されている。接続ノードAは、入力端子1及び2からの差動入力信号に対しては、実質的に接地端子とみなすことができる。このため、接続ノードAと実際の接地端子GNDの間に接続されたESD保護素子13のインピーダンスはほぼ零となる。

(もっと読む)

電気分散補償等化回路

【課題】群遅延時間の周波数依存性を抑制し、出力波形の歪みが少ない電気分散補償等化回路を提供する。

【解決手段】例えば2個縦列接続し、入力データのレベル調整用の入力バッファIBUF−LPFからのデータを所定遅延時間ずつ順次遅延させる遅延回路D1,D2、入力バッファIBUF−LPFおよび遅延回路D1,D2からのデータとタップ端子TAP1〜TAP3からのタップ電圧信号とをそれぞれ乗算する乗算器M1〜M3、乗算器M1〜M3からのデータを順次加算して積算する2入力の加算器A1,A2、最終段の加算器A2からのデータを外部に出力する出力バッファOBUFを備え、入力バッファIBUF−LPFの内部構成として、差動増幅回路と出力部の第2のエミッタフォロアとの間を、あらかじめ定めた周波数閾値以下の低周波成分を通過させ、該周波数閾値を超える高周波成分を低減させるローパスフィルタLPFを介して接続する構成とする。

(もっと読む)

信号波形等化回路及び受信回路

【課題】中心電圧が0Vの入力信号の波形等化が可能であり、且つ、回路規模の小さい信号波形等化回路を提供する。

【解決手段】波形等化対象の入力信号(図1では正相入力信号INP)を、nMOS11のソースに入力することで、余計な回路を付加することなく中心電圧が0Vの入力信号に対応可能になる。また、抵抗12aとキャパシタ12bとからなる遅延回路12によって、入力信号の波形は整形され、ノードNOから出力信号(図1では正相出力信号OUTP)が出力される。

(もっと読む)

データ受信装置

【課題】差動伝送路に含まれる各チャネルにおいて、信号に含まれるDCオフセット成分を正確に取り除いて、最適な受信波形に変換する。

【解決手段】TDMSのようにリファレンス・クロックの1チャネルを含む2チャネル以上からなる差動伝送路において、クロック及びデータの各チャネルに対して量子化帰還回路を配設するとともに、クロック信号から振幅情報を抽出し、この振幅情報に基づいてクロック及びデータの各チャネルでの入力信号振幅を推定すると、それぞれのチャネルの量子化帰還回路において量子化帰還出力振幅を入力信号振幅に追随させて、量子化帰還回路の動作条件を成立させる。

(もっと読む)

チャンネルの相互シンボル干渉を減らし、信号利得損失を補償する受信端

【課題】チャンネルの相互シンボル干渉ISIを減らし、信号利得損失を補償する受信端を提供する。

【解決手段】チャンネルを通過した信号を入力するハイパスフィルタと、第1及び第2制御信号に応答してハイパスフィルタの出力と第1電源電圧とを比較して第1及び第2出力信号を発生させるシュミットトリガーとを備えるシングルエンディド信号方式のチャンネルに連結される受信端である。制御部は、シュミットトリガーの第1及び第2トリガー電圧のレベルをシフトさせるために、第1及び第2制御信号を発生させる。増幅部は、シュミットトリガーの第1及び第2出力信号を入力して受信端の出力信号を発生させる。これにより、受信端は、ハイパスフィルタと第1及び第2制御信号によって制御されるシュミットトリガーとによって、データ伝送チャンネルのISIと信号利得損失とを補償する。

(もっと読む)

イコライザ回路

【課題】構成が簡単で雑音が小さく、かつパラメータの調整が容易なイコライザ回路を提供すること。

【解決手段】イコライザ回路は、入力信号を増幅して出力する第1の増幅回路50、入力信号が印加されるフィルタ回路51、フィルタ回路51の出力信号が入力される第2の増幅回路52、第1の増幅回路50の出力信号と第2の増幅回路52の出力信号とを逆相で加算する加算回路53とを備える。フィルタ回路51と第2の増幅回路52の組を複数個備えていてもよい。更に、増幅回路の利得やフィルタ回路の特性を制御する等化特性設定回路54を備える。高精度あるいは低雑音の部品や素子が必要なく、回路構成が簡単である。また、回路が高域に敏感でなくなるので、低雑音化が図れる。更に、イコライザ回路の特性を連続的に変更可能である。

(もっと読む)

等化装置及び方法

【課題】MIMO復号及び構成要素の複雑さを低減した記録可能メディアの読み取りのための等化装置を提供する。

【解決手段】正確計算アナログイコライザと比べて必要とする構成部品の数を減少するために、アナログイコライザは受信ビット値に対する周辺事後期待値の推定値を生成するように動作的に配置された繰り返し手段により特徴付けられる。

(もっと読む)

伝送線路損失の補償手段を有するドライバ回路

【目的】方形波または三角波を元の波形に加算することにより、任意の伝送線路に対して

損失の補償を行なうことが可能なドライバ回路を提供する。

【構成】信号発生器1と、方形波のパルス幅データ、振幅データを格納するレジスタ2と

、レジスタ2に格納したパルス幅データ、振幅データに従って方形波を生成する方形波発

生器3、方形波発生器4および方形波発生器5と、信号発生器1の出力1aと方形波発生

器3の出力3aと方形波発生器4の出力4aと方形波発生器5の出力5aとを加算する加

算器6と、加算器6の出力6aを増幅する増幅回路7とを有し、方形波パルスを信号波形

に加算することにより伝送線路の損失を補償する。

(もっと読む)

エンベロープ検出型リニアライザ装置及び該リニアライザ装置に用いられる歪み補償更新方法

【課題】エンベロープ検出型リニアライザ装置及び該装置に用いられる歪み補償更新方法において、歪補償を早くかつ正確に行うことを目的とする。

【解決手段】データ生成部100より送出されたデータは、DSPである制御/演算部200でプリディストーションされ、ディジタル・アナログ変換器102、直交変調器103、電力増幅器106を介して送信される。送信波の一部は方向性結合器108を通じて直交復調器104に入力される。直交復調器104は、ディジタル信号を復調し、制御/演算部200に入力する。制御/演算部200は、送出されるディジタル信号と該ディジタル信号の送信出力を復調して得た帰還信号との振幅、位相を比較して、例えば、LMS法に従って、送信回路の歪みを演算推定し補償テーブルを作成し、送信ディジタル信号をプリディストーション処理する。

(もっと読む)

イコライザおよび半導体装置

【課題】受信信号のS/N比低下を抑制可能であって、直流信号による断線テストが容易であり、送信信号の再現性に優れたイコライザおよび半導体装置を提供する。

【解決手段】ロウパスフィルタ4は、受信端1から与えられる受信信号を受けて、受信信号から高周波成分を除去した信号を出力する。減算部5は、ロウパスフィルタ4からの出力信号を受信信号から減算する。加算部6は、受信端1からの受信信号と減算部5からの出力信号とを加算する。これにより、加算部6からの出力信号は、高周波成分が強調された周波数特性となる。そして、アンプ2は、加算部6からの出力信号を増幅して、出力端3に送出する。

(もっと読む)

判定帰還型等化方法

【課題】ラインの欠陥を学習しそれらを補償することができるようにする。

【解決手段】等化器は、補償された受信値X(n)と、メモリ装置140からk個の以前の出力値Y(n−1),...,Y(n−k)に対応する記憶値D(n)との組み合わせに基づいて、等化された受信値X’(n)を形成する。更に、等化器は、X’(n)を正のスレシホールドV1および負のスレシホールドV2と比較した結果に基づいて、出力値Y(n)を判定する。Y(n)が0であると判定された時、等化器は、X’(n)が正か負かに基づいて、記憶されている補正値D(n)を所定値Δだけ調節する。

(もっと読む)

1 - 13 / 13

[ Back to top ]