Fターム[5L096LA09]の内容

Fターム[5L096LA09]に分類される特許

1 - 15 / 15

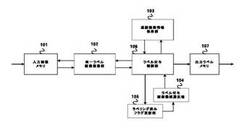

領域成長法によるラベリングの高速化

【課題】領域成長法を用いたラベリング処理を高速化する。

【解決手段】入力画像メモリと、近傍画素から処理対象画素と同一のラベルが付与される条件を満たす画素を探索する同一ラベル画素探索部と、前記同一ラベル画素探索部から出力される連結対象画素の位置情報を記録する連結画素情報保持部と、処理対象画像の全画素について「ラベル付与済み画素フラグ」を保持するラベリング済みフラグ更新部と、「ラベル付与済み画素フラグ」からプライオリティエンコーダにより次にラベルを付与する画素候補の位置情報を1つ選択して出力するラベル付与画素候補選択部と、前記連結画素情報保持部で保持される連結画素の情報と前記ラベル付与画素候補選択部の出力情報から次にラベルを付与する処理対象の画素と次のラベル番号とを決定するラベル付与制御部と、画素位置とラベル番号を基に各々の画素のラベル番号を書き込む出力ラベルメモリとを有する。

(もっと読む)

情報絞り込み検出機能を備えたメモリ、その使用方法、このメモリを含む装置。

【課題】

パターン認識など情報検出の最大の課題は検索時間でありメモリの逐次比較処理が不要な非ノイマン型情報検出メモリを実現する。

【解決方法】

メモリアドレスごとに情報を記憶しその情報を読み出し可能なメモリで、このメモリは、外部から与えられる第1のデータは記憶されたメモリのデータを比較するためのデータ、第2のデータはアドレス同士を比較するためのデータ、の双方の入力データの入力手段と、この入力手段から与えられた上記双方の入力データにより記憶された情報のデータと、そのアドレスと、の双方を二重並列に合否判定し、その双方の合否判定結果をさらに並列に論理演算する手段と、上記論理演算に合格するこのメモリの上記アドレスを出力する手段と、を具備することを特徴とする情報絞り込み検出機能を備えたメモリであるのでインテリジェンスな情報検索はもとより人工知能等に広く利用可能である。

(もっと読む)

目標追跡装置及び目標追跡方法

【課題】安定した目標追跡を継続し得る目標追跡装置を提供する。

【解決手段】指示される画像サイズ及び画像位置に基づいて、任意の画像サイズで任意の位置に存在する移動目標の画像データを取得する撮像部11と、この撮像部11の出力画像から1フレームにおける移動目標の画素を特定する画素アドレスを算出する画素アドレス算出部13と、この画素アドレス算出部13で得られる出力画像の目標画素アドレスのフレーム間におけるずれ量を算出し、この算出結果に基づいて撮像部11に指示する画像サイズ及び画像位置を含む追跡信号を生成する信号処理部14とを備える。

(もっと読む)

画像処理システム及び画像処理方法

【課題】テンプレート・マッチングのような画像処理に要する最大処理時間を短縮することが可能な画像処理システムを提供する。

【解決手段】画像処理システムは、探索対象画像の中からテンプレート画像と一致する一致領域を探索する。操作処理部501と、抽出処理部502と、計算処理部503と、特定処理部504とを具備する。操作処理部501は、連続した複数の第1ビットの各々を順次操作して、不連続な複数の第2ビットの各々を順次生成する。抽出処理部502は、順次生成される第2ビット毎に、探索対象画像の中の連続的な探索順の位置のうち、第2ビットに対応した探索位置で部分領域を抽出する。計算処理部503は、抽出された部分領域とテンプレート画像との類似性に関する指標を算出する。特定処理部504は、複数の第2ビットに対応した複数の部分領域について算出された複数の指標に基づいて、複数の部分領域から一致領域を特定し、一致領域の位置としての合致位置を特定する。

(もっと読む)

情報処理装置及び情報処理方法

【課題】累積画像情報の保持に必要なメモリリソースを低減することを目的とする。

【解決手段】累積画像情報保持メモリを含んで構成される情報処理装置が、入力画像情報を読み込む情報入力部と、情報入力部で読み込まれた入力画像情報と、複数の画素のうち指標とする画素の位置を示す画素パターンとに基づいて、指標とする画素の位置に対応する入力画像情報の位置についての累積画像情報を生成する累積画像情報生成部と、累積画像情報生成部で生成された累積画像情報を累積画像情報保持メモリに記憶するメモリコントローラと、を有することによって課題を解決する。

(もっと読む)

画像処理装置および画像処理方法

【課題】コンピュータなどのデバイスの画面の変化を効率よく検出する。

【解決手段】

ディスプレイタイミング設定部16は画像をラスタースキャンにより描画するためのタイミングを決定する。ピクセル読出部10はディスプレイタイミング設定部が出力するタイミングに応じてピクセルを読み出す。関心領域情報入力部20は画像中に任意の関心領域を特定するための情報を入力する。関心領域特定部26はディスプレイタイミング設定部16が出力するタイミングに基づいて、前記ピクセルが関心領域に含まれるか否かを特定する。有限ビット生成部30は前記ピクセルが関心領域に含まれる場合には、前記ピクセルの情報を写像変換することにより有限ビット列を生成する。

(もっと読む)

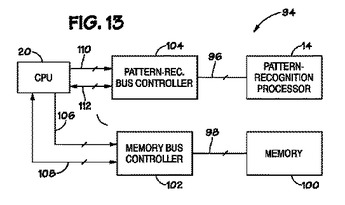

パターン認識プロセッサのためのバス

開示されているのは次のような方法およびシステムである。パターン認識プロセッサ(14)、そのパターン認識プロセッサ(14)にパターン認識バス(96)を介して接続される中央処理装置(CPU)(20)、およびCPU(20)にメモリバス(98)を介して接続されるメモリ(100)を有するシステム(94)である。幾つかの実施形態において、パターン認識バス(96)およびメモリバス(98)は、それぞれパターン認識プロセッサ(14)およびメモリ(100)に対するほぼ同数の接続を形成する。  (もっと読む)

(もっと読む)

正規化相関処理装置

【課題】ウィンドウ位置がランダムな場合も対応可能な正規化相関処理装置を提供する。

【解決手段】ウィンドウを格納するウィンドウバッファをダブルバッファ構成とし、各バッファに充填する矩形領域のサイズを任意に指定可能とする。ウィンドウ位置の指定がランダムで、ウィンドウ同士が大きく重なるような場合には、1つのウィンドウバッファに複数のウィンドウを格納するようにして、ウィンドウの読み出しの際に、キャッシュ効果が現れるようにする。

(もっと読む)

演算処理装置および方法

【課題】CNN演算等のネットワーク構造で接続された複数の処理ノードによって行われる演算処理を、限られたメモリ量で効率良く実現する。

【解決手段】入力データに対して演算を行い演算結果データを生成する、複数の論理的な処理ノードを接続した階層型ネットワークでネットワーク演算を実行する演算処理装置は、ネットワークを構成する複数の処理ノードの各々に対応して演算結果データを保持するための中間バッファ用の記憶領域をメモリに割り当てるための複数種類のバッファ割り当て方法のそれぞれについて、ネットワーク演算に必要なメモリ量を当該ネットワーク演算の構成に基づいて算出し、算出されたメモリ量に基づいて選択されたバッファ割り当て方法に応じた実行順でネットワーク演算を実行させる。

(もっと読む)

出現色ヒストグラム作成回路及び画像処理装置

【課題】

最頻出色を必要とする画像処理時に,CPUに,最頻出色を特定する処理を行わせる必要がない画像処理装置を、提供する。

【解決手段】

複合機等の画像処理装置に、処理対象画像データに関する出現色ヒストグラムをSRAM23上に作成しながら、処理対象画像データに関する最頻出色(最頻出色レジスタ25)を求めてしまう出現色ヒストグラム作成回路20(頻度レジスタ24上の値を超える頻度をSRAM23に書き込む際に、当該頻度及び色データを,それぞれ,頻度レジスタ24及び最頻出色レジスタ25に記憶しておく回路)を搭載しておく。

(もっと読む)

ブロックで保存された参照画像からテストブロックを取得する方法及び装置

【課題】 本発明は、ブロックで保存された参照画像から自由に選択できる位置でのテストブロックの取得に関する。

【解決手段】 ブロックで保存された参照画像からテストブロックを取得する方法が記載されている。当該方法は、参照ブロック(110)を取得する手順、及び前記参照ブロック(110)から第1コロナブロック(130,140,160,170)を生成する手順を有する。続いてテストブロック(180)は、前記参照ブロック(110)の小区分及び前記第1コロナブロック(130,140,160,170)の小区分を用いて作られる。

必要なときにコロナブロックを生成する方法では、コロナ(130,140,160,170)は、ブロックでのアクセスが可能な記憶装置(10)内に保持されている必要はない。これにより、記憶容量が節約される。

(もっと読む)

画像処理装置

【課題】画像データの輝度ヒストグラムの作成処理を高速化するための技術を提供する。

【解決手段】画像処理装置100が有するヒストグラム作成部101は、複数の色データからなる画素データを複数含む画像データの輝度ヒストグラムを作成する。ヒストグラム作成部101は、同系色に分類される画素の個数を特定する個数情報を、該分類ごとに記憶するヒストグラム作成用メモリ113と、画素データに含まれる各色データの一部のデータにマスクをかけてアドレスデータを生成するアドレス変換部111と、ヒストグラム作成用メモリ113にアクセスして、アドレス変換部111が生成したアドレスで特定される個数情報をインクリメントすることにより輝度ヒストグラムを作成するメモリ制御部112と、を有する。

(もっと読む)

動き検出処理装置および方法

【課題】処理速度の低下や消費電力の増加を防止することのできる動き検出処理装置を提供。

【解決手段】アドレス生成回路16には探索対象ブロック格納用RAM 12と参照ブロック格納用RAM 14が接続され、アドレス信号18に応じて差分絶対値演算回路24には探索対象ブロックの画素データと参照ブロックの画素データが入力されて差分絶対値が算出される。分割エリアの差分絶対値は差分絶対値保存レジスタ30にそれぞれ保持され、最大値検出回路42は、これら保持されている値の最大値を検出し、最大値に対応するエリアを示すエリア情報とクロック信号とをアドレス生成回路16に出力する。累積演算回路32では、差分絶対値から1ブロック分の総和を算出し、算出した差分絶対値和(SAD)をSAD値比較回路52に出力し、SAD値が最小のものでないことを検出するとリセット信号54を生成して現在処理を行なっているブロックの差分絶対値演算を中断する。

(もっと読む)

データ記憶装置、データ検索装置、データ再生装置、データ検索プログラム

【課題】 データ記憶において、コンテンツデータとこのコンテンツデータが記憶されたアドレスとを関連づける。

【解決手段】

メモリシステム1は、入力部10を通じて入力された第1のデータ列をカオス力学系関数に基づく関数演算によって第1の実数値に畳み込む畳み込み演算部22と、上記第1の実数値を記憶部30のデータ格納位置に対応づけ、上記第1のデータ列に関連づけられた関連づけデータを上記データ格納位置に格納する制御部20を備える。

(もっと読む)

ヒストグラム生成装置及び方法

【課題】画像データの濃度値の出現頻度(ヒストグラム)を高速に作成する。

【解決手段】入力データをD−FF110で1周期分遅延させ、第2セレクタ112で遅延データとD−FF110で遅延されていないデータとを半周期ずつ交互に選択出力する。第2セレクタ112からのデータをアドレスとして周期の前半でメモリ116からデータを読み出し、後半で加算器120により1だけ加算されたデータをメモリ116に書き込む。比較器108で連続する2つのデータが一致するか否かを判定し、一致する場合には変更器102で変更されたデータを第1セレクタ104で選択してD−FF106に供給する。

(もっと読む)

1 - 15 / 15

[ Back to top ]