Fターム[5L106DD35]の内容

半導体メモリの信頼性技術 (9,959) | 試験 (2,465) | 加速試験、ストレス (225)

Fターム[5L106DD35]の下位に属するFターム

電源電圧を変化させるもの (59)

周波数を変化させるもの (28)

Fターム[5L106DD35]に分類される特許

1 - 20 / 138

半導体記憶装置

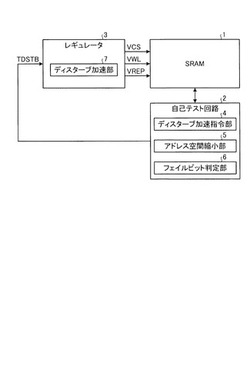

【課題】メモリセルの各トランジスタの特性のランダムばらつきについてのテストを効率化する。

【解決手段】メモリセルMCの動作をテストする自己テスト回路2と、自己テスト回路2からの加速指令に基づいて、メモリセルMCのディスターブが加速するようにワード線WL1〜WLnの電圧VWLまたはメモリセルMCのセル電源電圧VCSを設定するレギュレータ3とを備える。

(もっと読む)

半導体記憶装置

【課題】SRAMセルやセンスアンプの駆動トランジスタのしきい値電圧(Vth)を補正することを可能とする技術を提供する。

【解決手段】データを保持するラッチ回路と、データを伝送する信号線とを備える半導体装置を構成する。ラッチ回路は、第1インバータと、第2インバータとを具備する。第1、第2インバータのそれぞれの出力からビット線(BL0、BL1)やセンスアンプ信号線(SA0、SA0B)を経由してGNDへ至る電気的経路を備え、その電気的経路は、第1のトランジスタを備えるものとする。そして、Vt補正モードには、第1インバータまたは第2インバータの一方のHighレベルを供給し他方にLowレベルを供給することで、第1のトランジスタにより電気的経路を導通する。

(もっと読む)

半導体記憶装置

【課題】マーチパターンテストではアドレスデコーダの配線の遅延を検知できない。

【解決手段】半導体記憶装置のアドレスデコーダは,アドレスサイクルの第1のタイミングで,複数の入力アドレス信号それぞれの非反転及び反転論理レベルを有する第1と第2の内部アドレス信号を出力するアドレスレジスタと,複数の入力アドレス信号の第1と第2の内部アドレス信号を伝播する複数の内部アドレス信号線を有する内部アドレス信号線網と,アドレスレジスタと内部アドレス信号線網の間に設けられ,アドレスレジスタが出力した第1と第2の内部アドレス信号を,アドレスサイクルの第1のタイミング後の第2のタイミングで一定の論理レベルにリセットするリセット回路と,内部アドレス信号線網を介して複数の入力アドレス信号の第1と第2の内部アドレス信号の組合せを供給され,当該組合せを論理演算してそれぞれのワード線又はビット線を選択する複数のアドレスデコード回路とを有する。

(もっと読む)

半導体装置及びそのテスト方法

【課題】ディスターブ試験時のノイズを低減しサイクル高速化を実現する技術を提供する。

【解決手段】本発明による半導体装置は、ワード線及びビット線に接続された複数のメモリセルを含み、複数のバンクに分割されたメモリセルアレイと、テスト動作時に、テスト回路用アドレス信号とディスターブ試験用テスト信号を用いて、バンク毎にワード線を内部アドレス信号に応じて別々のタイミングで選択するロウ周辺回路とを備える。

(もっと読む)

半導体装置

【課題】テスト時間の短縮化を図ることが可能な半導体装置を提供する。

【解決手段】このチャージポンプ回路12では、通常動作時は、ポンプキャパシタC0,C2の一方電極にポンプクロック信号φPを与えるとともにポンプキャパシタC1,C3の一方電極にポンプクロック信号φPの相補信号を与え、ポンプキャパシタC0〜C3の欠陥を検出するテストモード時は、ポンプキャパシタC0〜C3の各々の電極間に外部電源電圧VCCを静的に印加する。したがって、MOSトランジスタのオン耐圧を超える高電圧をポンプキャパシタC0〜C3に印加できるので、テスト時間を短縮化できる。

(もっと読む)

半導体記憶装置およびそのテスト手法

【課題】短時間でライト動作不良をテストすることができる、半導体記憶装置、及びそのテスト方法を提供すること。

【解決手段】非テスト対象ポートに対応するワード線を活性化させ、非テスト対象ポートに対応するプリチャージ信号を非活性にすることにより、非テスト対象ポートに対応する前記ディジット線対の一方を放電させる。放電後の前記ディジット線対の電位差が保たれた状態で、複数のワード線を活性化させ、テスト対象ポートに対応するディジット線対を駆動することにより、メモリセルにテストデータを書き込む。その後、メモリセルからデータを読み出し、テストデータが正しく書き込まれていたか否かを判定する。

(もっと読む)

半導体メモリ、システムおよび半導体メモリの製造方法

【課題】 アドレス端子で受ける外部アドレスを用いて、リアルワード線を選択することなく、任意の冗長ワード線を選択する。

【解決手段】 半導体メモリは、複数のリアルワード線および複数の冗長ワード線を有するメモリブロックと、アドレス端子で受ける外部アドレスの一部である第1アドレスをデコードして第1デコード信号を出力し、テストモード中にデコード動作を禁止する第1デコーダと、通常動作モード中に、外部アドレスの別の一部である第2アドレスまたは不良の救済に使用する冗長ワード線を示す冗長アドレスをデコードし、テストモード中に第2アドレスをデコードし、第2デコード信号を出力する第2デコーダと、第1デコード信号および第2デコード信号に応じて、リアルワード線を選択する第1ドライバと、第2デコード信号に応じて、冗長ワード線を選択する第2ドライバとを有している。

(もっと読む)

半導体装置

【課題】ウェハレベルバーンインテスト時におけるクロックツリー配線のNBTI劣化を防止する。

【解決手段】通常動作時においては内部クロック信号DLLCLKを生成し、ウェハレベルバーンインテスト時においては内部クロック信号DLLCLKの生成を停止するディレイライン24aと、内部クロック信号LCLKを伝送するクロックツリー配線25と、ウェハレベルバーンインテスト時において、セルフリフレッシュタイミング信号SLFをダミークロック信号としてクロックツリー配線25に供給するセレクタ51,24bとを備える。本発明によれば、ウェハレベルバーンインテスト時においてダミークロック信号を供給していることから、ウェハレベルバーンインテストによるクロックツリー配線のNBTI劣化を防止することが可能となる。

(もっと読む)

WLBIテスト方法

【課題】ビット線を個別に制御することができ、同一センスアンプ列内の隣接ビット線間に“H/L”逆相ストレスパタンを印加できると共に、限定されない種々のストレスパタンをメモリセルに印加できるWLBIテスト方法を提供する。

【解決手段】半導体記憶装置にストレスを印加するのに先立ち、複数のメモリセルを活性化する一方、複数のセンスアンプは非活性状態を維持し、グローバル入出力線GIOB<0>〜<7>、GIOT<0>〜<7>を利用して各ビット線に個別に充電を行う。

(もっと読む)

不揮発性半導体記憶装置、および不揮発性半導体記憶装置の保持マージン検査方法

【課題】データ保持マージンチェックを高速化する技術を提供する。

【解決手段】不揮発性の記憶領域(5)にデータを記憶するメモリ部(2)と、記憶領域(5)に保持されているデータの状態を検査するためのデータ保持マージン検査用データを生成するメモリ制御回路(3)とを具備する不揮発性半導体記憶装置(1)を構成する。メモリ制御回路(3)は、通常のデータ読み出し電圧よりも高いマージン検査用読み出し電圧で、記憶領域(5)から連続的に読みだされたデータに基づいて誤り検出用コード(CRCコード)を生成する。比較回路(25)は、通常のデータ読み出し電圧に基づいて供給される比較用データ(CRCコード)と、誤り検出用コード記憶回路(24)に保持された誤り検出用コード(CRCコード)とを比較した比較結果を、データ保持マージン検査用データとして出力する。

(もっと読む)

半導体装置

【課題】テスト動作時の消費電力を削減できる半導体装置を提供する。

【解決手段】半導体装置は、外部クロック信号を受け取る第1の端子と、第1の端子に接続され、外部クロック信号に応じて内部クロック信号を発生するクロック発生回路と、複数のワード線及び複数のビット線と、複数のビット線にそれぞれ接続された複数の増幅回路と、テスト動作時に、第1の期間の間、複数のワード線のうちの1又は複数のワード線を内部クロック信号に応じて選択状態と非選択状態とを繰り返すように制御し、かつ、第1の期間の間、複数の増幅回路を活性状態に維持し、通常動作時には、複数のワード線のうち1又は複数のワード線の選択状態と非選択状態との切り換えに応じて複数の増幅回路の活性状態と非活性状態とを切り換えるように制御する制御部と、を備える。

(もっと読む)

半導体記憶装置

【課題】トランスファMOSトランジスタが正常に動作しない場合の不良を検出する。

【解決手段】半導体記憶装置(31)は、スタティック型のメモリセル(MC)と、ワード線(WL1〜WLm)と、ビット線(BL1,/BL1〜BLn,/BLn)とを含む。また上記半導体記憶装置(31)は、上記ビット線を上記メモリセルに結合するためのトランスファMOSトランジスタ(11,14)と、上記ビット線をハイレベルに駆動するための第1駆動回路(17,18,21,22)と、上記ビット線をローレベルに駆動するための第2駆動回路(19,20,23,24)とを含む。このとき、テストモードにおいて、上記第1駆動回路によるビット線駆動機能を停止させるための制御論理(26)を設けることで、トランスファMOSトランジスタが正常に動作しない場合の不良を検出可能にする。

(もっと読む)

ワード線電位制御回路

【課題】製造バラツキや動作温度などに応じてワード線電位を適正化する。

【解決手段】複数のメモリセルMCがアレイ状に配列されたメモリセルアレイ1において、メモリセルMCの特定の特性を制御し、メモリセルMCの特定の特性が制御された時の特性の分布に基づいて、ワード線wl_0〜wl_mの電位を調整する。リード/ライト回路7を介してメモリセルアレイ1の全てのメモリセルMCからデータが読み出される。そして、カウンタ8において、メモリセルMCから読み出されたデータの反転数がカウントされ、コンパレータ11に出力される。また、セレクタ10において、期待値N2が選択され、コンパレータ11に出力される。そして、コンパレータ11において、メモリセルMCから読み出されたデータの反転数と期待値N2が比較され、その比較結果がソース電位制御部13に送られる。

(もっと読む)

半導体装置

【課題】低周波数のクロックしか供給できないバーンインテスタを用いた場合であっても、テストに長時間を要するディスターブテストを、高周波数で実行可能な半導体装置を提供する。

【解決手段】テスト動作モードにおいて、ロウアドレスバッファ部12dにより、第1のワード線の位置を示すロウアドレスを取り込む。制御回路18a及びタイミング制御回路18bは、第1のワード線とビット線対を共有する第1のワード線とは異なる第2のワード線を選択し、当該ワード線に接続されるメモリセルのリフレッシュ動作を、外部から供給されるクロック信号の第1の周波数に比べて高い第2の周波数で実行する、ことを特徴とする。

(もっと読む)

記憶装置、半導体装置、検出方法

【課題】データの保持時間が所定の長さに満たないメモリセルを検出するための検証動作を、短時間にて正確に行うことができる記憶装置の提供。

【解決手段】各メモリセルに、第1容量素子と、第2容量素子と、上記第1容量素子及び第2容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子として機能するトランジスタと、を少なくとも有する。また、第1容量素子の容量値が、第2容量素子の容量値の1000倍以上、好ましくは10000倍以上となるようにする。そして、通常動作の時に、第1容量素子及び第2容量素子を用いて電荷の保持を行う。また、データの保持時間が所定の長さに満たないメモリセルを検出するための検証動作を行う時に、第2容量素子を用いて電荷の保持を行う。

(もっと読む)

メモリテスタ

【課題】

実施形態は、検査効率を向上可能なメモリテスタを提供する。

【解決手段】

本実施形態のメモリテスタによれば、複数の検査メモリのリードのそれぞれに電気的に接続可能なコネクタを複数個有するテストボードと、第1入出力部と、前記検査メモリを選択する第1選択部を有し、前記第1入出力部と複数の前記検査メモリが電気的に共通に接続され、前記第1選択部と前記検査メモリが電気的に共通に接続されて第1検査モードを行う第1検査装置と、第2入出力部と、前記検査メモリを選択する第2選択部を有し、前記第2入出力部及び前記第2選択部が対応する複数の前記コネクタそれぞれに接続されて第2検査モードを行う第2検査装置とを備えることを特徴とする。

(もっと読む)

半導体装置

【課題】ストレステストにおいて同時に立ち上げるワード線の本数を増やす。

【解決手段】複数のセンスアンプ列32によって複数のメモリセルマットMATに分割され、其々が複数のワード線WLを備えるメモリセルアレイ30と、複数のメモリセルマットMATの内、選択された互いに隣接しない複数のメモリセルマットMATに其々含まれる複数のワード線WLを同時に立ち上げるテスト制御を行うテスト回路25とを備える。本発明によれば、複数のワード線WLが立ち上がるメモリセルマットMATを分散させていることから、一つのメモリセルマット内において多数のワード線を立ち上げる場合に比べて、ワード線を駆動するためのドライバ回路や、ドライバ回路に動作電圧を供給する電源回路への負荷が軽減する。その結果、より多数のワード線を同時に立ち上げることが可能となる。

(もっと読む)

半導体装置

【課題】半導体装置におけるライン不良とコンタクト不良を効率的に判別する。

【解決手段】半導体装置10は、同一のカラム選択信号線によりローカルIO線との接続を制御されるビット線グループを複数備える。不良検出回路100は、第1のビット線グループから読み出される第1データグループと、第2のビット線グループから読み出される第2データグループを比較することにより、第1および第2のビット線グループのいずれかにおいて、カラム選択信号線との接続不良(コンタクト不良)が発生していないかを検出する。

(もっと読む)

半導体記憶装置

【課題】2個の隣接する列ブロックのいずれにも欠陥がある場合でも、これらの列ブロックの救済が可能な半導体記憶装置を提供する。

【解決手段】データ線シフト回路58は、偶数番目の正規ブロックに欠陥がある場合に、偶数番目の正規ブロックおよび偶数番目のスペアブロックを対象としたシフトリダンダンシ方式によって、偶数番目の内部正規データ線NIOXおよび偶数番目の内部スペアデータ線SIOXと偶数番目の外部データ線EIOXとの接続を行ない、奇数番目の正規ブロックに欠陥がある場合に、奇数番目の正規ブロックおよび奇数番目のスペアブロックを対象としたシフトリダンダンシ方式によって、奇数番目の内部正規データ線NIOXおよび奇数番目の内部スペアデータ線SIOXと奇数番目の外部データ線EIOXとの接続を行なう。

(もっと読む)

半導体装置

【課題】ビット線とデータバス線の接続を制御するカラム選択トランジスタの不良をデータバス線を介して検出することを可能とする半導体装置の提供。

【解決手段】ビット線と、前記ビット線に対応するデータバス線と、前記ビット線と前記データバス線との電気的な接続を制御する選択トランジスタと、前記ビット線に前記データバスを介してデータを書き込むライトアンプと、テスト回路と、を備え、前記テスト回路は、テスト期間中に、前記ライトアンプの動作に係わらず、前記ビット線を第1の電位に設定し、前記データバス線を第2の電位に設定し、その後、前記データバス線をフローティングに設定し、前記選択トランジスタが活性され、前記ビット線と前記データバス線とが電気的に接続されることにより、前記データバス線が前記第2の電位から前記第1の電位に遷移することを検出する。

(もっと読む)

1 - 20 / 138

[ Back to top ]