Fターム[5L106EE04]の内容

半導体メモリの信頼性技術 (9,959) | 障害・試験箇所 (1,040) | 入出力回路 (137) | 書込み回路 (59)

Fターム[5L106EE04]に分類される特許

1 - 20 / 59

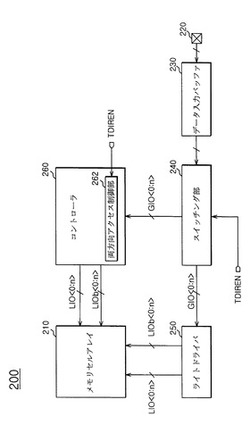

半導体メモリ装置及びそのためのテスト回路

【課題】本発明は、テスト速度を向上させることができる半導体メモリ装置及びそのためのテスト回路に関するものである。

【解決手段】本発明に係る半導体メモリ装置は、複数のメモリセルを含むメモリセルアレイ;データ入出力パッドに接続され、テストモード信号に応じて前記データ入出力パッドに印加されたデータの伝達経路を制御するスイッチング部;ノーマルモード時、前記スイッチング部から伝達されるデータを駆動して、前記メモリセルアレイに書き込むライトドライバ;及び、テストモード時、前記スイッチング部から伝達されるデータを前記メモリセルに伝達するコントローラを含む。

(もっと読む)

試験装置および試験方法

【課題】アドレスを反転制御することができる。

【解決手段】被試験メモリのアドレスを発生するアドレス発生部と、アドレス発生部により発生されたアドレスをビット反転して被試験メモリに供給するか否かを選択する選択部と、アドレスをビット反転することを選択部が選択した場合にアドレス発生部により発生されたアドレスをビット反転して出力し、アドレスをビット反転しないことを選択部が選択した場合にアドレス発生部により発生されたアドレスをビット反転せずに出力する反転処理部と、反転処理部が出力した反転制御されたアドレス、および、反転処理部が出力したアドレスがビット反転したアドレスであるか否かを示す反転サイクル信号を、被試験メモリへと供給する供給部と、を備える試験装置を提供する。

(もっと読む)

半導体装置

【課題】チップサイズの増大を抑制でき、評価精度を落とすことなく、パラレルテストの時間の増大を抑制できる半導体装置を提供する。

【解決手段】複数のメモリアレイと、読み出し動作においては、メモリセルからの読み出しデータを増幅して外部へ出力するリードデータを生成し、書き込み動作においては、外部から供給されるライトデータに基づいてメモリセルへの書き込みデータを生成する、複数のメモリアレイに共通に設けられたリードライトアンプ(RWAMP)と、複数のメモリアレイ毎に設けられたスイッチと、複数のメモリアレイのうち活性化するメモリアレイのスイッチを順次導通させる第1の制御信号(LMIOSW)を生成する第1の制御回路(12b)と、リードライトアンプを活性化する第2の制御信号(DAE)を、活性化するメモリアレイの個数に基づいて発生する第2の制御回路(14)と、を備える。

(もっと読む)

半導体メモリ、システムおよび半導体メモリの製造方法

【課題】 アドレス端子で受ける外部アドレスを用いて、リアルワード線を選択することなく、任意の冗長ワード線を選択する。

【解決手段】 半導体メモリは、複数のリアルワード線および複数の冗長ワード線を有するメモリブロックと、アドレス端子で受ける外部アドレスの一部である第1アドレスをデコードして第1デコード信号を出力し、テストモード中にデコード動作を禁止する第1デコーダと、通常動作モード中に、外部アドレスの別の一部である第2アドレスまたは不良の救済に使用する冗長ワード線を示す冗長アドレスをデコードし、テストモード中に第2アドレスをデコードし、第2デコード信号を出力する第2デコーダと、第1デコード信号および第2デコード信号に応じて、リアルワード線を選択する第1ドライバと、第2デコード信号に応じて、冗長ワード線を選択する第2ドライバとを有している。

(もっと読む)

抵抗変化メモリのテスト装置、方法および抵抗変化メモリ装置

【課題】任意のテストサイクルにおけるサイクル時間を局所的に自由に調整するとともにチップサイズ、テストコストを削減する。

【解決手段】シフトレジスタ回路の出力と第1のライトイネーブル信号とに基づき、複数のシーケンスのうちの限界時間の確認を行うシーケンスに対応して信号変化する第2のライトイネーブル信号を発生し、第1および第2のライトイネーブル信号を用いて信号変化する時間間隔が局所的に前記第1のライトイネーブル信号の周期よりも短い複数のコア制御信号を発生し、発生した複数のコア制御信号を用いて抵抗変化メモリの動作確認を行う。

(もっと読む)

半導体装置及びその制御方法

【課題】電気ヒューズ素子からなるヒューズ回路をウェハ状態である前工程における一次救済及びパッケージ後である後工程における二次救済の両方で有効に利用する。

【解決手段】複数のアンチヒューズセットAFSETを含むヒューズ回路50と、ヒューズ回路50に書き込むべきアドレスを電気的に保持するヒューズアドレスレジスタ70と、ヒューズ回路50にアドレスを書き込むプログラム回路40とを備える。プログラム回路40は、第1のテストコマンドが発行された場合には該第1のテストコマンドと共に外部から入力されたアドレスをヒューズ回路40に書き込み、第2のテストコマンドが発行された場合には際にヒューズアドレスレジスタ70に保持されたアドレスをヒューズ回路50に書き込む。これにより、通常の後工程用のテスタを用いて不良メモリセルを冗長メモリセルに正しく置換することが可能となる。

(もっと読む)

メモリ試験装置及びメモリ試験方法

【課題】本発明は、半導体メモリデバイスを試験するメモリ試験装置に関し、シリアル・メモリデバイスのメモリ試験を簡単な構成で確実に実施できるようにする。

【解決手段】被試験デバイスのシリアルデータ入力ピンに与えるためのコマンドおよびデータと、それらに対応付けられるアドレスのアドレス発生指示を含む試験情報を設定する試験情報設定部10と、その試験情報に基づきアドレス発生指示に対応付けたコマンドとデータを発生する実行制御部11と、実行制御部11からのアドレス発生指示に基づき前記入力ピンに与えるためのアドレスを生成する試験アドレス生成部12と、そのアドレスと実行制御部11からのコマンドとデータを対応付け合成してアドレス単位の試験データを生成する試験データ合成部13と、生成された試験データのコマンド、アドレスおよびデータ各々の多ビット構成データを共通のシフト演算構成によってシリアルデータ化して前記入力ピンに与えるシリアルデータ演算生成手段14とを備える。

(もっと読む)

半導体装置および半導体装置の検査方法および半導体装置の駆動方法

【課題】メモリセルアレイの配線を切断したり、個々のメモリセルあるいは行や列にプローバーを当てたりせずに、特定のメモリセルへの書き込みを制限する方法を提供する。

【解決手段】書き込めなくするメモリセルの行アドレスデータと列アドレスデータをレジスタに格納する。また、書き込み制御をおこなうイネーブルデータをレジスタに格納する。次に、メモリセルへの書き込みをおこなうために、論理回路から書き込みするメモリセルの列アドレスデータ、行アドレスデータ、書き込みイネーブルデータ等の出力により、レジスタに格納したアドレスデータに相当するメモリセルへの書き込みを禁止する。

(もっと読む)

半導体装置及びその試験方法

【課題】非圧縮の実データを入出力する動作試験を高速に行う。

【解決手段】試験プローブ6aによって電気的に共通接続される複数のデータ入出力端子DQ0〜DQn及びストローブ端子DQSと、試験プローブ6bに接続されるコマンドアドレス端子CAと、コマンドアドレス端子CAに入力される信号に基づいて、データ出力回路10〜1nの選択動作を行う出力制御回路31と、を備える。本発明によれば、テスタ内の1つの判定回路に複数のデータ入出力端子を割り当てつつ、非圧縮の実データを用いたテストを行うことが可能となる。これにより、テスタ内の限られた数の判定回路を用いてより多数の半導体装置を並列にテストすることが可能となる。

(もっと読む)

半導体装置、及び半導体試験方法

【課題】半導体装置を検査する検査時間を短縮できる半導体装置を提供する。

【解決手段】半導体装置は、変更レジスタ部13が、予めレジスタ部12に格納されているデータを変更する変更データを格納する。論理合成部14が、データと変更データとの論理合成処理を行う。変換部17が、変更データの値を変換する付加情報に基づいて前記変更データの値を変換し、論理合成部14に供給する。これにより、論理合成部が、論理合成処理を行った結果に変換することができ、半導体装置を検査する検査時間を短縮する。

(もっと読む)

半導体装置およびそのテスト方法

【課題】動作テストに係る時間を短縮することが可能な相変化メモリを提供する。

【解決手段】ライト回路10は、第1の論理レベルを示す入力データ信号である第1データ信号を各メモリバンクBANK0〜7に順番に書き込み、第2の論理レベルを示す入力データ信号である第2データ信号を各メモリバンクBANK0〜7に同時に書き込む。半導体装置は、複数の相変化メモリバンクと、第1の論理レベルを示す入力データ信号をリセット動作にて各メモリバンクに順番に書き込み、第2の論理レベルを示す入力データ信号をセット動作にて各メモリバンクに同時に書き込むライト回路と、を備える。テスト方法は、第1の論理レベルを示す入力データ信号である第1データ信号を各メモリバンクに順番に書き込み、第2の論理レベルを示す入力データ信号である第2データ信号を各メモリバンクに同時に書き込む。

(もっと読む)

テストボード

【課題】 複数の被テストデバイスのテストを高速かつ個別に行えるテストボードを提供する。

【解決手段】 テストボード41は、複数の伝送線路48と、第n(n<N,n:自然数,N:2以上の整数)の接続点Aと第n+1の接続点Bの間の伝送距離が複数の伝送線路48の全てについて等しくなるように、複数の伝送線路48の各々の一端と他端との間に設けられた第1乃至第Nの接続点Bを備える。

(もっと読む)

故障検出方法、半導体装置、マイクロコンピュータ応用システム

【課題】故障検出の対象とされる回路のアナログ量を変化させて故障検出を行うことにより、故障検出精度を向上させる。

【解決手段】チューニング回路(104A)によって、所定の条件下で上記被故障検出回路(104B)のアナログ量を変更し、上記被故障検出回路におけるアナログ量の変化に基づく上記被故障検出回路の状態変化を、故障検出回路(103)によって判別して上記被故障検出回路の故障を検出する。これにより、故障検出回路(103)の出力を半導体装置の外部でモニタすることなく、上記被故障検出回路の故障を検出することができる。しかも、上記被故障検出回路におけるアナログ量の変化に基づく上記被故障検出回路の実際の状態変化を故障検出回路によって判別するようにしているため、故障検出の精度の向上を図ることができる。

(もっと読む)

試験装置および試験方法

【課題】被試験メモリの試験を被試験メモリの容量よりも少ない内部メモリで試験する。

【解決手段】被試験メモリを試験する試験装置であって、被試験メモリの一部のメモリ領域に対応する試験データおよび試験結果の少なくとも一方の試験情報を記憶する内部メモリを有し、被試験メモリを試験する試験用集積回路デバイスと、被試験メモリの全メモリ領域に対応する試験情報を記憶する外部メモリと、外部メモリに接続され、試験対象のメモリ領域に応じた試験情報を外部メモリおよび内部メモリの間で転送するメモリコントローラと、を備える試験装置および試験方法を提供する。

(もっと読む)

半導体集積回路の試験装置、試験方法、及びプログラム

【課題】 本発明の課題は、半導体集積回路の試験装置が試験パタンデータを生成して半導体集積回路へ書き込むことを目的とする。

【解決手段】 上記課題は、半導体集積回路のメモリへの書き込みを試験するための試験パタンデータを生成するパタンデータ生成手段と、前記試験パタンデータを前記半導体集積回路の該試験パタンデータを格納する記憶領域へ書き込む書き込み手段と、を有することを特徴とする半導体集積回路の試験装置により達成される。

(もっと読む)

薄膜磁性体記憶装置

【課題】磁性体メモリセルのデータ誤書込に対する耐性を効率的にテストする。

【解決手段】メモリセルの各行に対応してライトディジット線WDLが配置される。データ書込時には、データ書込対象のメモリせルが含まれるメモリセル行に対応するライトディジット線WDLが選択的に活性化される。マルチセレクション回路320,330は、ディスターブ試験時には、マルチセレクション信号MSLa,MSLbに応答して、通常のデータ書込時よりも多い本数のライトディジット線WDLを並列に活性化する。

(もっと読む)

半導体記憶装置および半導体記憶装置の試験方法

【課題】ストレス試験の条件設定の自由度が大きく、様々な欠陥を検出可能な半導体記憶装置及び半導体記憶装置の試験方法を提供することである。

【解決手段】本発明にかかる半導体記憶装置は、行列状に配置された複数のメモリセル10と、メモリセルの行毎に対応して配線された複数のワード線WLと、メモリセル10の列毎に対応して配線された複数のビット線対BL、XBLと、テストモードの書き込み期間に、ワード線WLに第1の電圧を印加することでメモリセル10へデータを書き込み、書き込み期間の後のストレス印加期間に、ビット線対BL、XBLにプリチャージ電圧を印加すると共に、前記書き込み期間よりも長い時間、ワード線WLに任意の電圧値である第2の電圧を印加する制御回路と、を有する。

(もっと読む)

半導体記憶装置および半導体記憶装置の試験方法

【課題】ウェーハ状態の試験において、ライトマスク動作を実行するテスト回路を備えた半導体記憶装置を提供する。

【解決手段】メモリセルが接続されたビット線BLの信号を増幅するセンスアンプSAと、ビット線BLにYスイッチYS(カラムスイッチ)を介して接続されるローカル入出力線LIOの信号を増幅するサブアンプSUBと、ローカル入出力線LIOにライトスイッチWSを介して接続されるメイン入出力線MIOを書き込むべきデータ信号に基づき駆動するライトアンプ121Aと、テストモードとしてのデータ読出し動作において、センスアンプSAを活性化する一方、サブアンプSUBおよびライトアンプ121Aは共に非活性化し、さらにYスイッチYSおよびライトスイッチWSを共にオンとするテスト回路とを備える。

(もっと読む)

半導体試験装置

【課題】アドレスとフェイルデータの数がバースト長と一致しない場合またはフェイルデータに非対象データが混在した場合でも、フェイルデータをバーストアクセスを用いて収集メモリへ書き込むことが可能な半導体試験装置を実現する。

【解決手段】被試験対象デバイスが有するメモリのメモリセルに対応したアドレスとメモリセルの試験結果として得られたフェイルデータを並べ替えてバーストアクセスにより収集メモリに記憶させる半導体試験装置において、アドレスおよびフェイルデータがバーストアクセスの対象データであることを示すバースト対象信号を生成するアドレス発生部と、バースト対象信号に基づいてアドレスおよびフェイルデータをバーストアクセスに適した連続的なアドレスの順番に並べ替える並べ替え回路を備える。

(もっと読む)

半導体装置

【課題】半導体装置上の高速動作が可能な半導体記憶装置を実仕様周波数でも所望の動作を行うか確認する手段を提供する。

【解決手段】半導体記憶装置822と論理回路123とを有する半導体装置827において、半導体記憶装置822は2つのメモリアレイ領域802a,802bを備え、一方の出力をもう一方の入力として、かつ各々の読み出し書き込み制御が逆にできるようにして、半導体記憶装置822自体で検査できるようにする。

(もっと読む)

1 - 20 / 59

[ Back to top ]