Fターム[5L106FF07]の内容

半導体メモリの信頼性技術 (9,959) | 時期 (1,298) | 電源異常時 (5)

Fターム[5L106FF07]に分類される特許

1 - 5 / 5

不揮発性メモリにおける書き込み欠陥からのデータ保護

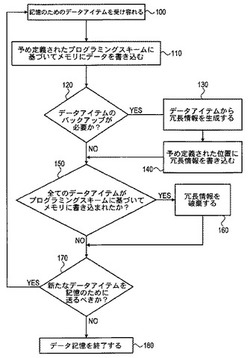

【課題】メモリ装置の書き込み欠陥からデータを保護するための方法及びシステムを提供する。

【解決手段】この方法は、データアイテムのセットにわたる冗長情報を計算し、データアイテムを、メモリに記憶するために送信することを含む。冗長情報は、データアイテムがメモリに首尾良く書き込まれるまでの間のみ保持され、次いで、破棄される。データアイテムは、それをメモリに書き込むのに欠陥が生じたとき、冗長情報を使用して回復される。

(もっと読む)

半導体集積回路テスト方法

【課題】複数のメモリを備えた半導体集積回路において、IRドロップによる誤動作を回避しつつ、効率の良いメモリテストを実現すること。

【解決手段】半導体集積回路に含まれる複数のメモリのそれぞれを単体でテストした場合に消費される電流を参照し、該複数のメモリから同時にテストすべき複数のメモリを被テストメモリとして選択する工程と、前記複数の被テストメモリを同時にテストした場合に消費される総消費電流をシミュレーションにより生成する工程と、前記総消費電流および前記半導体集積回路のレイアウト情報に基づいて、前記半導体集積回路におけるIRドロップを算出する工程と、算出した電圧降下が所定の許容値以内であるか否かを判定する工程と、前記電圧降下が前記所定の許容値を超えた場合には、前記複数のメモリから同時にテストすべきメモリを再度選択し直す工程と、を含む。

(もっと読む)

書き込み制御回路及び半導体装置

【課題】電気的に1回限りの書き込みが行われる記憶素子への誤書き込みを抑制する。

【解決手段】電圧検出部12は、電気的に1回限りの書き込みが行われる記憶素子(電気ヒューズ素子2)へ供給される書き込み電圧を検出し、書き込み電圧が所定の閾値電圧以上となると、書き込み制御部11に、書き込み信号に係わらず電気ヒューズ素子2への書き込みを停止させることで、書き込み電圧に異常が発生し、過電圧になることによる誤書き込みを抑制できる。

(もっと読む)

ドライバ

【課題】ドライバ全体の回路規模を低減すること。

【解決手段】本発明のドライバ(1)は、第1メモリ(10)と、アドレス制御回路(20)と、表示駆動回路(30)と、第2メモリ(60)とを具備している。第1メモリ(10)は、複数のメモリセル(11)と冗長メモリセル(12)とを含んでいる。アドレス制御回路(20)は、不良メモリセルを表す不良アドレス情報(W2)に基づいて、複数のメモリセル(11)のうちの不良メモリセルを冗長メモリセル(12)に置き換える。表示駆動回路(30)は、表示パネル(100)の表示品位を特定する表示品位特定情報(W1)に基づいて、第1メモリ(10)に格納される表示データ(DL)を表示パネル(100)に表示する。第2メモリ(60)には、上記の表示品位特定情報(W1)と上記の不良アドレス情報(W2)とが記録されている。

(もっと読む)

不揮発性記憶装置及びその書き込み判定方法

【課題】物理ページへの書き込み開始直後の電源遮断後に誤り訂正を行った後のデータは物理ページの消去済みではないにもかかわらず、全消去済と同じになり、正常に書き込みが行われた状態と誤判定するという課題がある。

【解決手段】不揮発性メモリにデータを書き込むときに必ず書き込みマークも同時に書き込む。単位ブロックに含まれる複数の書き込み単位毎に情報を読み出し、誤り訂正機能で読み出した情報の誤り訂正を行う。そして読み出した書き込みマークの情報を基にして書き込み単位毎の書き込み状態を判定する。

(もっと読む)

1 - 5 / 5

[ Back to top ]