Fターム[5M024AA05]の内容

Fターム[5M024AA05]に分類される特許

1 - 19 / 19

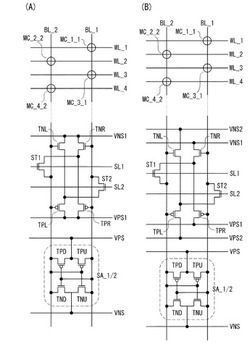

半導体装置及び半導体装置の動作方法

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは微細化と共にデータの読み出しエラーが発生しやすくなる。

【解決手段】第1のビット線BL_1の微弱な電位の変動はNチャネル型トランジスタTNRとPチャネル型トランジスタTPRで構成される第1のインバータで反転され、第1のスイッチである第1の選択トランジスタST1を介して、第2のビット線BL_2に出力される。第2のビット線BL_2の電位は、第1のビット線BL_1の電位とは反転した電位であるため、第1のビット線BL_1と第2のビット線BL_2の電位差は拡大する。この拡大した電位差を公知のセンスアンプSA_1/2あるいは、第2のインバータ(Nチャネル型トランジスタTNLとPチャネル型トランジスタTPLで構成される)と第1のインバータで構成されるフリップフロップ回路等で増幅する。

(もっと読む)

半導体装置

【課題】供給先回路の電流消費量によらず、内部電圧を短時間で安定化させる。

【解決手段】半導体装置10は、外部電位VDDを降圧することによって内部電圧VPERDを生成し、電源配線L1へ供給するVPERD生成回路2aと、接地電圧が供給される接地配線と電源配線L1との間に接続されたスイッチ52と、スイッチ52の開閉制御を行うワンショット信号生成部51とを備え、ワンショット信号生成部51は、VPERD生成回路2aによる内部電圧VPERDの開始と同期してスイッチ52を導通させる。

(もっと読む)

電圧発生装置

【課題】低電源電圧状態で、ビットラインプリチャージ電圧又はセルプレート電圧を安定的に駆動し、待機電流IDD2P及び動作電流を最小化すること。

【解決手段】電源電圧のハーフレベルの基準電圧を利用し、異なるレベルのバイアス信号を生成するバイアス信号生成手段と、出力端の電圧レベルに応答してプルダウン駆動信号を生成する駆動信号生成手段と、駆動信号に応答して出力端を駆動する電圧駆動手段と、出力端の電圧レベルに応じてプルアップ駆動信号/プルダウン駆動信号を生成する駆動信号生成手段と、前記プルアップ駆動信号/プルダウン駆動信号に応答して前記出力端をプルアップ駆動/プルダウン駆動するプルアップPMOSトランジスタ/プルダウンNMOSトランジスタと、第1多重化手段と、第2多重化手段とを備える半導体メモリ素子の電圧発生装置。

(もっと読む)

半導体装置、データ伝送システム、及び半導体装置の制御方法

【課題】小振幅信号を高速に増幅して出力し、かつ、消費電力の少ないアンプを備える半導体装置を提供する。

【解決手段】クロックに同期してデータが更新される小振幅信号を受信するアンプ部と、アンプ部の出力に接続された出力部と、を備え、アンプ部はクロックに同期して小振幅信号の論理レベルが遷移しうるタイミングで電流源の電流を増加し、遷移しないタイミングで電流を減少する。出力部はクロックに同期してアンプ部の出力データの論理レベルが遷移しうるタイミングで出力インピーダンスを低下させて高速に負荷を駆動すると共に、論理レベルが遷移しないタイミングで出力インピーダンスを増加させて貫通電流が流れることを防ぐ。

(もっと読む)

電流消耗を減らす構造を有する半導体装置及びそのターミネーション方法

【課題】電流消耗を減らすオン・ダイ・ターミネーション(ODT)構造を有する半導体装置及びそのターミネーション方法を提供する。

【解決手段】基準電圧と外部抵抗とが連結されたキャリブレーション端子の電圧に応答してキャリブレーションコードを発生させるキャリブレーション回路と、キャリブレーションコードとODT制御信号とに応答して、データ入出力パッドのターミネーション抵抗値を制御するODT装置と、を備え、データ入出力パッドのターミネーション抵抗値は、キャリブレーション端子の抵抗値より大きい半導体装置である。

(もっと読む)

半導体装置及びこれを備える情報処理システム

【課題】貫通電極に接続されているすべての双方向バッファ回路の出力バッファがハイインピーダンスとなった場合でも、貫通電極が論理不定状態となることを防止する。

【解決手段】半導体装置10は、積層された複数のコアチップCC0〜CC7及びインターフェースチップIFとを備えている。複数のコアチップCC0〜CC7及びインターフェースチップIFの各々は、半導体基板を貫通する複数の貫通電極TSV1と、貫通電極TSV1を駆動する双方向バッファ回路BUとを含み、インターフェースチップIFは、貫通電極TSV1の論理レベルを保持する論理レベル保持回路26をさらに含んでいる。双方向バッファ回路BUは、入力バッファIB及び出力バッファOBを含み、論理レベル保持回路26の第1のインバータINV1の駆動能力は、双方向バッファ回路BUの出力バッファOBの駆動能力よりも小さい。

(もっと読む)

入力バッファ回路

【課題】貫通電流の量を低減し、応答速度の低下を抑制する。

【解決手段】差動入力回路と、電源VDDと差動入力回路の一方の電源との間を接続し、差動入力回路の動作状態と非動作状態とを切り替え可能とするPMOSトランジスタ20と、PMOSトランジスタ20に並列に接続され、ゲートに差動入力回路の出力信号を入力するPMOSトランジスタ14と、を備える。PMOSトランジスタ20のサイズは、PMOSトランジスタ14のサイズよりも小さい。接地と差動入力回路の他方の電源との間を接続し、差動入力回路の動作状態と非動作状態とを切り替え可能とするNMOSトランジスタ19と、NMOSトランジスタ19に並列に接続され、ゲートに差動入力回路の出力信号を入力するNMOSトランジスタ13と、をさらに備える。NMOSトランジスタ19のサイズは、NMOSトランジスタ13のサイズよりも小さい。

(もっと読む)

半導体集積回路

【課題】従来の半導体集積回路は、データの送信を精度良く行うことができないという問題があった。

【解決手段】本発明にかかる半導体集積回路は、複数の信号線を介してパラレルに送信データを送信するSoC回路100と、送信データを受信するSDRAM回路101と、を備える。SoC回路100は、各信号線に対して設けられ、送信データを出力するためのデータ送信モードと、出力をハイインピーダンスにするためのハイインピーダンスモードと、が切り替わる複数のデータ出力回路203と、データ出力回路203に対して、送信データと予め設定された固定データとのいずれかを選択して出力するデータ選択回路256と、各データ出力回路203において、ハイインピーダンスモードからデータ送信モードへモードが切り替わってから実際に送信データの出力を開始するまでの間、固定データを出力するように制御する制御回路205と、を備える。

(もっと読む)

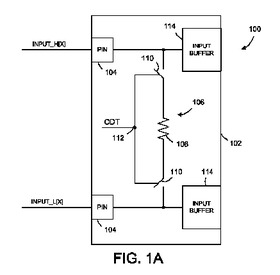

差動式オンライン終端

メモリデバイス及びシステムには、信号線に対するオンチップ終端が組み込まれている。メモリデバイスは、集積回路チップを備える。該集積回路チップは、1対の入力信号を提供する1対の入力信号ピンと、該入力信号ピンの対間に結合されるオンチップ終端回路とを備える。該オンチップ終端回路は、前記1対の入力信号を差動式に終端する。  (もっと読む)

(もっと読む)

半導体メモリデバイス

【課題】読み出しおよび書き込み動作の高速化と、低消費電力化を図る。

【解決手段】メモリセルアレイ1と、読み出しビット線RBLと、書き込みビット線WBLと、読み出しビット線RBLの電圧をセンスするセンスアンプSAと、センスアンプに接続されている第1および第2センス線(センス線対RBL_SA,WBL_SA)と、RBLセンス線RBL_SAと読み出しビット線RBLとの電気的な接続と非接続を制御する読み出しビット線スイッチ(BLスイッチ80(i))と、WBLセンス線WBL_SAと書き込みビット線WBL間に接続され、両者の電気的な接続と非接続を制御可能な書き込みバッファWBUFとを有する。

(もっと読む)

半導体メモリデバイスとその動作方法

【課題】読み出しおよび書き込み動作の高速化と低消費電力化を図る。

【解決手段】メモリセルアレイ1と、メモリセルMCaのデータ出力ノードに接続され、一方向に並ぶ複数セルで共有されている読み出しビット線RBLと、メモリセルMCaのデータ入力ノードに接続されて同様に共有されている書き込みビット線WBLと、当該ビット線対の電圧をセンスするセンスアンプSAと、センスアンプSAの一方入力に接続されている第1センス線(RBLセンス線RBL_SA)と、他方入力に接続されている第2センス線(WBLセンス線WBL_SA)と、第1センス線と読み出しビット線RBLとの電気的な接続と非接続を制御する第1ビット線スイッチ(BLスイッチ8ir)と、第2センス線と書き込みビット線WBLとの電気的な接続と非接続を制御する第2ビット線スイッチ(BLスイッチ8iw)とを有する。

(もっと読む)

電圧発生装置

【課題】待機動作又はセルフリフレッシュ動作、及びアクティブ動作の際に最終ドライブ端を制御するトランジスタを選択的に駆動して待機電流を低減させ、アクティブの際の応答時間を短縮し、駆動能力を向上させることができるようにすること。

【解決手段】本発明の電圧発生装置は、電源電圧を利用してプルアップ駆動信号及びプルダウン駆動信号を発生するコア電圧制御手段と、前記プルアップ駆動信号及びプルダウン駆動信号に応じて内部電圧を生成する出力駆動部と、バンクアクティブ信号に応じて前記コア電圧制御手段の駆動力を制御するアクティブ制御部とを備える。

(もっと読む)

電圧発生装置

【課題】ドライバー端にしきい電圧の低いPMOSトランジスタとNMOSトランジスタとを用いて、最終端の電圧駆動手段のターンオン/ターンオフ動作時間が同じになるように制御し、低電源電圧状態で、ビットラインプリチャージ電圧又はセルプレート電圧を安定的に駆動し、待機電流IDD2P及び動作電流を最小化すること。

【解決手段】本発明では、電源電圧のハーフレベルの基準電圧を利用し、異なるレベルのバイアス信号を生成するバイアス信号生成手段と、出力端の電圧レベルに応答してプルダウン駆動信号を生成する駆動信号生成手段と、駆動信号に応答して出力端を駆動する電圧駆動手段と、出力端の電圧レベルに応じてプルアップ駆動信号を非アクティブ/非アクティブにさせる補助駆動制御手段とを備える半導体メモリ素子の電圧発生装置。

(もっと読む)

半導体集積回路装置の駆動方法

【課題】供給能力が比較的低い昇圧電位生成回路の電荷供給量が削減された半導体集積回路装置の駆動方法を実現できるようにする。

【解決手段】半導体集積回路装置の駆動方法は、メインワード線及び複数のサブワード線と、複数のビット線と、メモリセルアレイと、センスアンプ列と、メインワード線駆動信号生成回路と、サブワード線駆動信号生成回路と、サブワード線非選択信号生成回路と、サブワード線駆動部とを備えた半導体集積回路装置の駆動方法であって、選択されていたサブワード線駆動回路が非選択に変化する際には、サブワード線が非選択になった後メインワード線駆動信号を非選択にする。

(もっと読む)

パワーオン・オフリセット回路及び半導体装置

【課題】動作中のシーケンスを正常に終了させるパワーオン・オフリセット回路を提供すること。

【解決手段】本発明は、電圧検号VD知信T21を出力する電圧検知回路43と、基準クロックCLKを出力する基準クロック発生回路47と、電圧検号VD知信T21と制御信号CLKから制御信号CEを出力する制御信号CE発生回路48と、制御信号CEから内部制御信号ICEを出力する内部制御信号ICE発生回路49からなり、電圧検知信号VDT21で検知される電圧以下のときに新たな動作シーケンスを禁止するとともに、すでに動作しているシーケンスは最後まで動作するものである。

(もっと読む)

半導体メモリ装置

【課題】オン/オフ制御が可能なローカルセンス増幅回路を備える半導体メモリ装置を提供する。

【解決手段】半導体メモリ装置は、複数のメモリセルアレイブロック、ビットラインセンス増幅回路、ローカルセンス増幅回路、データセンス増幅回路及び制御部を備える。制御部は第1信号及び第2信号に応答してローカルセンス制御信号を一定の時間だけ活性化させる。第1信号はビットラインセンス増幅回路を活性化させるビットラインセンスイネーブル信号であり、ローカルセンス増幅回路はビットラインセンスイネーブル信号が活性化された後に一定の時間だけ活性化される。第2信号はビットライン対と前記ローカル入出力ライン対とを連結するカラム選択ライン信号と同時に活性化または非活性化される。

(もっと読む)

不良検出回路および半導体記憶装置

【課題】 半導体記憶装置においてアレイ面積を増大させることなくアレイ内の短絡不良を検出して分離する。

【解決手段】 複数のメモリセルを有するメモリマット(MM)内において、不良列救済単位(RBU)ごとにローカルプリチャージ電圧伝達線(13u,13l)を配設する。各ローカルプリチャージ電圧伝達線に対して短絡検出回路(20)を設ける。短絡検出回路は、電源投入時に対応のローカルプリチャージ電圧伝達線の電圧レベルを検出し、その検出結果に従ってメインプリチャージ電圧伝達線(15u、15l)と対応のローカルプリチャージ電圧伝達線と接続または分離する。

(もっと読む)

半導体装置及び半導体チップ

【課題】

DDR-SDRAM などの入出力同期信号DQSを持つ半導体チップを複数個用い、DQS信号を共通接続して用いる場合において、各DQS信号が出力する時、その出力遅延時間のばらつきにより、共通接続したDQSを介して電源/グランド間に貫通電流が流れることを防止しなければならない。

【解決手段】

チップ単体のDQSにその出力信号を常にハイインピーダンスとする、オプション機能(ボンディングオプションチップ・ヒューズオプション等)を組み込み、複数個のチップのDQS信号を共通接続したとき、前記接続した中の1つのチップのみが正常にDQSを出力し残りはオプションを利用してDQSをハイインピーダンスにすることにより、DQSを介して電源/グランド間に貫通電流が流れることを避ける

(もっと読む)

1 - 19 / 19

[ Back to top ]