Fターム[5M024AA07]の内容

Fターム[5M024AA07]に分類される特許

1 - 20 / 33

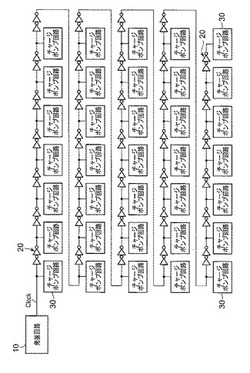

昇圧回路及びその給電方法

【課題】簡略化された回路構成でノイズ低減効果を持つ多相駆動型の昇圧回路を実現する。

【解決手段】昇圧回路は、所定周期のクロック信号を出力する発振回路と、前記クロック信号の1本の配線に直列接続され、トータル遅延時間が前記所定周期よりも長い複数の遅延回路と、前記複数の遅延回路に対応して前記1本の配線に接続された複数の分割昇圧回路と、を含む。

(もっと読む)

メモリ制御装置

【課題】メモリ書き込み時の消費電力を削減できるメモリ制御装置を提供する。

【解決手段】メモリ制御装置は、データバスを介してメモリ装置にデータをバースト転送するデータ出力バッファ回路390と、データのうちのメモリ装置内のメモリセルへの書き込みを禁止するデータを示すマスク信号をメモリ装置に出力するマスク信号出力バッファ回路190とを具備し、データ出力バッファ回路390は、マスク信号が書き込み禁止を示すときに出力ノードをハイインピーダンスにする。

(もっと読む)

半導体装置

【課題】直前の書き込みデータと同じ書き込みデータを連続して書き込む場合であれば、入出力線対のイコライズは不要である。そのため、直前の書き込みデータと同じ書き込みデータを連続して書き込む場合に、入出力線のイコライズを実施せず、データ書き込み時の消費電力を削減する半導体装置が、望まれる。

【解決手段】半導体装置は、第1の信号入出力線をイコライズする第1のイコライズ回路と、データのライト動作が連続する場合には、連続するライト動作間、第1のイコライズ回路を非活性とし、リード動作が連続する場合又はライト動作の後にリード動作を行う場合には、連続するライト動作間又はライト動作の後のリード動作間時に、第1のイコライズ回路を活性とする制御回路と、を備えている。

(もっと読む)

フロントエンドプリチャージを有するメモリ

【課題】デジタルメモリデバイスの動作電力を低減する。

【解決手段】複数のメモリセル(713)を含むデジタルメモリデバイス(2904)は、一組のメモリセル(713)上で動作を実行するようにコマンドを受信し、一組のメモリセル(713)は、デバイス(2904)全体よりも含有するメモリセルが少なく、デバイス(2904)は、受信コマンドに応答して、一組のメモリセル(713)に関連する一組のビットライン(709)のみを、動作のフロントエンドに選択的にプリチャージすることを含む動作を実行する、デジタルメモリ(2904)を動作させる方法、装置、およびシステム(2900)。

(もっと読む)

半導体装置

【課題】信号転送ラインの充放電によって消費される電力を低減する。

【解決手段】フリップフロップ構成のアンプ回路AMPを含むレシーバ回路R0kと、データバスDBとレシーバ回路R0kの入力端T2との間に挿入され、データバスDBがVPERI−NVthに達するとオフするトランジスタM7を備える。本発明によれば、トランジスタM7によって入力端T2の振幅が制限されることから、データバスDBがローレベルからハイレベルに変化する際の転送速度が向上する。しかも、アンプ回路AMPがフリップフロップ構成を有していることから、フリップフロップが反転した後は貫通電流が生じない。これにより、消費電力がより一層低減される。

(もっと読む)

半導体装置及び半導体装置を含む情報処理システム

【課題】センスアンプからデータ線への信号伝送時の振幅の増大に起因する動作電流の増加を防止し得る半導体装置を提供する。

【解決手段】本発明の半導体装置は、センスアンプ回路30、データ線LIO(T/B)、MIO(T/B)、リードアンプ回路31、スイッチ回路Q10、Q11、スイッチ回路Q14、Q15、スイッチ回路Q18、Q19、電荷転送トランジスタQ20、Q21、電位設定回路Q12、Q13、電位設定回路Q16、Q17を備えている。データ線LIOT、MIOTは、リードアンプ回路31の駆動電位である第1の電位より低い第2の電位に制御され、スイッチ回路Q14〜Q16のゲート電位は第1の電位に制御され、電荷転送トランジスタQ20、Q21のゲート電位(VTG)は、その閾値電圧に第2の電位を加えた固定電位に制御され、センスアンプ回路30からリードアンプ回路31に伝送される情報の増幅動作が行われる。

(もっと読む)

半導体装置

【課題】半導体装置の複数の伝送線の間で電荷を適切に再利用することで消費電流を削減可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、伝送線(GBL)、信号の論理を反転して出力する反転回路(IV)、伝送線と反転回路の入力側/出力側との間の接続をそれぞれ制御する第1・第2のスイッチ(Q1、Q2)、隣接する伝送線の間の接続を制御する第3のスイッチ(Q3)を備えて構成される。伝送線の信号が反転回路に保持された状態で、第1・第2のスイッチを非導通状態にして伝送線をフローティング状態とし、第3のスイッチを所定期間だけ導通状態として隣接伝送線をチャージシェアし好ましくは略同電位とした後、伝送線が反転回路及び第2のスイッチを介して反転駆動され、これにより隣接伝送線が逆論理の信号を反転駆動する場合、伝送線間で電荷を適切に再利用することにより消費電流を削減可能となる。

(もっと読む)

半導体装置及び半導体装置を含む情報処理システム

【課題】センスアンプからデータ線への信号伝送時の振幅の増大に起因する動作電流の増加を防止し得る半導体装置を提供する。

【解決手段】本発明の半導体装置は、センスアンプ回路20、第1のデータ線LIOT(B)、第2のデータ線MIOT(B)、第1の電位で駆動されるリードアンプ回路21、センスアンプ回路20と第1のデータ線との間の第1のスイッチ回路Q10、Q11、第1/第2の各データ線の間の第2のスイッチ回路Q14、Q15、第2のデータ線とリードアンプ回路21の間の接続を制御する第3のスイッチ回路Q18、Q19、第1のデータ線を第1の電位より低いVBLPに設定する第1の電位設定回路Q12、Q13、第2のデータ線をVBLPに設定する第2の電位設定回路Q16、Q17を備え、第2/第3のスイッチ回路の各々はトランジスタを含み、そのゲート電圧をVBLPに閾値電圧を加えた所定電圧に制御して導通状態になる。

(もっと読む)

半導体記憶装置

【課題】面積増大および消費電力の増大を招来することなく、データ読出しの高速化、安定化を図る半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、センスアンプ3がビット線対BL、BLBの電位の読み出しを開始するときのビット線の電位をレベルシフトさせるレベルシフト手段を備える。レベルシフト手段は、一方の電極が各ビット線に接続され、ビット線対ごとに二つで1対となるレベルシフト用キャパシタSFTCと、レベルシフト用キャパシタSFTCの他方の電極に共通に接続され、この他方の電極の共通ノードにシフト容量駆動信号SFTを与えて所定タイミングでレベルシフト用キャパシタSFTCの蓄電量を変化させるタイミングジェネレータ5と、を備える。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置内において、昇圧電源VPPから重負荷の信号線に流れる電流を低減し、昇圧電源VPPにおける電力消費を低減する。

【解決手段】センスアンプ回路21内のプリチャージ部22を制御するビット線プリチャージ信号BLEQBRの信号線と、シェアード部23を制御するシェアード信号SHRRの信号線との間にショート用トランジスタQ31を設ける。ビット線プリチャージ信号BLEQBRとシェアード信号SHRRとは、第1のレベルまたは第2のレベル、たとえば、“H”または“L”の論理レベルが逆方向に遷移する信号である。そして、ビット線プリチャージ信号BLEQBRとシェアード信号SHRRの信号遷移時に、所定時間、ショート用トランジスタQ31をON(導通)にする。これにより、ビット線プリチャージ信号BLEQBRの信号線とシェアード信号SHRRの信号線と間に短絡電流を流し、相互に電荷の再配分を行う。

(もっと読む)

半導体記憶装置及びその制御方法

【課題】アクセス速度の低下を最小限に抑制しつつ、プリデコード信号のリセットによる消費電力の増大を防止する。

【解決手段】ロウアドレスRADTをプリデコードすることによりプリデコード信号RFを生成するプリデコーダ100と、ロウアドレスRADTが不良アドレスであるか否かを判定する救済判定回路300と、救済判定回路300によりロウアドレスRADTが不良アドレスであると判定された場合に、救済アドレスRREDを生成する救済アドレスデコーダ400と、プリチャージコマンドの発行に応答して、プリデコード信号RFをリセットすることなく救済アドレスRREDをリセットする信号制御回路200とを備える。これにより、プリデコード信号RFのリセットによる消費電力の増大が防止される一方、ロウ系アクセスを律速する冗長パスについては高速なアクセスが担保される。

(もっと読む)

ワードライン駆動回路及び駆動方法

【課題】消費電流を低減できるワードライン駆動回路及び駆動方法を提供すること。

【解決手段】本発明に係るワードライン駆動回路は、ワードライン(WL)を活性化電圧(VPP)で駆動する第1駆動手段(410)と、前記ワードラインを非活性化電圧(VBBW)で駆動する第2駆動手段(420)と、前記ワードラインを前記活性化電圧と前記非活性化電圧との間の電圧(VSS)で駆動する第3駆動手段(430)と、を備える。

(もっと読む)

半導体集積回路および半導体記憶装置

【課題】チップの内部バスやチップ間を接続する外部バスにおける消費電力の低減や、データ転送速度の向上を実現する。

【解決手段】論理レベル‘H’か‘L’かその中間レベルとなる‘M’を採り得る複数本のバスDB[0]〜DB[n−1]と、データD[0]〜D[m−1]を符号化し、これに基づいて複数本のバスのそれぞれを論理レベル‘H’、‘L’、‘M’のいずれかに駆動する送信回路TXと、複数本のバスを互いにショートするバスイコライズ回路BEQを設ける。送信回路TXは、データの符号化を行う際に、論理レベル‘H’に駆動するバスの本数(k本)と論理レベル‘L’に駆動するバスの本数(k本)が同数となるような組み合わせを用いる。バスイコライズ回路BEQは、データが送信された後にショート動作を行うことで、各バスを論理レベル‘M’にプリチャージする。

(もっと読む)

データバス電力低減化半導体記憶装置

【課題】半導体記憶装置のデータ伝送時におけるデータバスのトグル動作よる消費電力を低減する。

【解決手段】DRFバス、DR11Fバス、GDRFバス、及びGDR11Fバスを含み、DRFバス及びDR11Fバス、並びにGDRFバス及びGDR11Fバスは、データ伝送時に実施されるデータバスのトグル動作の回数を減少させる目的で、並行して配置される。DR11Fバスは、データ伝送が従来システムで実施された場合に両側のDRFバスがトグル動作を実施させられる場合にのみ、DR11Fバスにトグル動作を実施させるように追加される。

(もっと読む)

半導体記憶装置

【課題】データバスの配線長を短縮するとともに、共通データバスと複数の単独データの間の伝送データを選択的にバッファリング可能な半導体記憶装置を提供する。

【解決手段】本発明の半導体記憶装置において、複数のバンク0〜7に分割され、かつ各々のバンクが2つの領域HBa、HBbに区分されたメモリセルアレイと、入出力回路部12に接続される共通データバスBS0と、各バンクの領域HBa、HBbのI/Oと接続される複数の単独データバスBS1、BS2、BS3、BS4と、共通データバスBS0と単独データバスBS1、BS2に接続された双方向バッファ10と、共通データバスBS0と単独データバスBS3、BS4に接続された双方向バッファ11を備えている。双方向バッファ10、11は、共通データバスBS0と単独データバスBS1〜BS4の中の選択された単独データバスとの間を双方向に伝送されるデータをバッファリングする。

(もっと読む)

複数のチャージポンプ回路を用いて昇圧された電圧を生成する装置および方法

本発明は、複数のチャージポンプ回路、チャージポンプ制御信号、およびアクティブなチャージポンプのアクティブな容量性エレメントを用いて、昇圧された電圧を生成するための装置および方法に関するものである。さらに、本発明は、活性化されたチャージポンプの容量性エレメントが、チャージポンプへの入力電圧およびチャージポンプ信号に応じて充電される、装置および方法、ならびにダイナミックランダムアクセスメモリを提供するものである。  (もっと読む)

(もっと読む)

同期式半導体装置及びこれを有するデータ処理システム

【課題】チップセレクト信号の非活性化に応答して、入力バッファの動作や内部クロックを停止させることなく消費電力を低減可能な同期式半導体装置を提供する。

【解決手段】入力バッファ110と、クロックCLKに基づいてラッチ信号CLK1を生成するラッチ信号生成回路120と、アドレス信号をラッチ信号CLK1に応答してラッチするラッチ回路130と、アドレス信号をラッチ信号CLK1に同期してラッチ回路130に供給するディレイ回路140と、入力バッファ110とディレイ回路140との間に設けられ、チップセレクト信号CSBの非活性化に応答してアドレス信号を非活性化させるNORゲート回路150とを備える。本発明によれば、入力バッファの動作や内部クロックを停止させることなく、入力バッファとラッチ回路との間で発生する消費電力を効果的に低減することが可能となる。

(もっと読む)

半導体記憶装置

【課題】メイン入出力線MIOとローカル入出力線LIOとの間に設けられたトランスファーゲートの消費電流、素子数および面積を低減する。

【解決手段】メモリマットを格子状に配置してなるメモリセルアレイにおいて、メモリマット間のクロスエリア領域に配置され、信号SBAENに応じて動作し、書き込み時にセンスアンプ60とメインアンプ20とを直接的に接続するトランスファーゲート(薄膜NMOSトランジスタ401、402)を有するサブアンプ10と、サブアンプ10のないクロスエリア領域に配置され、カラムアドレスデコーダから配線された信号線とロウアドレスデコーダから配線された信号線とを入力として、サブアンプ10に供給する信号SBAENを生成する論理回路を備えている。

(もっと読む)

半導体記憶装置の出力回路、および半導体記憶装置の出力回路のデータ出力方法

【課題】待機時の漏れ電流の抑制と動作時の低消費電流化をともに実現することができる、半導体記憶装置の出力回路を提供する。

【解決手段】PMOSトランジスタQ11とNMOSトランジスタQ21とが直列に接続されて構成され、メモリセルからの読み出しデータOUTHBを論理反転して、出力用PMOSトランジスタQ51のゲート信号を出力するインバータINV(1)を設ける。そして、待機時には、PMOSトランジスタQ81をONし、インバータINV(1)の回路電源として電源VDD(1.8V)を選択し、出力用PMOSトランジスタQ51のゲートレベルをVDDレベルに設定する。動作時には、NMOSトランジスタQ71をONし、電源VDDQ(1.2V)を選択し、PMOSトランジスタQ51のゲートレベルをVDDQレベルに設定する。

(もっと読む)

半導体装置

【課題】昇圧電源回路の消費電流を削減することにより、低消費電力化を実現する半導体記憶装置を提供する。

【解決手段】ドライバ制御回路22は、レベル変換回路21の出力端子であるノードn3の信号が入力される遅延回路24及びNOR回路25を有している。NOR回路25は、遅延回路24の遅延信号に従って、トランジスタT20を介してドライバ回路23の出力ノードn7を、接地電圧Vssから電源電圧VINTまでまず昇圧させる(第1段階)。続いて、遅延時間の経過後、トランジスタT19を導通させて、出力ノードn7の電圧を電源電圧VINTから昇圧電圧VPPまで昇圧させる(第2段階)。

(もっと読む)

1 - 20 / 33

[ Back to top ]